在三天前SpinalHDL1.8.0正式上線,在這次更新中增加了Scala代碼和生成的RTL代碼之間的對(duì)照功能,也就是說我們可以在生成的RTL代碼中看到是哪一行Scala生成的,這就為后續(xù)的代碼調(diào)試增加了靈活性(雖然在調(diào)試SpinalHDL的時(shí)候也很少看對(duì)應(yīng)的RTL吧)。

更新記錄可以從這個(gè)網(wǎng)址看到

https://github.com/SpinalHDL/SpinalHDL/pull/985

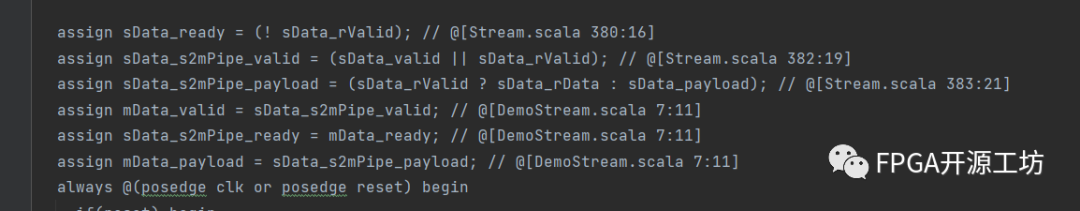

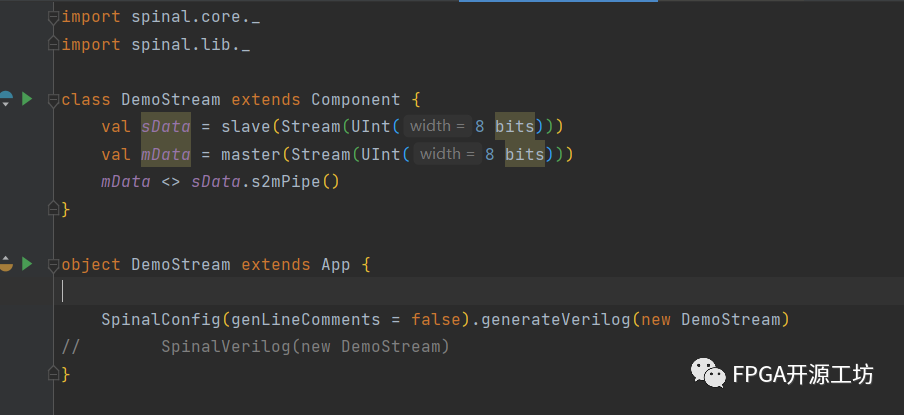

下圖是Stream的打拍,在它生成的Verilog里面可以清楚的看到是哪一行Scala代碼生成的。

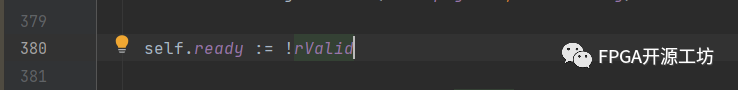

可以看到在生成的Verilog中標(biāo)記了原始的scala文件和對(duì)應(yīng)的代碼行數(shù),以sData_ready為例可以看到它是Stream.scala這個(gè)文件中第380行代碼生成的。也就是下面這一行代碼。

通過新更新的這個(gè)功能就能從生成的Verilog、VHDL等文件中追蹤原始的Scala文件。

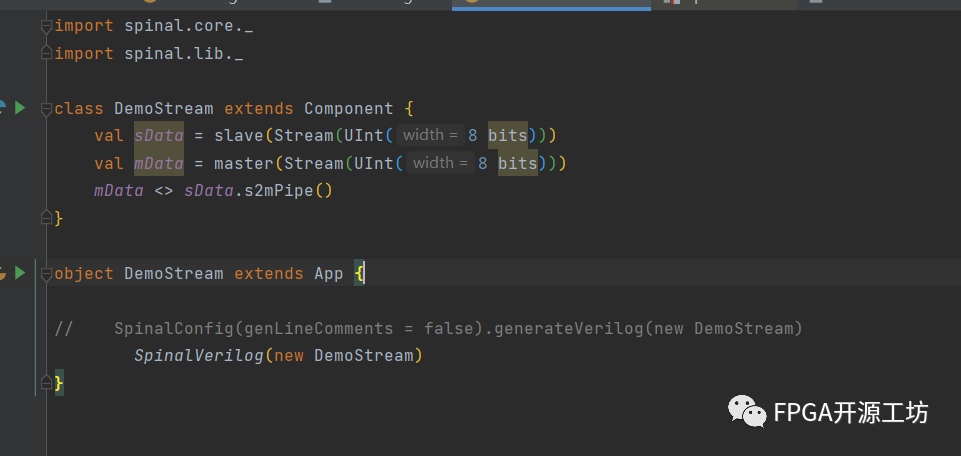

如果不想啟用這個(gè)功能可以在配置中將genLineComments設(shè)置為false,這樣就不會(huì)生成追蹤的代碼注釋了。使用方法如下。

import spinal.core._ import spinal.lib._ class DemoStream extends Component { val sData = slave(Stream(UInt(8 bits))) val mData = master(Stream(UInt(8 bits))) mData <> sData.s2mPipe() } object DemoStream extends App { SpinalConfig(genLineComments = false).generateVerilog(new DemoStream) // SpinalVerilog(new DemoStream) }

審核編輯:湯梓紅

-

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60593 -

代碼

+關(guān)注

關(guān)注

30文章

4886瀏覽量

70175 -

scala

+關(guān)注

關(guān)注

0文章

42瀏覽量

6613

原文標(biāo)題:從RTL追蹤到Scala

文章出處:【微信號(hào):FPGA開源工坊,微信公眾號(hào):FPGA開源工坊】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Scala入門到精通——第三十節(jié) Scala腳本編程與結(jié)束語

請(qǐng)問怎么提高JTAG調(diào)試追蹤到printf()?

spark scala maven創(chuàng)建工程與提交任務(wù)到yarn的步驟

SpinalHDL如何把名字從scala代碼傳遞到產(chǎn)生的硬件中

從ESL到RTL,低功耗設(shè)計(jì)再下一城

scala語言主要應(yīng)用領(lǐng)域詳解

一文看懂scala和java的區(qū)別

評(píng)論