USB是比較通用的,這里就寫USB2.0和3.0的通用設(shè)計規(guī)則,以及幾個實(shí)際中的注意事項。

1.由于USB是外部接口,考慮到用戶使用的各種復(fù)雜條件,防止有短路的情況影響到板卡自身的電源,所以需要設(shè)計限流IC。

這里使用的限流IC還是比較簡單的,首先根據(jù)負(fù)載確定限流IC芯片,USB2.0跟USB3.0跑的最大電流不一樣,限流的大小也不一樣,需要注意。

筆者以前做設(shè)計用過另外一種限流IC,保護(hù)時能輸出狀態(tài)IO,這個信號可以連接到板卡的SOC,或者MCU等,以進(jìn)行狀態(tài)檢測。

2.電容

因?yàn)閁SB設(shè)備拔插的時候,電壓會波動,尤其是插入的時候,需要較大的電流,需要在接口附近使用較大的電容,防止電壓被拉低。為了電源的干凈,也可以增加兩枚小電容。

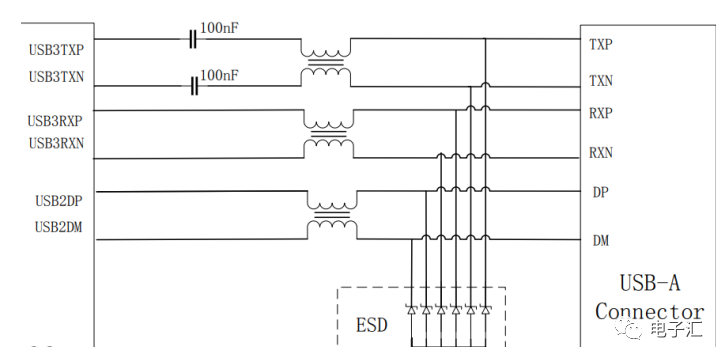

3. 信號線。USB信號走的是差分信號,為了保護(hù),需要在鏈路上增加TVS管,理論上每個元器件都有一定的容性,所以選用TVS管的時候,盡量選擇容性負(fù)載小一些的,對信號影響最小。保護(hù)電壓不必太大,考慮USB差分信號幅值大小來選型即可。考慮到PCB走線阻抗的連續(xù)性,TVS管在板卡的位置,距離USB座子不宜太遠(yuǎn)也不宜太近。太遠(yuǎn)不利于TVS,太近則會導(dǎo)致阻抗跌落。

二. USB2.0

以下為USB電路設(shè)計;

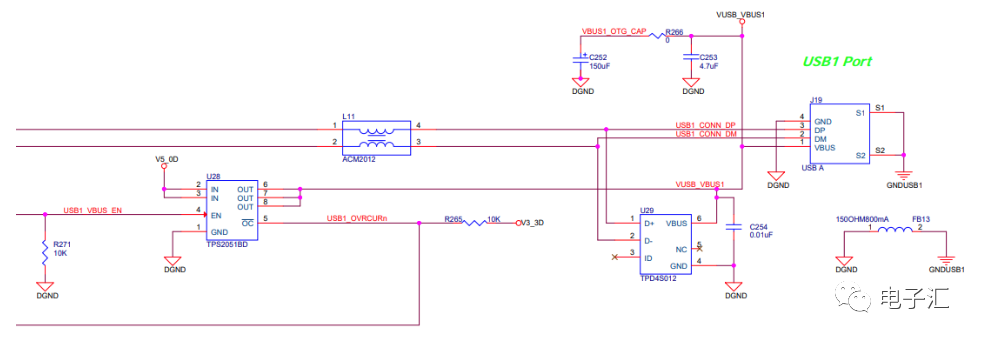

1)U28是過流保護(hù)器件,USB協(xié)議中規(guī)定USB端口供電5V,電流500mA,超過該值要能實(shí)現(xiàn)關(guān)斷輸出,另外在負(fù)載短路時也能實(shí)現(xiàn)關(guān)斷,所以使用該器件,該器件叫做負(fù)載開關(guān)芯片。

2)L11是共模電感,共模電流會導(dǎo)致EMC測試中的輻射測試超標(biāo),差分信號不平衡將會導(dǎo)致該情況發(fā)生,所以增加共模電感,來減小/阻礙共模電流。實(shí)際產(chǎn)品設(shè)計中,這個共模電感可以和兩顆0402的電阻做共-lay,然后根據(jù)實(shí)際測試的數(shù)據(jù)決定電感要不要上件。如果貼電阻的情況下,EMC的表現(xiàn)也很好,那么就不貼共模電感,只貼電阻就可以了,畢竟一個共模電感可以買好多個電阻了,成本差異很明顯。

3)U29是靜電防護(hù)器件,因?yàn)閁SB端口我們會使用手插入USB設(shè)備,可能導(dǎo)致電源、數(shù)據(jù)線上有靜電放電,用該器件來保護(hù)CPU端口。一般這個靜電防護(hù)器件要注意結(jié)電容,結(jié)電容和信號速率相關(guān)。USB信號上通常用的ESD器件的結(jié)電容在幾pF左右。同時,在PCB上,這個ESD器件不要有分叉走線,最好把ESD器件的焊盤直接放在USB信號線上。

4)Vbus上的電容,這是因?yàn)閁SB設(shè)備插入時瞬間電流較大,則可能導(dǎo)致Vbus電壓下降,此時需要滿足標(biāo)準(zhǔn)規(guī)定,所以增加電容來穩(wěn)定電壓。

5)FB13是信號地和外殼屏蔽地之間的隔離磁珠,磁珠是耗能原件,來消耗掉不需要的干擾高頻信號,直流下基本上沒作用。

6)J19是USB端子,可能是電腦那種的USB母頭,也可能是手機(jī)上的Micro USB接口。

7)在USB靠近端子側(cè)放置電阻是靜電防護(hù)作用,因?yàn)橛袝r候靜電防護(hù)器件還沒起作用,就要靠這個電阻起作用了。

三. USB3.0

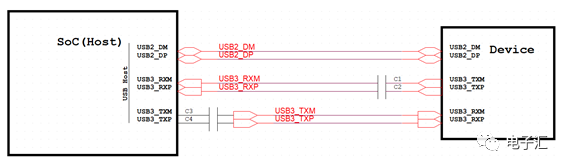

USB3.0相比2.0在硬件物理連接上有較大的改變,采用的是RX/TX全雙工鏈路設(shè)計,由2對差分信號組成,同時向下兼容USB2.0,所以整個接口有3對差分信號,分別為USB3_RXM/USB3_RXP,USB3_TXM/USB3_TXP,USB2_DM/USB2_DP,USB3.0的傳輸速率可達(dá)到5Gbps,相比USB2.0 480Mbps有比較大的提供。

硬件原理設(shè)計

如下圖,為USB3.0的Data數(shù)據(jù)連接原理圖,從電路上可以看是USB2.0為半雙工,數(shù)據(jù)收發(fā)在一對差分信號上傳輸。USB3.0為全雙工,收發(fā)信號為獨(dú)立的傳輸路徑;其次,由于Sink端的直流偏置電壓和source端的直流偏置電壓不一樣,故要需要串入AC耦合電容,電容一般取100nF,一般靠近驅(qū)動端放置,電容在設(shè)計上要求ESR ESL(特別重要)盡量小。

USB 3.0的Host的RX連接到Device Tx,Host的Tx連接到Device的 Rx,類似于我們常用的UART接口的連接。

PCB Layout設(shè)計

硬件連接上相對比較簡單,最終需要PCB Layout設(shè)計來保證信號的完整性,接下來從PCB層疊結(jié)構(gòu)、阻抗控制、走線要求等細(xì)節(jié)上說明USB3.0的設(shè)計的注意事項。

阻抗控制:90Ω差分阻抗±10%

AC耦合電容:100nF

USB2.0: 5V,500mA

USB3.0: 5V,1A

1. PCB層疊結(jié)構(gòu)要求

以下是4層板的層疊結(jié)構(gòu)圖,可通過Si9000計算出差分對所約束的線寬線距。

對于PCB阻抗線的定義,受那些物理參數(shù)影響,請自行查閱相關(guān)

2. USB差分阻抗控制要求

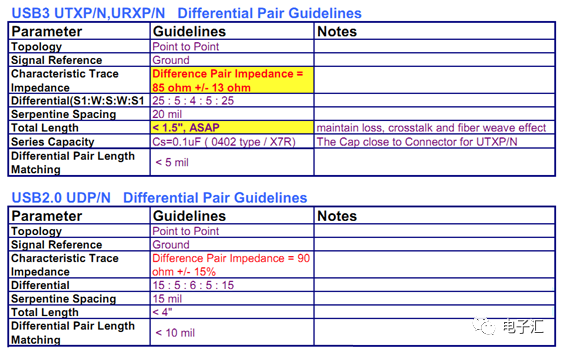

參考USB PHY手冊,基于上圖的層疊結(jié)構(gòu),計算出差分信號所要求的線寬線距,本文為ASM1153 為例進(jìn)行闡述:

ASM1153為USB 3.0轉(zhuǎn)Sata接口的橋芯片,要求USB 3.0的差分阻抗為85歐,USB2.0為90歐,差分對等長公差在+/-5mil。

3. PCB走線要求

5Gbps的速率需要以高速線的設(shè)計規(guī)則來嚴(yán)格把關(guān)走線,充分考慮PCB的設(shè)計細(xì)節(jié)

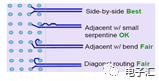

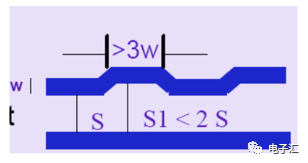

3.1 PCB出線要求盡可能平等出差,具體走線參考下圖:

3.2 走線換層需要在信號過孔旁邊增加地過孔,用于信號的回流(高速通用規(guī)則)

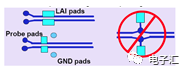

3.3 USB信號測試點(diǎn)的放置建議如下圖,“一”字形放置在路徑上,非Y字形或T字形放置,并且測試焊盤如果走線不連續(xù)的較大焊盤,請將相鄰層的GND層垂直于測試焊盤掏空,避免出現(xiàn)影響信號的寄生電容或等效電容。測試點(diǎn)的焊盤尺寸,應(yīng)盡可能的小,如果必需要放置測試點(diǎn)的話,比照0402封裝的焊盤尺寸或直接將測試點(diǎn)放置在信號線的過孔上。

3.4 關(guān)于等長匹配蛇形線的走線方式,建議按下圖方式走線

3.5 USB3.0 的P/M如果走線上有交差,可以將差分對的P/M交換,USB3允許P/M反轉(zhuǎn)

四. 注意事項

USB2.0信號線換層次數(shù)。

一般是要求換層2次,即從SoC扇出換層一次,到Device端或者連接器端換層一次。十幾種換3~4次也沒有問題,但最好每次換層都伴隨GND過孔,每個信號線一個,空間受限的話也可以兩個信號先共用一個。

USB3.0信號

USB3.0速率更高,這方面的要求會更嚴(yán)格一點(diǎn)。在實(shí)際項目中,也可以參考2.0的信號處理。

如果是核心板和底板的方式,那么用非高速的普通連接器問題也不大。

審核編輯:郭婷

-

芯片

+關(guān)注

關(guān)注

456文章

50892瀏覽量

424325 -

接口

+關(guān)注

關(guān)注

33文章

8617瀏覽量

151317 -

usb

+關(guān)注

關(guān)注

60文章

7952瀏覽量

264928

原文標(biāo)題:USB設(shè)計簡介

文章出處:【微信號:電子匯,微信公眾號:電子匯】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

TUSB8041是否支持將USB2.0通道的數(shù)據(jù)編碼到USB3.0通道去?

有沒有ASM3354 USB2.0口轉(zhuǎn)SATA的bridge?

使用USB接口的注意事項

CYUSB3014是否會自動調(diào)整工作模式USB3.0還是USB2.0?

CYUSB3304-68LTXI可識別2.0設(shè)備但不識別3.0設(shè)備,為什么?

Fcx3 usb2.0攝像頭分辨率問題求解

矽力杰USB2.0接口ESD保護(hù)方案

USB2.0和3.0的通用設(shè)計規(guī)則和注意事項

USB2.0和3.0的通用設(shè)計規(guī)則和注意事項

評論