異步fifo詳解

一. 什么是異步FIFO

FIFO即First in First out的英文簡稱,是一種先進先出的數據緩存器,與普通存儲器的區別在于沒有外部讀寫的地址線,缺點是只能順序的讀取和寫入數據(對于大型數據存儲,在性能上必然緩慢),其數據地址是由內部讀寫指針自動加一完成的,不能像普通的存儲器一樣,由地址線決定讀取或者寫入某個特定地址的數據,按讀寫是否為相同時鐘域分為同步和異步FIFO,這里主要介紹異步FIFO,主要用于跨時鐘域傳輸數據。

FIFO是一種數據緩沖器,用來實現數據先入先出的讀/寫方式。FIFO有一個寫端口和一個讀端口,外部無需使用者控制地址,使用方便。FIFO與普通的Block RAM有一個很明顯的區別就是使用Block RAM來做數據緩存處理,使用者必須自己控制讀和寫地址的管理,必須保證寫的數據不把Block RAM中未被讀出的內容覆蓋掉從而造成數據錯誤,同時保證讀的時候要讀出未被寫入的地址。而采用FIFO時,只需要關注FIFO控制器給出的空滿狀態信號即可知道當前有沒有錯誤的操作了FIFO,使FIFO的數據寫溢出或讀空。

異步FIFO讀寫分別采用相互異步的不同時鐘,使用異步FIFO可以在兩個不同時鐘系統之間快速而方便地傳輸實時數據

FIFO的常見參數

FIFO的寬度:即FIFO一次讀寫操作的數據位;

FIFO的深度:指的是FIFO可以存儲多少個N位的數據(如果寬度為N)。

滿標志:FIFO已滿或將要滿時由FIFO的狀態電路送出的一個信號,以阻止FIFO的寫操作繼續向FIFO中寫數據而造成溢出(overflow)。

空標志:FIFO已空或將要空時由FIFO的狀態電路送出的一個信號,以阻止FIFO的讀操作繼續從FIFO中讀出數據而造成無效數據的讀出(underflow)。

讀時鐘:讀操作所遵循的時鐘,在每個時鐘沿來臨時讀數據。

寫時鐘:寫操作所遵循的時鐘,在每個時鐘沿來臨時寫數據。

二、設計原理

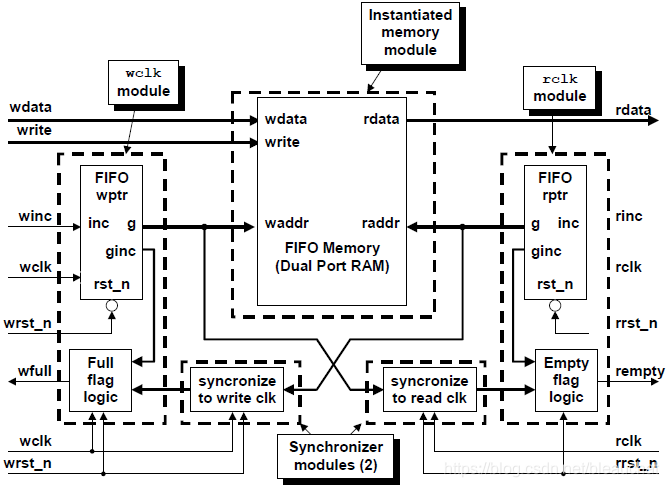

2.1結構框圖

如上圖所示的同步模塊synchronize to write clk,其作用是把讀時鐘域的讀指針rd_ptr采集到寫時鐘(wr_clk)域,然后和寫指針wr_ptr進行比較從而產生或撤消寫滿標志位wr_full;類似地,同步模塊synchronize to read clk的作用是把寫時鐘域的寫指針wr_ptr采集到讀時鐘域,然后和讀指針rd_ptr進行比較從而產生或撤消讀空標志位rd_empty。

另外還有寫指針wr_ptr和寫滿標志位wr_full產生模塊,讀指針rd_ptr和讀空標志位rd_empty產生模塊,以及雙端口存儲RAM模塊。

2.2 二進制計數器存在的問題

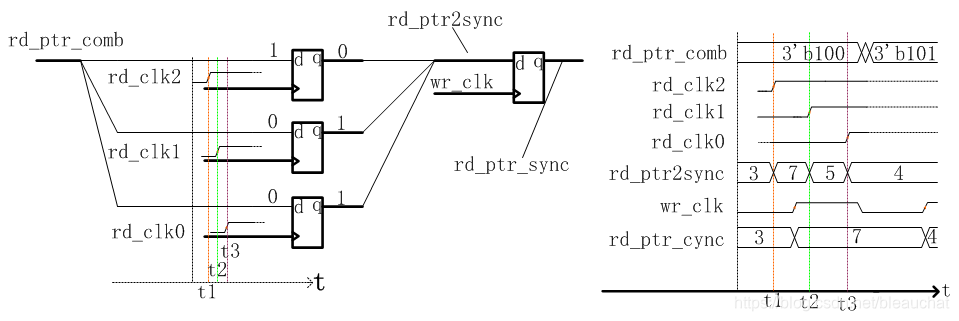

異步FIFO讀寫指針需要在數學上的操作和比較才能產生準確的空滿標志位,但由于讀寫指針屬于不同的時鐘域及讀寫時鐘相位關系的不確定性,同步模塊采集另一時鐘域的指針時,此指針有可能正處在跳變的過程中,如下圖所示,那么采集到的值很有可能是不期望的值,當然,不期望的錯誤結果也會隨之發生。

上圖中,rd_ptr2sync 3和4以及4和5之間的中間態是由于到各寄存器的時鐘rd_clk存在偏差而引起的。二進制的遞增操作,在大多數情況下都會有兩位或者兩以上的bit位在同一個遞增操作內發生變化,但由于實際電路中會存在時鐘偏差和不同的路徑延時,二進制計數器在自增時會不可避免地產生錯誤的中間結果,如下圖。

由于rd_clk上升沿到達三寄存器的時間各不相同,這就導致了rd_ptr2sync的值從3’b011跳變3’b100的過程中經歷了3’b111和3’b101,直到最后一個時鐘(rd_clk0)沿的到來后rd_ptr2sync才跳變到正確結果3’b100。中間結果的持續的時間雖然相對短暫,但是這些不正確的中間結果完全有可能被其它時鐘域的同步模塊采集到而產生錯誤的動作,見上圖。

由此可見,要避免中間結果的產生,其中一個可行的方案就是使被同步模塊采集的數據遞變時,每次只有一個bit位發生改變。格雷碼計數器就是一個不錯的選擇。

-

fifo

+關注

關注

3文章

387瀏覽量

43648

發布評論請先 登錄

相關推薦

FIFO Generator的Xilinx官方手冊

Efinity FIFO IP仿真問題 -v1

異步永磁電機工作原理 永磁電機有異步的嗎

同步FIFO和異步FIFO區別介紹

DMA產生FIFO error interrupt錯誤的原因?

cy7c68013a slave fifo寫數據出現異常的原因有哪些?如何解決?

如何清除SPI通信中的TX_FIFO和RX_FIFO?

同步級聯和異步級聯的區別 異步級聯和同步級聯分別要注意什么

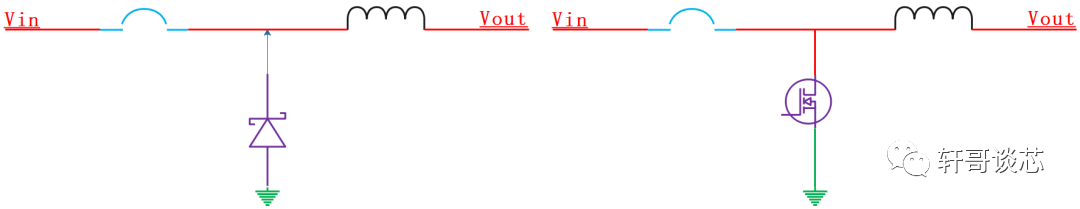

異步整流是什么 異步整流優點介紹

異步電機應用類型有哪些?該如何分類?

異步fifo詳解

異步fifo詳解

評論