為改善超大尺寸芯片封裝的內應力,研究了使用導電膠粘接的超大尺寸芯片的陶瓷封裝結構,建立了簡化的結構模型。模型從上到下依次為硅芯片、導電膠和陶瓷基板三層結構。利用有限元分析方法,研究了導電膠的粘接層厚度、彈性模量、熱膨脹系數和固化溫度對芯片封裝內應力的影響。

結果表明,粘接層所受的應力主要集中在導電膠和芯片粘接界面邊緣處,且粘接層四個角所受的應力最大,故在貼片工藝中要保證導電膠在芯片四個角的溢出,防止芯片脫落。適當增加導電膠的粘接層厚度,選取低彈性模量和低熱膨脹系數的導電膠,以及采較低的固化溫度可大幅度降低器件的內應力,提高芯片剪切力。

引言

隨著微電子技術的不斷創新和發展,大規模集成電路的集成度和工藝水平不斷提高,系統級芯片的設計能力和技術也得到了很大的提高。系統級芯片可將微處理器、模擬IP核、數字IP核和存儲器集成在一起,大幅提高器件的集成度,但芯片也面臨晶粒尺寸過大的挑戰,尤其當芯片使用超低k電介質材料時,晶粒變得更脆、更易碎。

由于陶瓷基板、芯片和導電膠之間的線性熱膨脹系數的差異,超大尺寸芯片粘接面存在的大應力會使器件在后續使用中存在重大的質量隱患。粘接面應力過大,易使粘接面邊緣出現開裂,嚴重時會使芯片脫落;應力過大會損傷芯片,影響器件電性能。

近年來我國在芯片封裝內應力方面進行了深入的研究。連興峰等人運用COMSOL Multiphysics軟件分析了由封裝引起的熱失配對1mm x 1mm芯片的封裝內應力的影響,發現芯片所受應力會隨著基板厚度的增加而增加。李明等人利用數字散斑相關方法對COB封裝在熱載荷下的表面熱變形分布進行實驗測量,并比較了不同封裝結構對內應力的影響,認為陶瓷基板上的封裝方案比FR4上的封裝方案的熱失配小,封裝內應力也較小,適用于應力敏感的封裝系統。

梁穎等人對微光機電系統芯片粘接層進行了溫度循環應力與應變有限元分析,發現無溢出結構的粘接層內的應力與應變大于有溢出結構的粘接層內的,有溢出結構的粘接層在溫度循環條件下可以在一定程度上降低粘接層內的最大應力與應變。張淑芳等人對LED小芯片封裝中所受內應力與應變進行了模擬仿真與分析,發現芯片封裝的內應力集中在導電膠和芯片粘接界面邊緣處。

目前國內針對芯片封裝內應力方面的研究主要集中在小尺寸芯片上,而對超大尺寸芯片封裝,其封裝內應力與導電膠的性能參數、粘接層厚度和固化溫度的關系研究較少。本文利用有限元分析方法,采用簡化的結構模型,分析了這些變量對芯片內應力的影響,從而為超大尺寸芯片的封裝設計提供參考依據。

1 超大尺寸芯片封裝內應力仿真模型

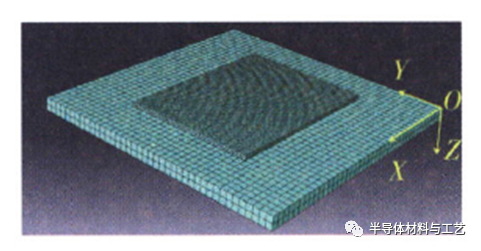

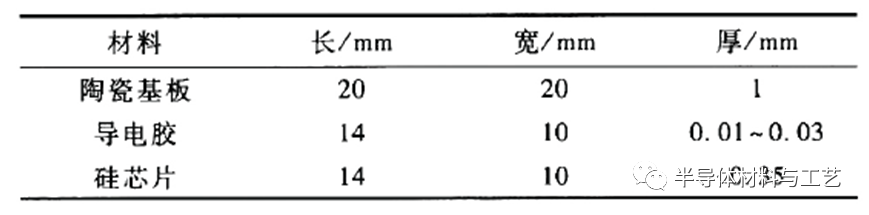

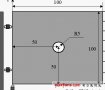

將使用導電膠粘接的超大尺寸芯片的陶瓷封裝結構作為研究對象,封裝模型從上到下依次為硅芯片、導電膠粘結層和陶瓷基板三層結構,簡化后模型的有限元網格劃分如圖1所示,模型尺寸參數和模型中材料的性能參數分別如表1和表2所示。為提高計算效率,對分析模型進行簡化處理:①芯片與陶瓷基板之間的粘接層無空洞等缺陷;②模型溫度發生變化時,模型整體溫度分布均勻;③不考慮導電膠溢出情況,導電膠尺寸與芯片尺寸一致。

圖1 有限元分析模型

表1 模型尺寸參數

表2 模型中材料性能參數

2 仿真分析及驗證

由于不同導電膠的性能參數差異較大,其應用環境也不一樣。本文分析了導電膠的粘接層厚度、彈性模量、熱膨脹系數和固化溫度對超大尺寸芯片粘接內應力的影響并進行了試驗驗證。

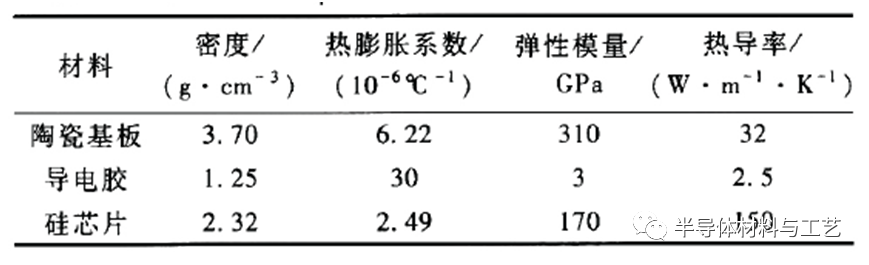

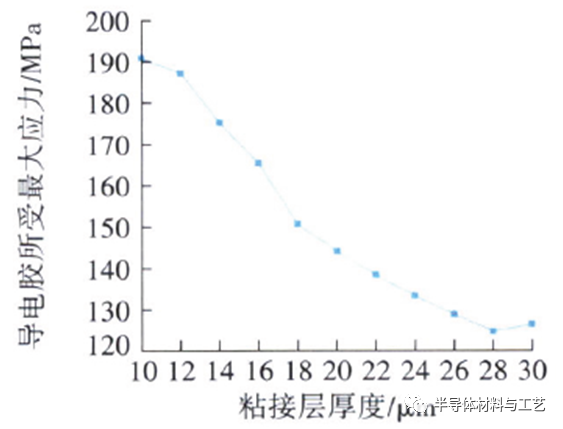

2.1 粘接層厚度對芯片封裝內應力的影響

為研究超大尺寸芯片的粘接內應力與粘接層厚度的關系,模型中設定導電膠的熱膨脹系數為3x10-5/oC,彈性模量為3 GPa,固化溫度為175oC,粘接層厚度為10~30 um。圖2為導電膠所受的最大應力隨粘接層厚度的變化關系,從圖中可以看出隨著粘接層厚度增大,導電膠所受的最大應力呈減小趨勢;當粘接層厚度較小時,導電膠所受的最大應力隨粘接層厚度的增加迅速減小。

圖2 粘接層厚度與導電膠所受最大應力的關系

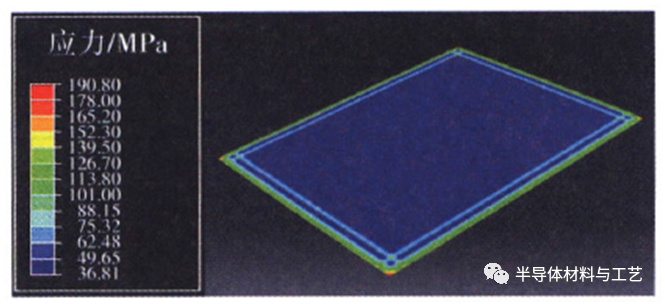

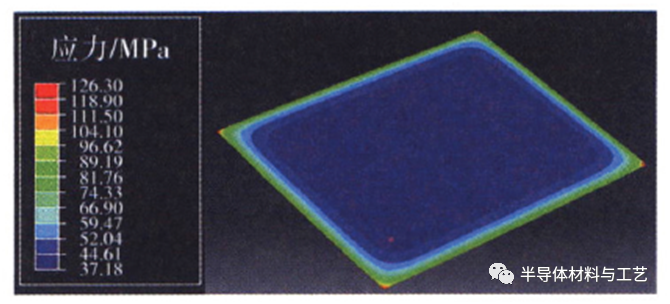

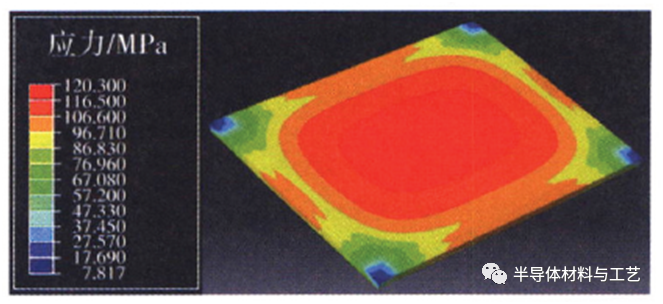

圖3為不同粘接層厚度(10 um和30 um)粘接層所受應力情況,從圖中可以看出,粘接層所受應力集中在導電膠和芯片粘接界面邊緣處,且粘接層四個角所受的應力最大。

(a)粘接層厚度為10 um

(b)粘接層厚度為3 0 um圖3 不同厚度粘接層所受應力

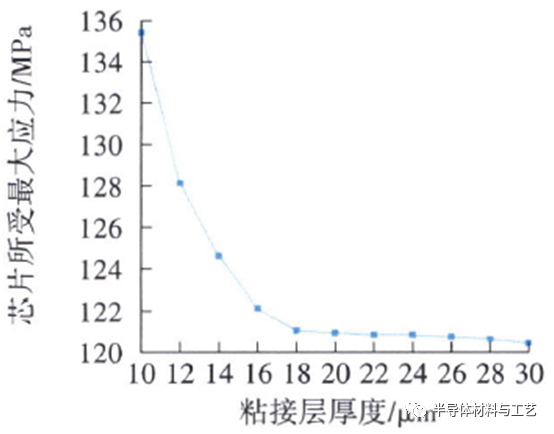

圖4為芯片所受最大應力與粘接層厚度的關系,從圖中可以看出隨著粘接層厚度增大,芯片所受的最大應力快速減小,當粘接層厚度達到18 um后,芯片所受的最大應力基本保持不變。因此,在超大尺寸芯片的貼片工藝中可適當增加粘接層厚度來降低器件的內應力,同時要保證芯片四個角有膠溢出,防止芯片因受應力而發生脫落。

圖4 粘接層厚度與芯片所受最大應力的關系

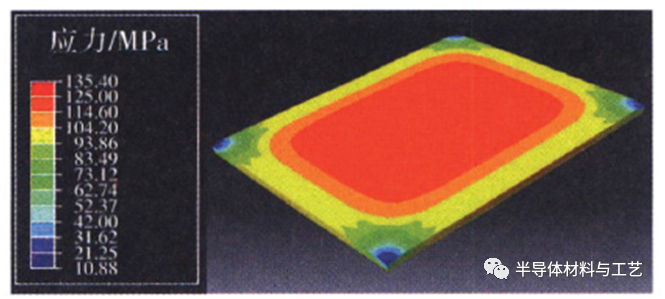

圖5為不同粘結層厚度(10 um和30 um)芯片所受應力情況,從圖中可以看出,芯片所受應力主要分布在芯片中心區域,芯片中心易受應力過大而產生裂紋。粘結層厚度太厚會導致其熱阻增大,阻礙熱的傳導。綜合考慮器件散熱和內應力影響,后續在分析導電膠的彈性模量、熱膨脹系數及固化溫度對超大尺寸芯片內應力的影響時,將導電膠的厚度設定為20 um。

(a)粘接層厚度為10 um

(b)粘接層厚度為3 0 um圖5 不同粘接層厚度芯片所受應力

2.2 彈性模量對芯片封裝內應力的影響

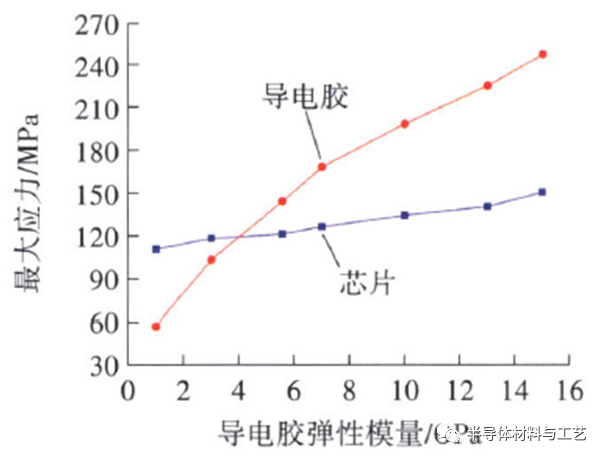

超大尺寸芯片粘結所使用的導電膠一般為環氧樹脂導電膠,其在高溫固化過程中會使基體樹脂在空間中形成三維網狀交錯結構,為芯片提供良好的支撐和保護,環氧樹脂導電膠彈性模量變化范圍比較寬,從幾GPa到十幾GPa。為表征該參數對大尺寸芯片封裝內應力的影響,假設導電膠的熱膨脹系數為3x10-5/oC,固化溫度為175 oC,粘接層厚度為20 um,彈性模量從1~15 GPa遞增。圖6為彈性模量與導電膠和芯片所受最大應力的關系。

圖6 彈性模量與導電膠和芯片所受最大應力的關系

從圖6可以看出,隨著導電膠彈性模量的增加,導電膠所受最大應力快速增大,芯片所受最大應力緩慢增大。故在超大尺寸芯片的貼片工藝中要選取低彈性模量的導電膠,以防芯片在溫度變化時所受應力過大而發生破裂,影響器件的電性能。

2.3 熱膨脹系數對芯片封裝內應力的影響

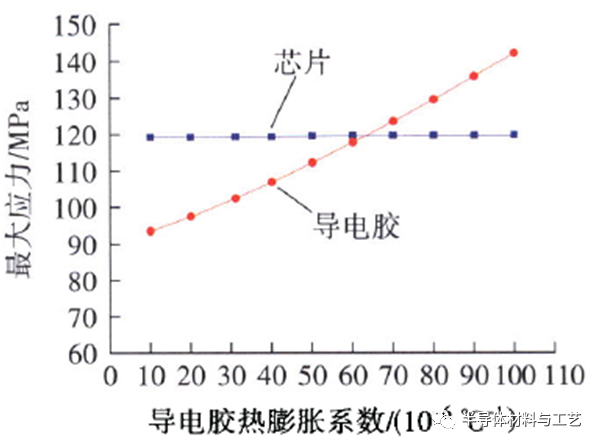

假設導電膠的彈性模量為3 GPa,固化溫度為175 oC,粘接層厚度為20 um,導電膠的熱膨脹系數為1x10-5/oC~1x10-4/oC,研究熱膨脹系數對大尺寸片上系統(SoC)芯片粘接內應力影響。圖7為導電膠熱膨脹系數與導電膠和芯片所受最大應力的關系。從圖7可以看出,隨著導電膠熱膨脹系數的增加,導電膠所受最大應力逐漸增大,芯片所受最大應力基本保持不變。故在超大尺寸芯片的貼片工藝中,要選取低熱膨脹系數的導電膠,以降低器件所受內應力。

圖7 熱膨脹系數與導電膠和芯片所受最大應力的關系

2.4 固化溫度對芯片封裝內應力的影響

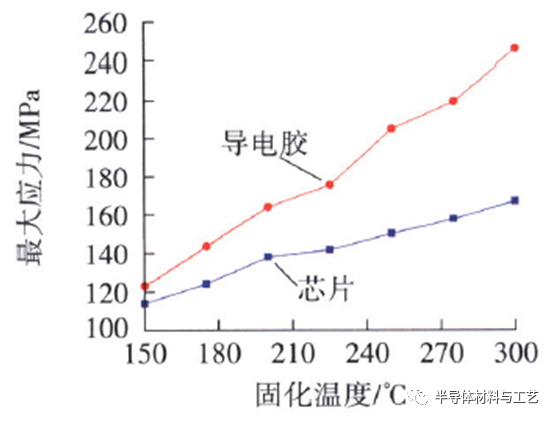

導電膠的產品手冊中會給出幾種不同的固化溫度,為表征該參數對大尺寸芯片粘接內應力影響,假設導電膠的彈性模量為3 GPa,導電膠的熱膨脹系數為3x10-5/oC,粘接層厚度為20 um,固化溫度為150~300oC。圖8為固化溫度與導電膠和芯片所受最大應力的關系。從圖8可以看出,選取較高的固化溫度時,導電膠和芯片所受最大應力比較大。故在超大尺寸芯片的貼片工藝中要選取較低的固化溫度,以降低器件所受內應力。

圖8 固化溫度與導電膠和芯片所受最大應力的關系

2.5 試驗驗證

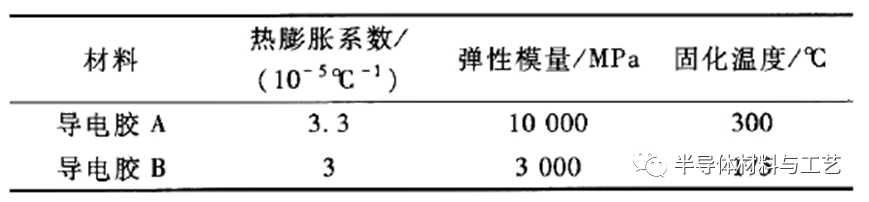

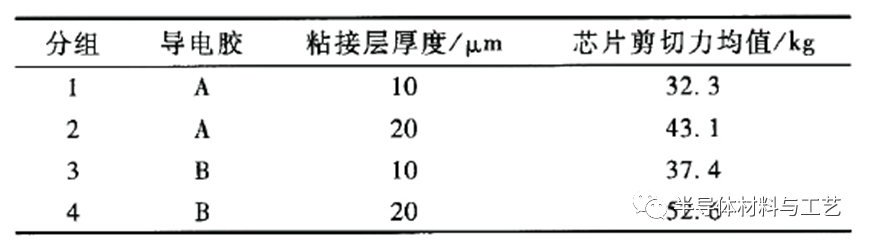

使用導電膠A和導電膠B進行試驗,驗證仿真結果。導電膠的性能參數如表3所示。分別用導電膠A和B將14mm x 10mm x 0.35mm芯片粘接在陶瓷基板上。試驗分四組進行,如表4所示,每個試驗組包含20只樣品。

表3 導電膠性能參數

表4 試驗分組及各分組的芯片剪切力均值

導電膠固化完成后將4組樣品按照GJB548B-2005方法1010的要求進行100次溫度循環試驗,試驗條件為-65~150 oC,高低溫總轉換時間不得超過1 min,停留時間不得少于10 min。試驗后對樣品進行芯片剪切力試驗,芯片剪切力的大小反映了芯片粘接內應力對粘結力的影響,試驗接果如表4所示。

經過溫度循環試驗后,分組1、分組2和分組3的部分樣品的粘接面邊緣均出現縫隙,且芯片剪切力也較低;分組4樣品經過試驗后粘接面邊緣未出現縫隙,且芯片剪切力也較前3組的大,因此,增加粘接層厚度,采用較低彈性模量的導電膠和較低的固化溫度可有效降低產品的內應力。

3 結論

本文利用有限元分析方法,采用簡化的結接構模型,研究了導電膠的粘接層厚度、彈性模量、熱膨脹系數及固化溫度對超大尺寸芯片粘接內應力的影響,主要結論如下。

①超大尺寸芯片的粘接內應力與導電膠粘接厚度關系密切。當粘接層厚度增大時,導電膠所受的最大應力呈減小趨勢;隨著粘接層厚度增大,芯片所受的最大應力快速減小,當粘接層達到一定厚度后,芯片所受應力基本保持不變。

②在超大尺寸芯片的貼片工藝中可適當增加粘接層厚度來降低器件的內應力;粘接層四個角所受應力最大,故在貼片時要保證膠在芯片四個角的溢出,防止芯片發生脫落。

③當導電膠的彈性模量增加時,導電膠和芯片所受最大應力逐漸增大,在超大尺寸芯片的貼片工藝中要選取低彈性模量的導電膠。

④當導電膠的熱膨脹系數增大時,導電膠所受最大應力逐漸增大,芯片所受應力基本保持不變。在超大尺寸芯片的貼片工藝中要選取低熱膨脹系數的導電膠。

⑤選取較高的固化溫度時,導電膠和芯片所受應力比較大。故在超大尺寸芯片的貼片工藝中要選取較低的固化溫度,以降低器件所受內應力。

審核編輯:郭婷

-

芯片

+關注

關注

455文章

50730瀏覽量

423184 -

封裝

+關注

關注

126文章

7880瀏覽量

142899 -

微處理器

+關注

關注

11文章

2259瀏覽量

82406

原文標題:【半導光電】超大尺寸芯片封裝內應力的改善

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

[轉帖]壓電效應的有限元分析及壓電懸置控制方法的研究(碩士論文)

MATLAB有限元分析與應用

如何有效的學習CAE有限元分析

求一種有限元分析中PCBA的簡化建模方法

有限元分析及應用_曾攀

abaqus動力學有限元分析指南

有限元分析相關知識的解析

基于箱形梁CADCAE有限元分析

利用有限元分析方法的超大尺寸芯片的改善封裝設計

利用有限元分析方法的超大尺寸芯片的改善封裝設計

評論