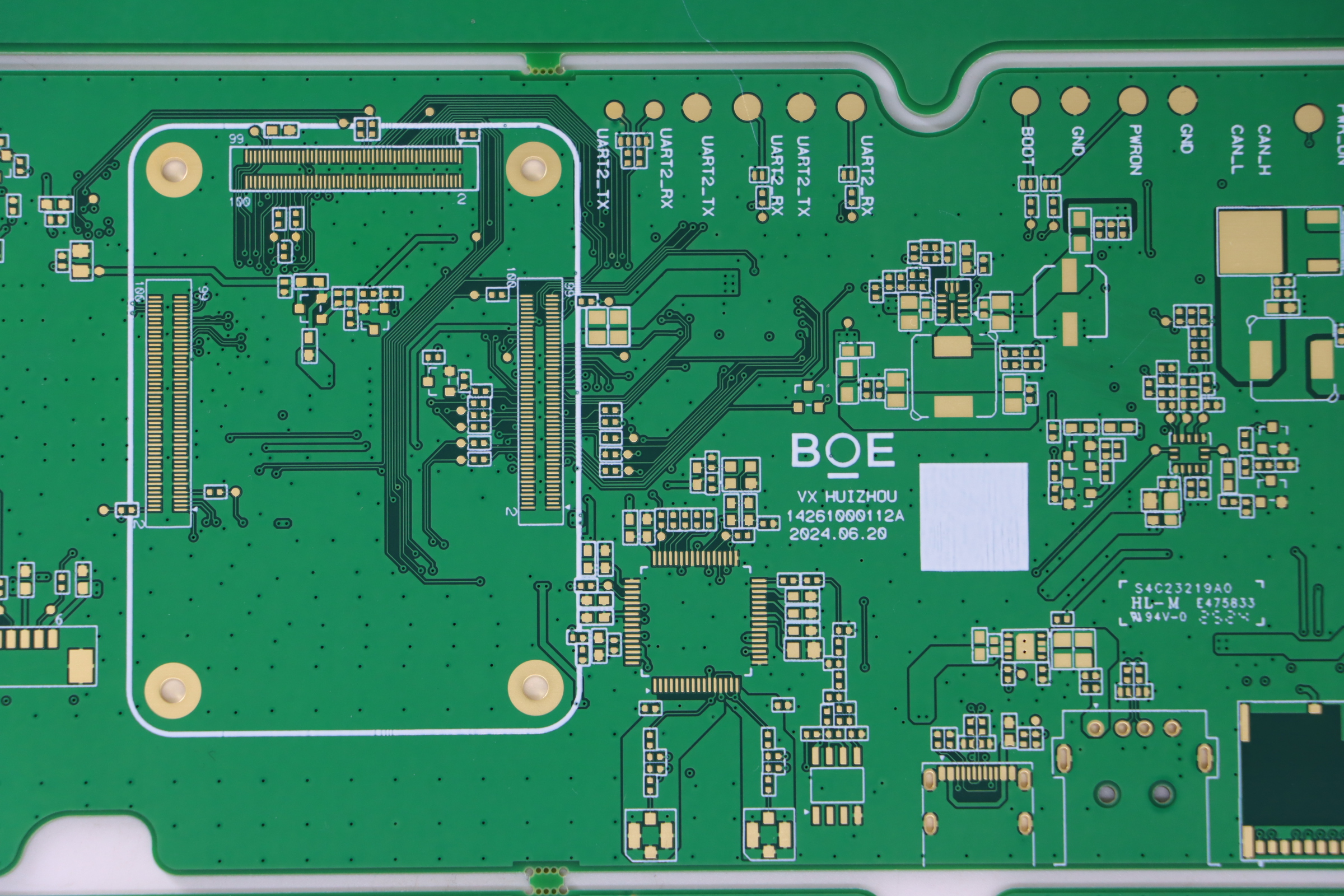

隨著高速電路的不斷涌現,PCB板的復雜度也越來越高,為了避免電氣因素的干擾,信號層和電源層必須分離,所以就牽涉到多層 PCB的設計,即疊層結構設計。好的疊層設計不僅可以有效地提高電源質量、減少串擾和EMI、提高信號傳輸性能,還能節約成本,為布線提供便利,這是任何高速PCB設計者都必須首先考慮的問題。

PCB疊層設計的十個小技巧

1.分層

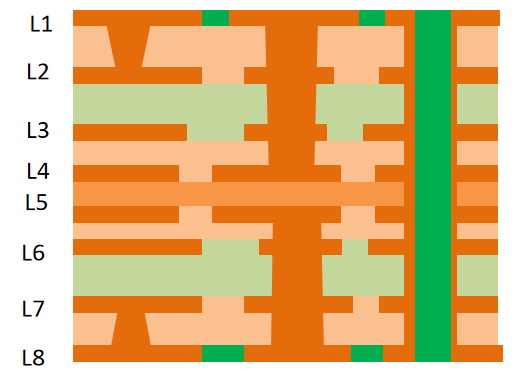

在多層PCB中,通常包含有信號層(S)、電源(P)平面和接地(GND)平面。電源平面和接地平面通常是沒有分割的實體平面,它們將為相鄰信號走線的電流提供一個好的低阻抗的電流返回路徑。信號層大部分位于這些電源或地參考平面層之間,構成對稱帶狀線或非對稱帶狀線。多層PCB的頂層和底層通常用于放置元器件和少量走線,這些信號走線要求不能太長,以減少走線產生的直接輻射。

2.確定單電源參考平面(電源平面)

使用去耦電容是解決電源完整性的一個重要措施。去耦電容只能放置在PCB的頂層和底層。去耦電容的走線、焊盤,以及過孔將嚴重影響去耦電容的效果,這就要求設計時必須考慮連接去耦電容的走線應盡量短而寬,連接到過孔的導線也應盡量短。例如,在一個高速數字電路中,可以將去耦電容放置在PCB的頂層,將第2層分配給高速數字電路(如處理器)作為電源層,將第3層作為信號層,將第4層設置成高速數字電路地。

此外,要盡量保證由同一個高速數字器件所驅動的信號走線以同樣的電源層作為參考平面,而且此電源層為高速數字器件的供電電源層。

3.確定多電源參考平面

多電源參考平面將被分割成幾個電壓不同的實體區域。如果緊靠多電源層的是信號層,那么其附近的信號層上的信號電流將會遭遇不理想的返回路徑,使返回路徑上出現縫隙。對于高速數字信號,這種不合理的返回路徑設計可能會帶來嚴重的問題,所以要求高速數字信號布線應該遠離多電源參考平面。

4.確定多個接地參考平面(接地平面)

多個接地參考平面(接地層)可以提供一個好的低阻抗的電流返回路徑,可以減小共模EMl。接地平面和電源平面應該緊密耦合,信號層也應該和鄰近的參考平面緊密耦合。減少層與層之間的介質厚度可以達到這個目的。

5.高速信號層位于信號中間層

電路中的高速信號傳輸層應該是信號中間層,并且夾在兩個鋪銅層之間。這樣兩個鋪銅層的銅膜可以為高速信號傳輸提供電磁屏蔽,同時也能有效地將高速信號的輻射限制在兩個鋪銅層之間,不對外造成干擾。

6.設定布線方向

在同一信號層上,應保證大多數布線的方向是一致的,同時應與相鄰信號層的布線方向正交。例如,可以將一個信號層的布線方向設為"Y軸”走向,而將另一個相鄰的信號層布線方向設為“X軸”走向。

7.多電源層遠離高速信號層多電源層要注意遠離高速數字信號布線。因為多電源層會被分割成幾個電壓不同的實體區域,如果緊靠多電源層的是信號層,那么其附近的信號層上的信號電流將會遭遇不理想的返回路徑,使返回路徑上出現縫隙。

8.采用偶數層結構經典的PCB疊層設計幾乎全部是偶數層的,而不是奇數層的。偶數層印制電路板具有成本優勢,同時偶數層比奇數層更能避免電路板翹曲。

9.布線組合安排在鄰近層為了完成復雜的布線走線的層間轉換是不可避免的。一個信號路徑所跨越的兩個層稱為一個“布線組合”。最好的布線組合設計是避免返回電流從一個參考平面流到另一個參考平面,而是從一個參考平面的一個點(面)流到另一個點(面)。因此,布線組合最好安排在鄰近層,因為一個經過多層的路徑對于返回電流而言是不通暢的。雖然可以通過在過孔附近放置去耦電容或者減小參考平面間的介質厚度等來減小地彈,但也非一個好的設計。

10.成本考慮

在制造成本上,在具有相同的PCB面積的情況下,多層電路板的成本肯定比單層和雙層電路板高,而且層數越多,成本越高。但在考慮實現電路功能和電路板小型化,保證信號完整性、EMl、EMC 等性能指標等因素時,應盡量使用多層電路板。綜合評價,多層電路板與單雙層電路板兩者的成本差異并不會比預期的高很多。

關于PCB多層板設計有什么技巧?PCB多層板設計10個小技巧的知識點,想要了解更多的,可關注領卓PCBA,如有需要了解更多PCB打樣、SMT貼片、PCBA加工的相關技術知識,歡迎留言獲取!

審核編輯:湯梓紅

-

多層板

+關注

關注

2文章

151瀏覽量

27883 -

疊層設計

+關注

關注

0文章

26瀏覽量

6196 -

PCB

+關注

關注

1文章

1795瀏覽量

13204

發布評論請先 登錄

相關推薦

PCB基礎知識:單面板和多層板講解以及如何確定在電路設計中使用單面板還是多層板?

高多層板的生產工藝

對于多層板pcb走線一般原則

多層pcb板電路之間如何工作

PCB多層板和PCB單層板有什么區別

PCB多層板是什么?它有哪些特點?

HDI多層板制作工藝

全面掌握高多層PCB板材、制造流程與工藝難點

掌握這十個技巧,輕松搞定PCB多層板設計

掌握這十個技巧,輕松搞定PCB多層板設計

評論