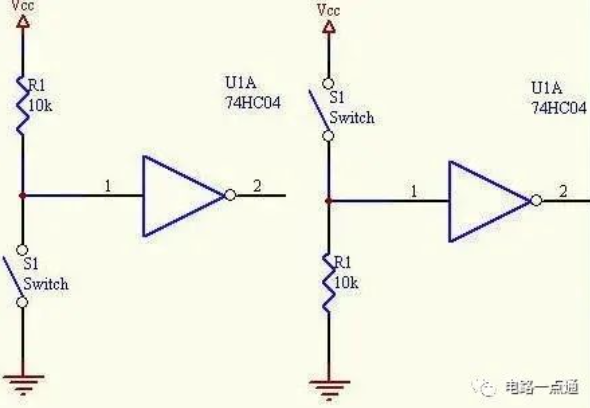

1、根據I2C總線規范,總線空閑時兩根線都必須為高;

這是規定,動不了的,不然什么叫標準呢?其實所謂的這個神圣的標準也并不是多么邪乎,你想啊,只有是高的才能拉成低的,難道誰可以把低的拉成高的嗎?所以這是之所以規定空閑時必須為高的一個原因,要是保持“低”的話,那是不可能成為“多主”總線的。

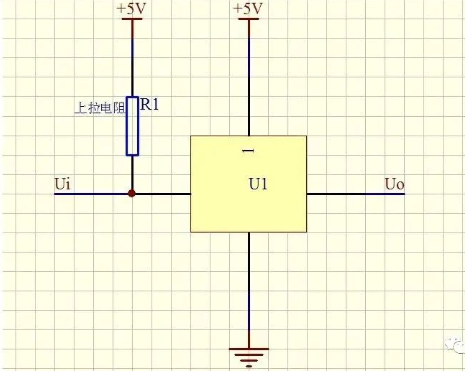

2、上拉電阻的問題;

其實各個I2C接口工作時只檢測高、低電平,管你有沒有什么上拉電阻呢!

但問題是,你要是直接接電源的來實現高的話,一旦其他器件拉低時豈不危險?

所以,這個上拉電阻有保護作用。如果你確信直接接電源沒問題(比如有短路保護等,呵呵),也可以試一試,問題的關鍵是主器件要能正確的拉低或置高,從器件要能明確地區分高、低就可以了,這是問題的關鍵,當然,還有時序問題,不能混亂!

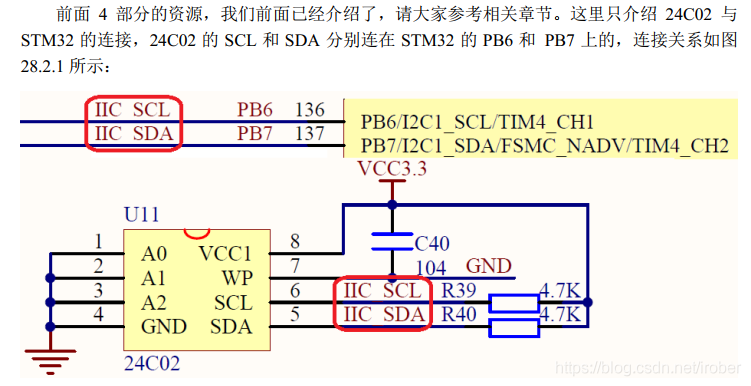

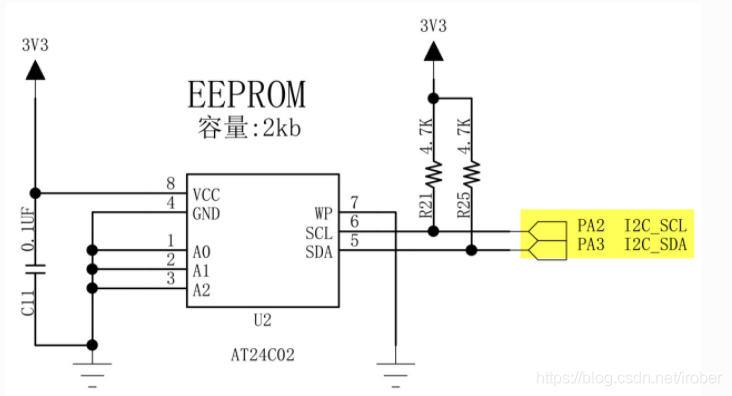

STM32f103的I2C例程:

理論上,軟件IIC可以使用任何通用引腳。

有人用PA2和PA3進行IIC通信。

3、電阻大小的問題;

最直接的,牽涉到兩方面的問題,首先是功耗的問題,其次是速度的問題,二者是矛盾的!如果你想盡量提高速度,那么就牽涉到總線電容的問題,其實很容易理解,上拉電阻與總線的電容形成了RC,高速時將直接影響通訊!因為總線拉高時有個充電時間以及高電平的閥值,如果還沒有充電到足以保證從器件可以識別的高電平的閥值時主器件就以為完成了一個總線動作的話,那么通訊肯定是不能進行的!

如果你想盡可能降低功耗,那么就要盡可能增大電阻以最大可能的減小電路各部分的消耗電流從而實現整體降低功耗!但不可能無限大,否則充電時間你會受不了的!

備注:

I2C的上拉電阻可以是1.5K,2.2K,4.7K, 電阻的大小對時序有一定影響,對信號的上升時間和下降時間也有影響,一般接1.5K或2.2K

I2C上拉電阻確定有一個計算公式:

Rmin={Vdd(min)-0.4V}/3mA

Rmax=(T/0.874) *c, T=1us 100KHz, T=0.3us 400KHz

C是Bus capacitance

Rp最大值由總線最大容限(Cbmax)決定,Rp最小值由Vio與上拉驅動電流(最大取3mA)決定;

于是 Rpmin=5V/3mA≈1.7K(@Vio=5V)或者2.8V/3mA≈1K(@Vio=2.8V)

Rpmax的取值:參考周公的I2C總線規范中文版P33圖39與P35圖44

標準模式,100Kbps總線的負載最大容限<=400pF;快速模式,400Kbps總線的負載最大容限<=200pF,根據具體使用情況、目前的器件制造工藝、PCB的走線距離等因素以及標準的向下兼容性,設計中以快速模式為基礎,即總線負載電容<200pF,也就是傳輸速度可以上到400Kbps是不成問題的。于是Rpmax可以取的范圍是1.8K~7K @ Vio=5V對應50pF~200pF

上拉電阻阻值的確定

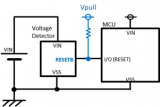

由于I2C接口采用Open Drain機制,器件本身只能輸出低電平,無法主動輸出高電平,只能通過外部上拉電阻RP將信號線拉至高電平。因此I2C總線上的上拉電阻是必須的!

RP不宜過小,一般不低于1KΩ

一般IO端口的驅動能力在2mA~4mA量級。如果RP阻值過小,VDD灌入端口的電流將較大,這導致端口輸出的低電平值增大(I2C協議規定,端口輸出低電平的最高允許值為0.4V);如果灌入端口的電流過大,還可能損壞端口。故通常上拉電阻應選取不低于1KΩ的電阻(當VDD=3V時,灌入電流不超過3mA)。

RP不宜過大,一般不高于10KΩ

由于端口輸出高電平是通過RP實現的,線上電平從低到高變化時,電源通過RP對線上負載電容CL充電,這需要一定的時間,即上升時間。端口信號的上升時間可近似用充電時間常數RPCL乘積表示。

信號線負載電容(對地)由多方面組成,包括器件引腳、PCB信號線、連接器等。如果信號線上掛有多個器件,負載電容也會增大。比如總線規定,對于的400kbps速率應用,信號上升時間應小于300ns;假設線上CL為20PF,可計算出對應的RP值為15KΩ。

如果RC充電時間常數過大,將使得信號上升沿變化緩慢,達不到數據傳輸的要求。

因此一般應用中選取的都是幾KΩ量級的上拉電阻,比如都選取4K7的電阻。

小阻值的RP電阻增大了端口Sink電流,故在可能的情況下,RP取值應稍大一點,以減少耗電。另外,通產情況下,SDA,SCL兩條線上的上拉電阻取值是一致的,并上拉到同一電源上。

PCB布局布線與抗干擾設計

I2C信號線屬于低速控制線,在手機PCB設計時,按通常的控制IO對待即可,無需做特別的保護設計,一般不用擔心受到噪聲源干擾。

但在一些特定的情況下,比如折疊、滑蓋機型中,I2C的兩根信號線需要通過轉軸或滑軌處的FPC,此時由于信號路徑比較長,距離天線比較近,而且Open drain的輸出級對地阻抗大,對干擾比較敏感,因此比較容易受到RF信號源的干擾。在這種情況下,就應適當注意對I2C信號線的保護。比如I2C兩條信號線(SDA,SCL)等長度地平行走線,兩邊加地線進行保護,避免臨近層出現高速信號線等。

上拉電阻應安置在OD輸出端附近。當I2C總線上主從器件(Master& Slave)兩端均為OD輸出時,電阻放置在信號路徑的中間位置。當主設備端是軟件模擬時序,而從設備是OD輸出時,應將電阻安置在靠近從設備的位置。

I2C協議還定義了串聯在SDA、SCL線上電阻Rs。該電阻的作用是,有效抑制總線上的干擾脈沖進入從設備,提高可靠性。這個電阻的選擇一般在100~200ohm左右。當然,這個電阻并不是必須的,在惡劣噪聲環境中,可以選用。

比如常用的FM接收模塊或者Capsense觸摸感應功能塊,都是通過I2C接口控制的。I2C接口信號從處理器出發,經過PCB上的信號路徑,進入上述電路單元。I2C信號線上載有一定干擾,這種干擾雖然幅度并不很大,但還是會影響敏感的FM接收模塊或Capsense觸摸感應功能塊。此時,可以通過在靠近FM模塊或觸摸感應模塊的I2C信號線上串接Rs電阻,即可有效降低干擾的影響。此外,上拉電阻端的電源也要進行退耦處理。

軟件模擬I2C時序

由于一般的I2C應用速率并不高(400kbps),使用處理器的IO口模擬I2C波形,完全可以勝任(處理器一般擔任Master,占有I2C通信的控制權,無需擔心隨機的I2C通信服務中斷其他任務的執行)。

處理器分配給I2C任務的IO口,要求可以輸出高低電平,還能配置為輸入端口。處理器根據總線規范以及從設備的時序要求,利用2條IO信號線,模擬I2C接口時序波形,進行I2C通信。

處理器發送數據時,通過IO口輸出高電平,上升時間基本與外部上來電阻阻值無關,且比用外部上拉電阻上拉到高電平快很多。處理器在接受數據時,即便上拉電阻阻值選的大一些,從設備輸出數據的波形上升沿緩慢,但由于處理器使用軟件采樣的而非硬件采樣,因此,對數據傳輸的結果并不影響。也就是說,使用IO口模擬I2C時序時,上拉電阻阻值可以適當選的大一些。

需要指出的是,使用軟件模擬最多只能完成單Master的應用,對于多Master應用,由于需要進行總線控制權的仲裁管理,使用軟件模擬的方法很難完成。

I2C總線空閑的時候,兩條信號線應該維持高電平。否則,上拉電阻上會有耗電。特別是在上電過程中,IO線上電平也應保持在高電平狀態。也就是說:當Master的I2C使用的是IO軟件模擬時,一定要保證該兩個IO上電默認均為輸入(或高阻)或者輸出高電平,切不可默認為輸出低電平。IO默認為輸入時,可以通過外部上拉電阻將I2C信號線拉至高電平。

I2C應用中上拉電阻電源問題

在部中分應用中,還存在主從設備以及上拉電阻電源不一致的情況,比如Camera模組。在很多設計方案中,Camera模組不工作時,并不是進入Power Down模式,而是直接關閉模組供電VDDS。此時,處理器與模組相互連接的所有信號線都應該進入高阻態,否則就會有電流漏入模組;而對于此時的I2C控制信號線來說,由于上拉電阻的存在,必須關斷上拉電阻電源VDDP。如果上拉電阻使用的是系統電源VDDM(VDDP=VDDM),無法關閉,就會有漏電流進入模組;因此這種情況下,應該使用VDDS作為上拉電阻電源(VDDP=VDDS),這樣上拉電阻電源與Slave電源即可同時關閉,切斷了漏電路徑。

另外需要注意的是,在上述應用實例中選擇的IO,應該選取上電默認為輸入(或高阻)才行。

總的來說:電源電壓限制了上拉電阻的最小值 ;負載電容(總線電容)限制了上拉電阻的最大值

補充:在I2c總線可以串連300歐姆電阻RS可以用于防止SDA和SCL線的高電壓毛刺: I2c從設備的數量受總線電容,<=400pF的限制

做過I2C碰到過各種問題,多半是上拉電阻或者控制器時鐘的問題。沒上拉電阻或者上拉電阻過大,都會導致不穩定而出現尋址不到的問題。

審核編輯 黃昊宇

-

電阻

+關注

關注

86文章

5507瀏覽量

171931 -

IIC

+關注

關注

11文章

300瀏覽量

38311

發布評論請先 登錄

相關推薦

IIC信號線需要增加上拉電阻,是因為IIC的IO是什么

【干貨】IIC上拉電阻的選擇與計算

【干貨】IIC上拉電阻的選擇與計算

評論