之前在設計板卡時,只是聽過相關的概念,但是未真正去研究關于SI相關的知識。將之前看過的一些資料整理如下:

1、信號完整性分析

與SI有關的因素:反射,串擾,輻射。反射是由于傳輸路徑上的阻抗不匹配導致;串擾是由于線間距導致;輻射則與高速器件本身以及PCB設計有關。

傳輸線判斷

先解釋一下什么是高速電路:信號的最高頻率成分是取決于有效頻率,而不是周期頻率。

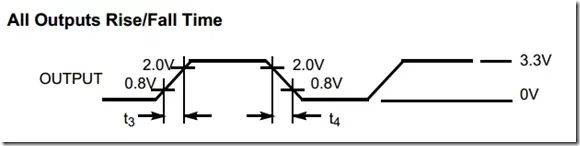

高速電路的定義是根據信號的有效頻率來計算的,在現實世界中,任何信號都是由多個頻率分量的正弦波疊加而成的。定義各正弦波分量的幅值為VN,則VN = 2 / (3.14 x N),可見各級諧波分量的幅值與頻率成反比。現實信號,隨著頻率的升高,其各級諧波分量的幅值比理想方波中相同頻率正弦波分量的幅值下降的更快,直到某級諧波分量。其幅值下降到理想方波中對應分量的70%(即功率下降到50%),定義該諧波分量的頻率為信號的有效頻率,其計算公式為:Fknee = 0.5 / Tr(10% ~ 90%),其中Tr(10% ~ 90%)為信號上升沿部分的10%~90%,一般在數據手冊中都會給出相應的時間。如圖中所示的t3。

某手冊輸出信號上升時間

利用判斷高速信號的公式,所以對于高速和低速的區分,需要考慮信號頻率和傳輸路徑長度。

判斷步驟:

1)獲得信號的有效頻率Fknee 和走線長度 L;

2)利用Fknee 計算出信號的有效波長λknee,,即λknee = C /Fknee ;

3)判斷L與1/6 x λknee之間的關系,若L > 1/6 x λknee,則信號為高速信號,反之為 低速信號;

其中λknee = C / Fknee;其中C是比光速略低的速度,Fknee = 0.5 / Tr(10% ~ 90%),還需注意的是,若是對于百兆頻率的信號,若是沒有現成的板子,可以對有效頻率Fknee進行估算, Fknee 約為 7倍的Fclock(信號的周期)。

若L > 1/6 x λknee,則視為傳輸線,傳輸線必須考慮在傳輸過程中可能由于阻抗不匹配導致信號的反射問題。

反射公式

信號的反射ρ = (Z2 -Z1)/(Z2 +Z1);

其中Z2 為反射點之后的線路阻抗;Z1為反射之前的線路阻抗;

ρ 的可能存在值±1,0,當為0時全部吸收,當為±1時則發生反射。信號的反射由始端、傳輸路徑、終端阻抗的不匹配導致。

降低反射方法

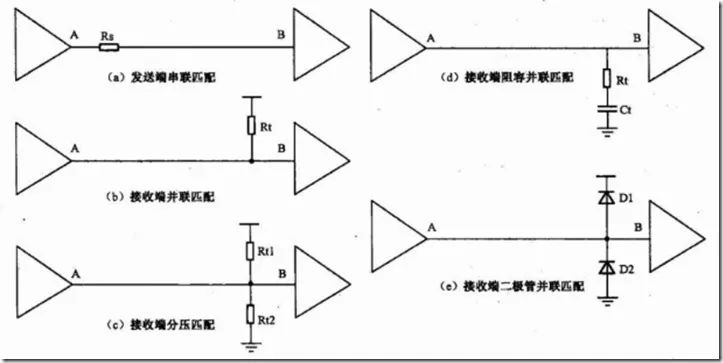

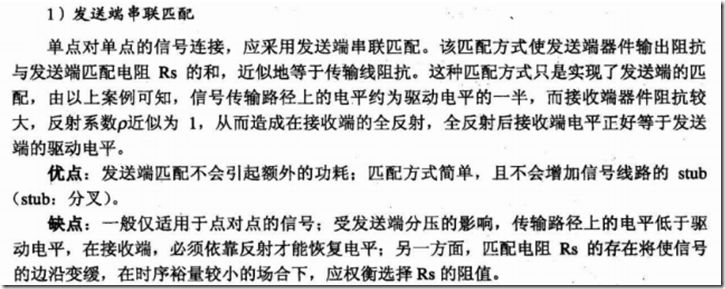

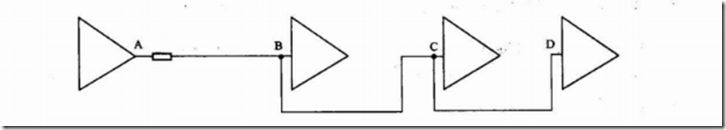

為了盡可能降低信號的反射,那么需要Z2 和Z1盡可能相近。有幾種方法進行阻抗匹配:發送端串聯匹配,接收端并聯匹配,接收端分壓匹配,接收端阻容并聯匹配,接收端二極管并聯匹配。

3)接收端分壓匹配

4)接收端阻容并聯匹配

優點:功耗較小;

缺點:存在接收端高低電平不匹配情況,由于電容的存在,會使信號的邊沿變化變緩。

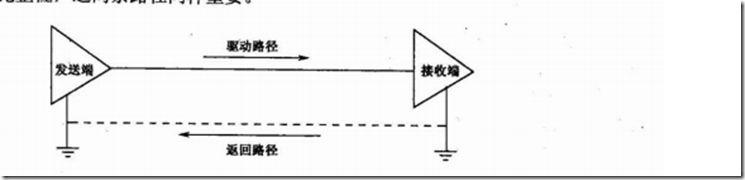

2、信號回路

信號回路主要包括兩個路徑,一個是驅動路徑,一個是回路路徑,在發送端、傳輸路徑、接收端測得的信號電平,實質上是該信號在驅動路徑和返回路徑上對應位置的電壓值,這兩條路徑都非常重要。

要提供完整的回流路徑,需要注意以下幾點:

1.信號換層時,最好不要改變參考層,若信號的換層時從信號層1換到信號層。參考層都是底層1,在這種情況下,返回路徑無需換層,即信號的換層對其反回路徑無影響。

2.信號換層時,最好不改變參考層的網絡屬性。也就是信號1開始的參考層是電源層1/地層1,經過換層之后,信號1的參考層是電源層2/地層2,其參考層的網絡屬性未變,都是GND或電源屬性,可利用附近的GND或者電源過孔實現反回路徑的通路。這里在高速情況下,過孔的容抗和感抗也是不能忽略的,這種情況下,盡量減小過孔,減小過孔本身產生的阻抗變化影響,減小對信號回流路徑的影響。

3.信號換層時,最好在信號過孔附近增加一個與參考層同屬性的過孔。

4.若換層前后,兩層參考層的網路屬性不同,要求兩參考層相距較近,減小層間阻抗和返回路徑上的壓降。

5.當換層的信號較密集時,附近的地或者電源過孔之間應保持一定距離,換層信號很多時,需要多打幾個對地或者對電源的過孔。

3、串擾

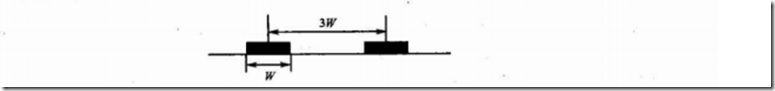

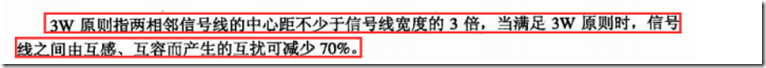

解決串擾的辦法是,高速信號,時鐘信號,其他數據信號等,間距滿足3W原則。

審核編輯:郭婷

-

pcb

+關注

關注

4319文章

23111瀏覽量

398321 -

阻抗

+關注

關注

17文章

958瀏覽量

46023 -

信號完整性

+關注

關注

68文章

1409瀏覽量

95504 -

高速電路

+關注

關注

8文章

158瀏覽量

24247 -

高速器件

+關注

關注

0文章

9瀏覽量

3009

原文標題:PCB設計中越早解決效率越高的關鍵——信號完整性(SI)[20221214]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB設計中信號完整性SI的重要性

PCB設計中信號完整性SI的重要性

評論