作者:Siddharth Devarajan, Larry Singer, Dan Kelly, Tao Pan, Jose Silva, Janet Brunsilius, Daniel Rey-Losada, Frank Murden, Carroll Speir, Jeffery Bray, Eric Otte, Nevena Rakuljic, Phil Brown, Todd Weigandt, Qicheng Yu, Donald Paterson, Corey Petersen, Jeffrey Gealow, and Gabriele Manganaro

本文介紹了一種 12 位 10GS/s 交錯 (IL) 流水線模數轉換器 (ADC)。該 ADC 采用 4 GHz 輸入信號實現 55 dB 的信噪比和失真比 (SNDR) 和 66 dB 的無雜散動態范圍 (SFDR),采用 28 nm CMOS 技術制造,功耗為 2.9 W。 八個流水線子 ADC 交錯以實現 10 GS/s 采樣速率,子 ADC 之間的不匹配在后臺校準。流水線子ADC采用多種技術來降低功耗,例如避免專用采樣保持放大器(無SHA)、殘余縮放、閃存背景校準、抖動和級間增益誤差背景校準。針對高頻線性度優化的推挽式輸入緩沖器驅動交錯式子 ADC,以實現 >7GHz 帶寬。快速開啟自舉開關可實現 100ps 采樣。該ADC還能夠隨機化子ADC選擇模式,以進一步減少殘余交錯雜散。

索引術語 — 校準、CMOS、數字輔助模擬設計、直接射頻采樣模數轉換器 (ADC)、千兆赫茲數據轉換、交錯 (IL) ADC、流水線 ADC、開關電容器。

介紹

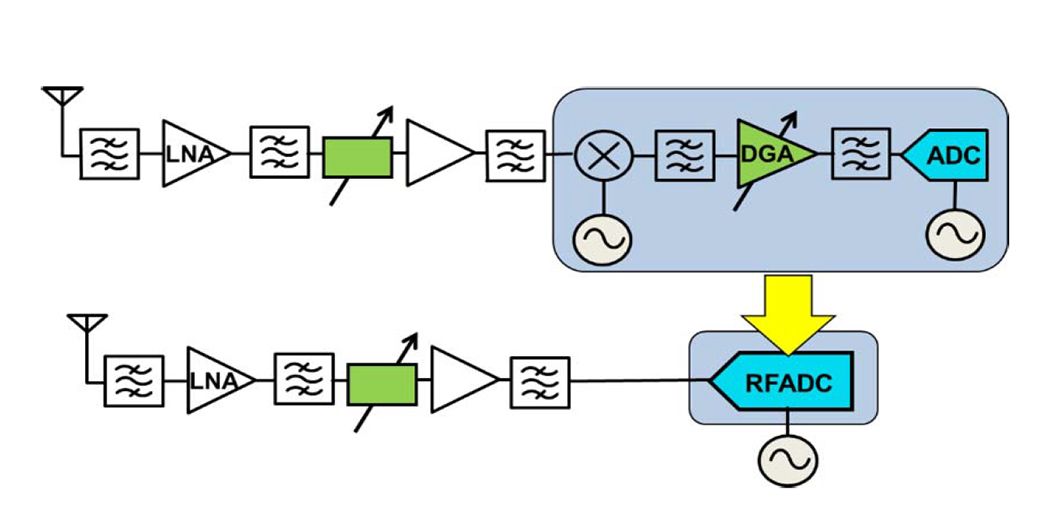

分辨率大于10 b、采樣率遠達千兆赫范圍的高速模數轉換器(ADC)設計的最新進展使軟件定義無線電可用于各種應用,包括通信系統和數據采集系統[1]-[5]。雖然傳統上使用較窄帶無線電(如圖1上半部分所示的外差接收器),但數據轉換技術的發展使寬帶ADC能夠取代信號鏈的重要部分,如圖1下半部分所示,從而降低系統復雜性、功耗和成本。

圖 1.傳統外差接收器與直接RF接收器的比較。

宏蜂窩基站、衛星通信系統以及電子戰系統和高性能臺式測量系統等無線基礎設施系統正在推動對射頻頻率高達3.2 GHz的千兆赫寬帶(有時是由于合并多個獨立的子頻段,共存于不同的載波頻率)的信號直接數字化的需求, 并且具有相當高的線性度(例如,在 1 GHz 或更高時 SFDR 約為 70 dB)和低噪聲頻譜密度(例如,噪聲頻譜密度 (NSD) 約為 –150 dBFS/Hz 或更高)。不幸的是,由于采樣率(fs) 的 ADC 增加,其功耗增加:首先線性與 fs然后與 f 超線性s;因此,使ADC的效率越來越低,最終使其實施變得不切實際。交錯式(IL)ADC可以實現更高的采樣速率轉換,同時保持功耗可控。然而,涉及多種設計權衡,需要克服許多架構和電路設計挑戰。

本文描述了一種采用28納米CMOS技術制造的12-b 10 GS/s IL流水線ADC[6]。該 ADC 交錯于由單個輸入緩沖器驅動的 8 個 12 b 流水線子 ADC 陣列,并采用各種校準、抖動和隨機化技術來提高頻譜性能。

圖 2.施賴爾FOM和相關ADC趨勢[8]。

本文的組織結構如下。在第二部分中,概述了與千兆赫茲采樣率交錯相關的一些架構權衡和挑戰。第三部分首先描述了該設計中采用的整體架構以及各種交錯校準。接下來,在III-A節中,討論與子ADC相關的架構和電路,以及它們的校準和抖動。III-B部分介紹包括輸入緩沖器在內的前端電路設計,III-C部分討論順序交錯子ADC的殘余效應,以及隨機選擇子ADC的好處。原型IC的測量結果在第IV節中報告。與類似的先進ADC的比較是第五節的主題。最后,第六節提供了摘要和結論。

交錯和架構權衡

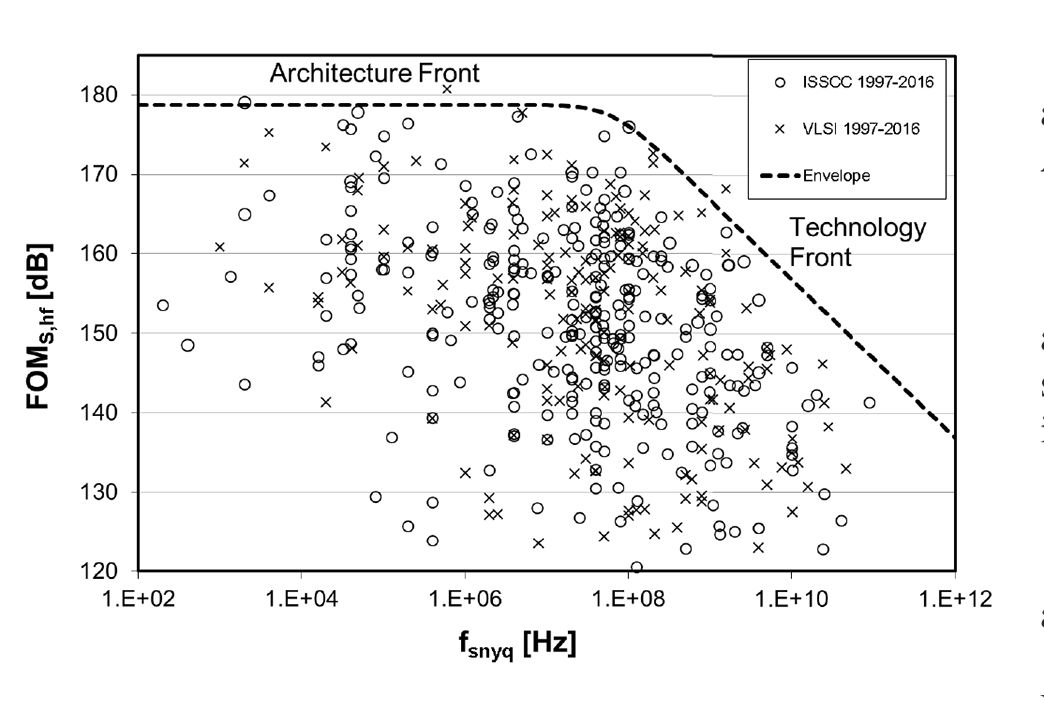

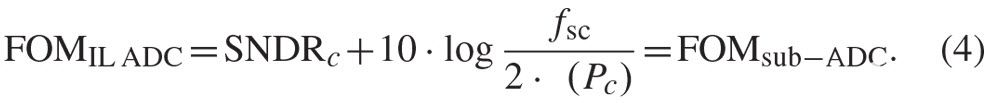

評估ADC功率效率的常用品質因數(FOM),稱為施賴爾FOM,是

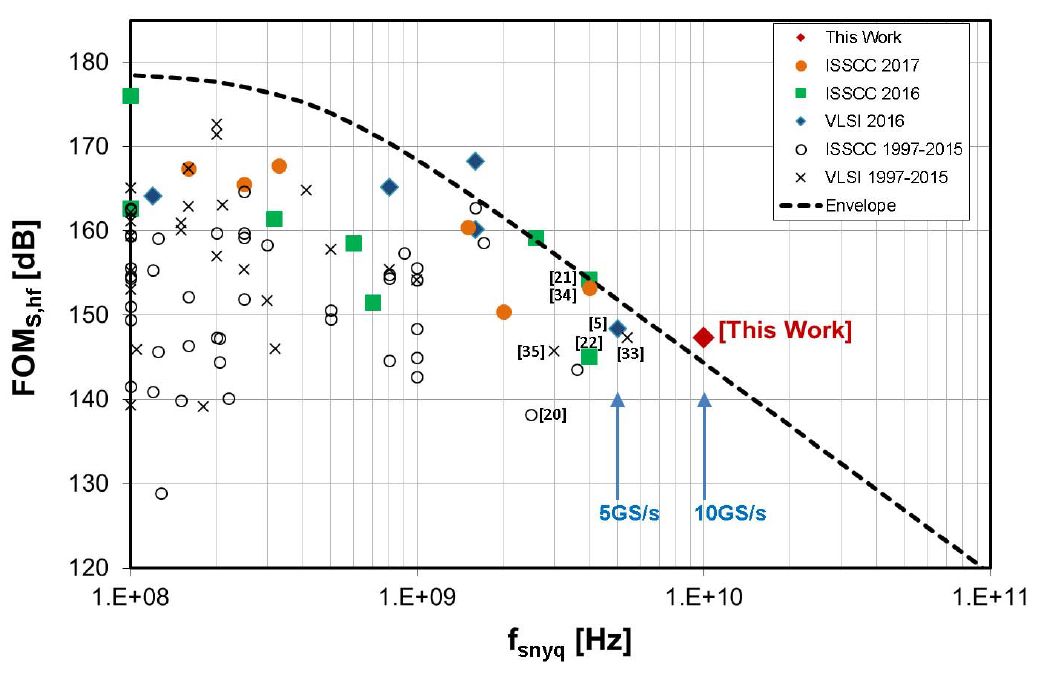

其中 SNDR分貝是以分貝 f 表示的信噪比和失真比斯尼克是奈奎斯特采樣率(對應于采樣率fs除以過采樣率),P是功耗[7]。圖2所示的顯示FOM [8]的散點圖顯示了最高采樣速率ADC的效率如何迅速下降,位于通常稱為“技術前沿”的漸近對角線虛線內,并且主要受給定工藝技術中晶體管速度的限制。因此,隨著較新的ADC采用更精細的光刻CMOS工藝和更快的器件,技術前沿向右[7]轉移,更高的采樣速率ADC變得實用。

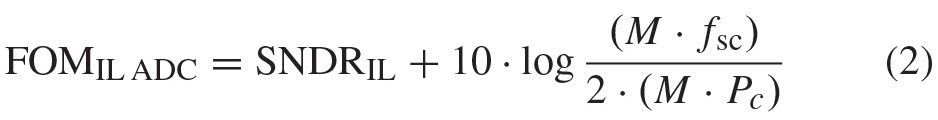

雖然對于非IL(或單核)ADC架構來說也是如此,但IL(或并行)ADC提供了擴展工藝技術速度限制的理論潛力[9]。事實上,至少在原則上,通過交錯M個相同的ADC(稱為子ADC),每個ADC的時鐘頻率為f南卡羅來納州和消耗Pc瓦特,一個 IL ADC 采樣速率為 fs= M ·f南卡羅來納州和消耗 P = M ·Pc瓦特可以設計。

首先,人們可以得出結論,IL ADC應該與其子ADC一樣高能效,因為IL ADC的FOM是

并且由于原則上,SNDRC的子ADC與SNDR相同伊利諾伊州IL ADC,然后通過替換 (2)

最后

因此,回到圖2,從具有FOM的子ADC開始設計子模數轉換器,位于技術前沿的左側,并與遞增的M交錯,可以設想構建越來越快的IL ADC,具有恒定的FOM(向圖形添加新點以獲得更大的f)。s但不斷橫坐標),最終超越了技術前沿設定的極限。

然而,在實踐中,要從子ADC構建IL ADC,需要相當多的額外電路開銷。這包括信號緩沖、路由、基準電壓源、時鐘和控制、輸入信號源的前端接口、數字后端解復用、不同部分的電源以及校準電路。所有這些都會消耗額外的功率Po,Po隨M和fs線性或超線性增長,因此,當引入對數(2)參數的分母時,會降低IL ADC的實際效率

由于最高FOM是在采樣速率較低的非IL ADC架構中獲得的,例如逐次逼近(SAR)轉換器,因此在具有大交錯階M [9]-[14]的IL ADC中找到此類SAR子ADC已成為降低功耗的常見現象。然而,上述模型以及其他更復雜的分析表示[15],[16]并未捕獲影響最終IL ADC頻譜性能和驅動性能的其他重要架構考慮因素。

雖然高能效、高交錯階ADC(例如M>10)面臨著許多實際實現挑戰,將其分辨率限制在10 b左右[17],[18]。此外,隨著M的增加,輸入緩沖器必須驅動更多的子ADC,從而增加前端負載,從而降低輸入帶寬(BW)和線性度,并增加功耗[16],[17]。相反,更高的采樣速率子ADC架構,如流水線子ADC [19],雖然功耗效率略低,但降低了M(對于相同的f)。s),這有助于減少前端負載,減少實現挑戰、復雜性和開銷,并已顯示出更高的分辨率 [20]-[22]。

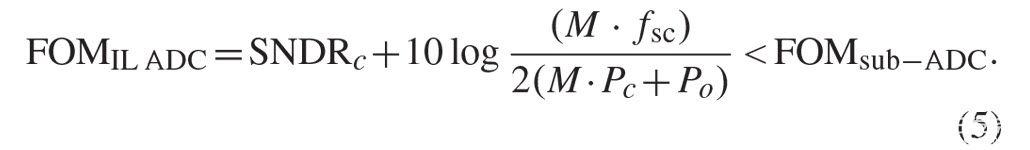

圖 3.12-b 10-GS/s ADC 架構。

因此,雖然較高M SAR陣列和較低M流水線陣列均有其優點,但基于嚴格的頻譜性能和寬帶寬目標,本文選擇流水線子ADC架構,并采用各種技術來降低流水線子ADC的功耗。最近發布的 14 b 2.5-GS/s 流水線 ADC [5] 是這些性能水平下最快的非 IL 流水線 ADC,是 28 納米 CMOS 中此類流水線 ADC 速度限制的重要數據點。我們的評估表明,在28納米CMOS技術中,高能效流水線子ADC可以設計為低于2 GS/s的采樣率。此外,在IL ADC中使用二進制數量的子ADC通常可以實現更好的匹配布局。考慮到所有這些因素,在這項工作中交錯使用八個子ADC以實現10 GS/s,這種架構選擇與其他IL流水線ADC有相似之處[20],[18]。

交錯式 ADC 架構

整體ADC架構如圖3所示。8個流水線子ADC交錯實現10 GS/s采樣速率。單個公共輸入緩沖器用于驅動輸入信號,V在,以用于所有八個子 ADC。八個子ADC的數字輸出進入各個子ADC數字校準模塊,用于校正子ADC缺陷。單獨校正的子ADC輸出進入一個公共IL校準模塊,該模塊估計并校正子ADC之間的失配,否則會導致失配音[15],[16]。所有校準的估計和校正方面都在片上實現。偏移、增益和時序失配在后臺校準,以確保良好的頻譜性能。失調和增益失配在數字域中得到估計和校正[23]。然而,對于時序失配,估計是通過數字方式完成的,但校正是在模擬域中完成的[16],[24],[12]。為了估計時序偏差,假設IL失調和增益已經校準。如果所有子ADC在等間隔的時刻采樣,則它們平均與相鄰的子ADC采樣具有相同的相關性。如果子ADC早期偏斜,那么它與緊接在它之前的樣本的相關性會更高,而與緊隨其后的樣本的相關性會降低,同樣,平均而言[16]。對于每個子ADC,在其輸出和緊隨其后的采樣之間執行相關性。如果 ADC[n]子ADC_M是用第 M 個子 ADC 采集的第 n 個總體 ADC 樣本,則感興趣的相關值為

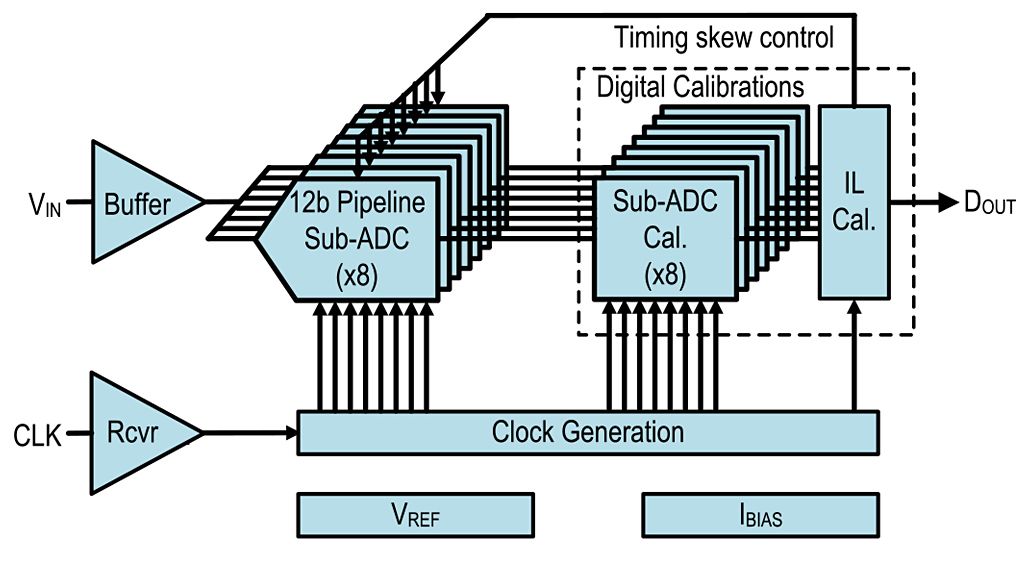

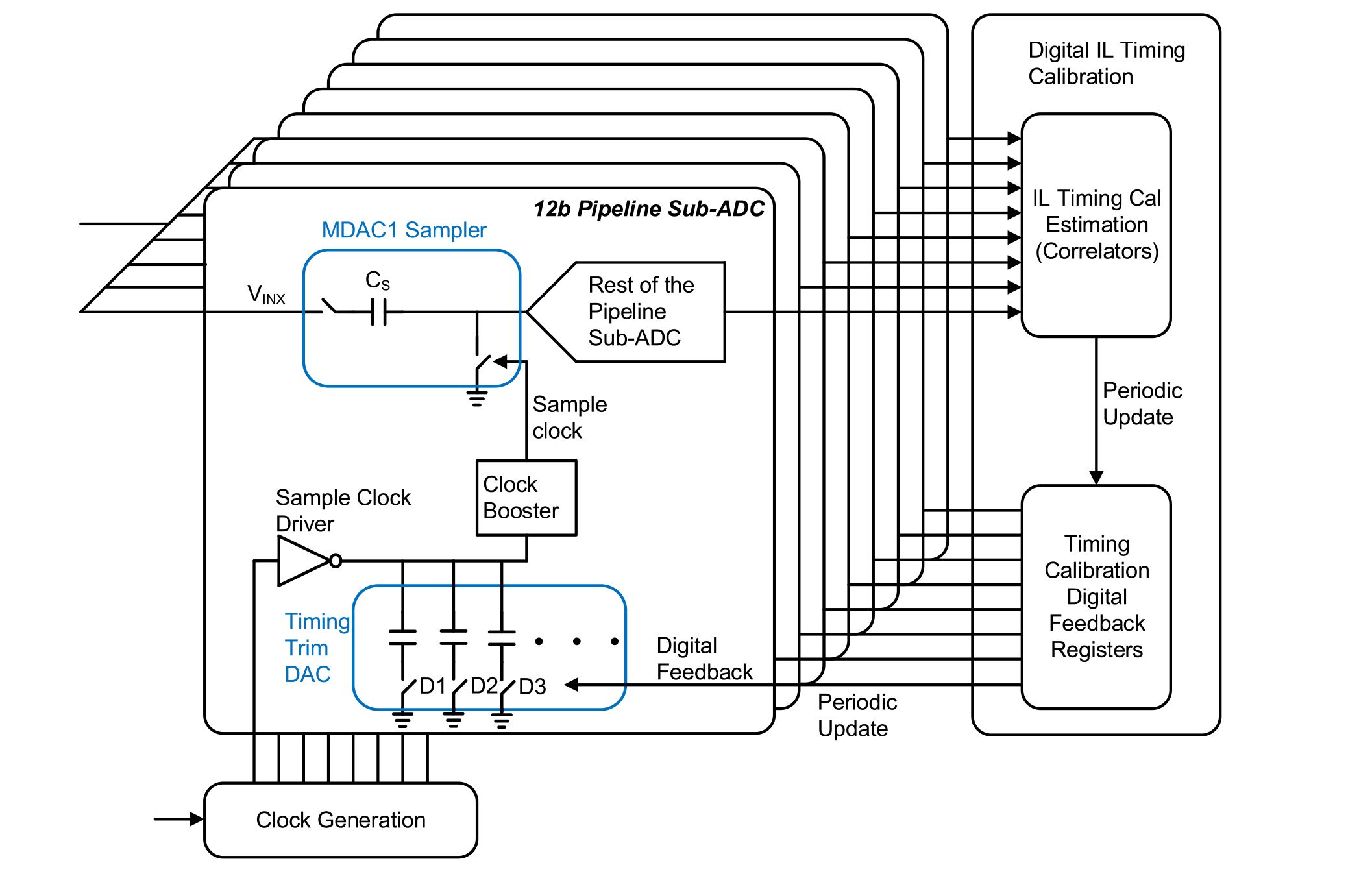

其中 E 是期望值或平均值。將其中一個子ADC作為基準,所有其他子ADC時序偏差根據其與該參考相關性的差異定期調整,使用遞歸數字反饋環路在后臺連續工作[16]。時序失配的校正可以使用有限脈沖響應濾波器[22]以數字方式完成,但即使在像28 nm CMOS這樣的高級工藝中,這種具有10 fs定時分辨率的濾波器的功耗也會大大高于模擬偏斜校正,后者是通過在采樣時鐘驅動器上加載電容式數模轉換器(DAC)來實現的[22]。完整的時序偏斜數字反饋環路及其在每個子ADC內控制的DAC如圖4所示。通過打開(或關閉)開關以加載(或卸載)逆變器以延遲(或提前)采樣時鐘來調整采樣時間。

為了完成架構描述,如圖3所示,差分時鐘接收器(Rcvr)由片外10 GHz時鐘(CLK)發生器驅動,時鐘接收器的輸出進入時鐘生成電路,該電路生成所有交錯時鐘相位,以控制子ADC操作,例如采樣、閃存中的粗量化、 并增加DAC(MDAC)殘基的產生。該ADC包括片內基準電壓生成和偏置電流生成電路。

A. 子ADC架構和電路實現

如前文第一節所述,這項工作交織相對較快(>1.25 GS/s)的流水線子ADC。28 nm等先進CMOS技術中的流水線架構使這種GHz子ADC具有非常好的頻譜性能。在這項工作中,采用了多種技術來最大限度地降低流水線子ADC的功耗,而不會犧牲性能。為了最大限度地降低功耗,流水線子 ADC 設計為采用內核 1V 電源供電。低壓流水線的主要挑戰之一是設計具有足夠擺幅、增益精度和線性度的MDAC放大器[25]。流水線子ADC設計用于處理1.4 Vpp差分的輸入信號擺幅,這給在1 V電源上設計MDAC帶來了挑戰。為MDAC放大器使用更高的電源將導致更高的功率和復雜性,其中包括當低壓MDAC放大器晶體管與高于額定電源一起使用時用于緩解電壓應力的額外電路,以及由于多個電源電壓而增加的電源布線復雜性。此外,由于開關電容MDAC電路中有多個電源域,時鐘和升壓器可能需要進一步的電平轉換(LS)。所有這些都將轉化為子ADC設計的更大面積,從而增加IL ADC在時鐘寄生效應和輸入緩沖器必須驅動的寄生效應方面的整體功耗。在這項工作中,MDAC放大器設計為采用1 V電源供電,以最大限度地減小面積和功耗,并結合使用模擬電路技術和數字校準技術來確保良好的性能。

圖 4.時序偏斜校正DAC和控制該DAC的整個數字反饋。

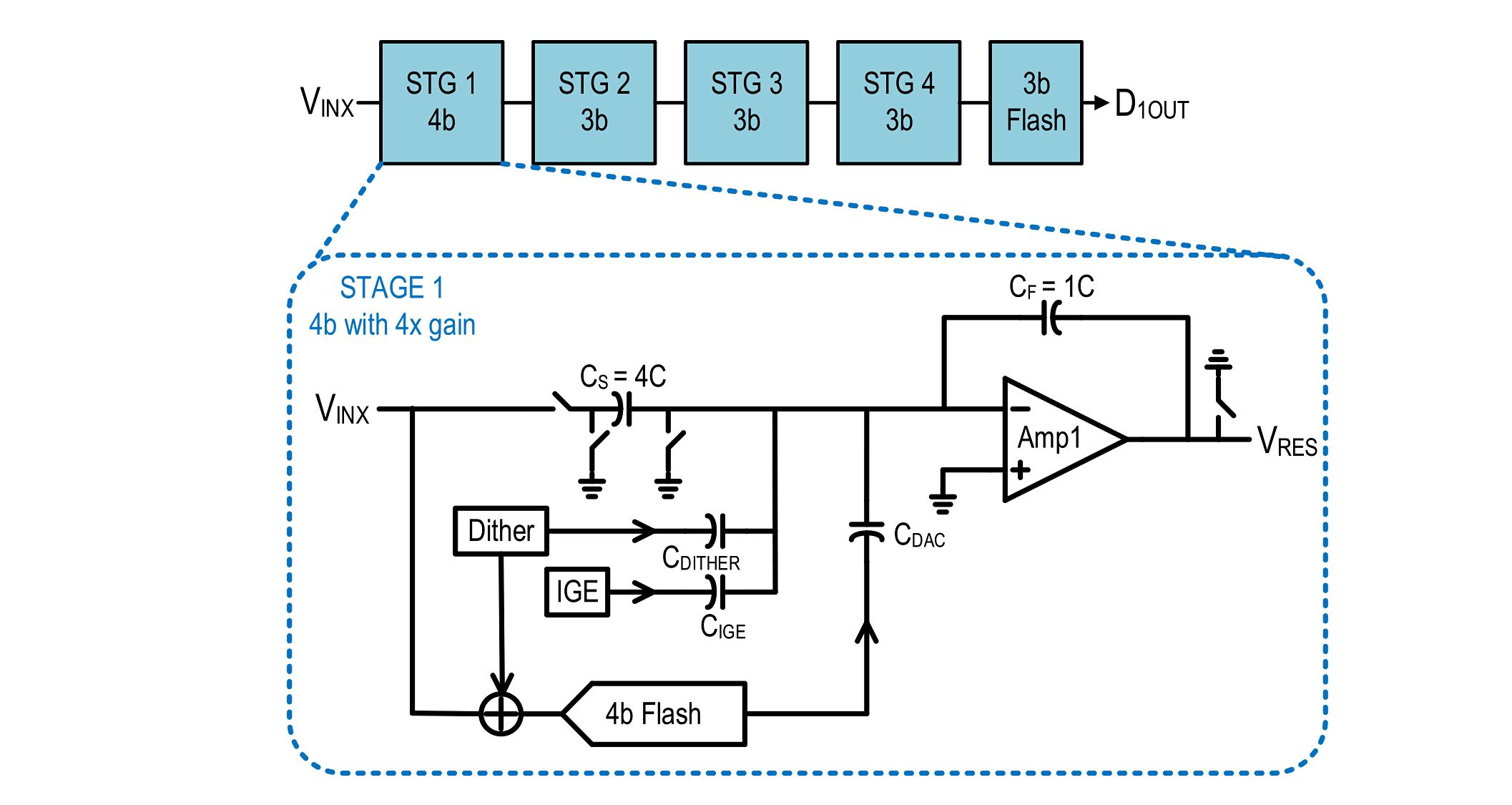

圖 5.12-b 流水線子 ADC 架構和階段 1 實現細節。

流水線子ADC的架構如圖5所示。該流水線由4-b第一級組成,隨后是三個3-b級和最后的3-b閃存。在熱噪聲受限設計中,MDAC分辨率(每級位數)的選擇通常被認為是相當淺的最佳選擇[26]-[28]。流水線子ADC無SHA格式,避免了SHA的功率、噪聲和失真開銷,但在MDAC和閃存之間的軌道帶寬方面引入了嚴格的匹配要求[29]。

流水線子ADC第一階段(階段1)的實現細節也如圖5所示。輸入信號V英克斯在采樣電容上采樣CS,4-b 閃光燈粗略量化V英克斯同時。4-b閃存的輸出驅動DAC電容器C代數轉換器和C代數轉換器減去電荷CS.使用單獨的DAC電容器,而不是重復使用CS同時執行DAC功能具有眾所周知的權衡[30],[28]。單獨的好處C代數轉換器分別是:1) 基準電壓緩沖器上的電荷毛刺與信號無關,允許使用低功耗基準電壓緩沖器;2)CS在保持階段結束時沒有非線性量化電荷,這消除了在CS返回軌道之前進行顯式復位階段的需要,從而節省了功耗。

單獨C代數轉換器噪聲增加,反饋因子降低。MDAC 放大器 Amp1 產生殘余,VRES,進入下一階段。在第1級注入抖動以線性化子ADC傳遞函數[28],并且還執行級間增益誤差(IGE)校準以校正背景中的MDAC增益誤差[31]。基準電壓緩沖器(圖5中未明確顯示)作為互補的推挽源跟隨器實現,以確保快速建立C代數轉換器MDAC 處于保持階段時的電容器。每個子ADC中的每個MDAC級都有自己的基準電壓緩沖器,基準電壓緩沖器之間的不匹配作為背景數字校準的一部分進行校正。對所有MDAC使用通用基準電壓緩沖器會導致該緩沖器必須驅動路由寄生電容到每個MDAC,從而導致更高的功耗。

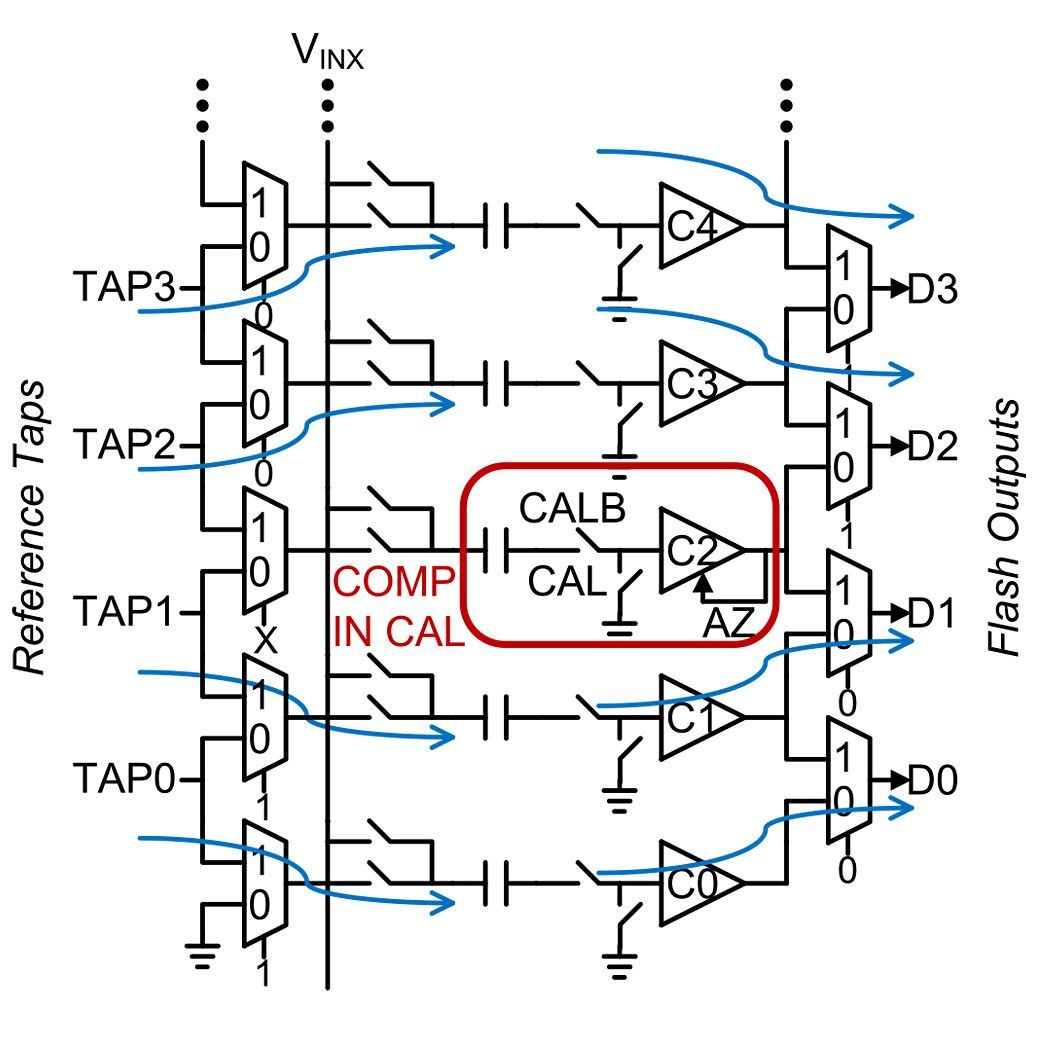

4-b閃存中的比較器使用小型器件來實現低功耗和小面積,因此其工藝失配會消耗很大的校正范圍。為了克服這個問題,4-b閃光燈采用背景校準方案來校正比較器偏移,如圖6所示。這項工作中的4-b閃存通常需要16個比較器(具有16個比較器轉換的MDAC傳遞函數將在本節后面解釋[28]),但是,為這種背景校準方案增加了一個額外的第17個比較器。在任何給定時間,主信號路徑操作只需要16個比較器,因此17個比較器中的一個離線移除并在后臺校準。所有比較器均按順序旋轉,以確保其所有偏移定期校準。在圖6中,突出顯示了正在校準的比較器。

圖 6.Flash1背景比較器偏移校準。

基準抽頭和比較器的輸出數據位在校準中如比較器周圍所示進行多路復用,以確保信號路徑功能不會因離線移除比較器進行校準而受到影響。正在自動歸零的比較器的輸入與采樣網絡斷開連接并短路以提供零輸入。背景偏移校準不僅可以消除工藝、電源和溫度變化的偏移,還可以消除晶體管老化引起的偏移漂移,這在28 nm等高級CMOS技術中可能很嚴重。

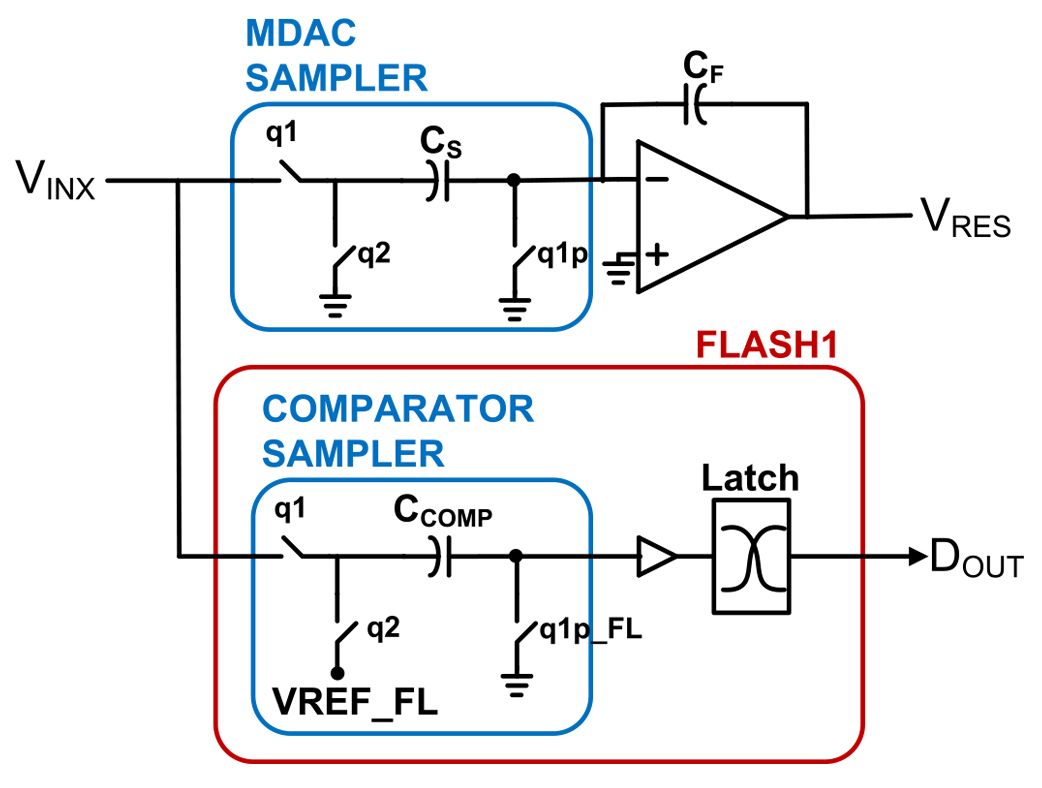

圖 7.閃存1采樣比較器架構,確保閃存1和MDAC1之間的帶寬匹配。

一個重要的無SHA考慮因素是,由于第1級的閃存和MDAC都對GHz輸入進行采樣,因此小的帶寬失配會消耗很大的校正范圍。為了盡量減少帶寬失配,在flash1中使用了采樣比較器架構[29],如圖7所示。V英克斯首先在MDAC和閃存中被動采樣,然后鎖存器觸發以產生比較器的輸出。雖然這種順序操作增加了比較器的延遲,而不是直接在鎖存器上采樣,但好處是能夠非常接近MDAC和閃存的軌道帶寬,因為它們在跟蹤輸入信號時都是分布式RC網絡。此外,為了能夠糾正MDAC和閃光燈之間存在的任何帶寬不匹配,MDAC(q1p)和閃光燈(q1p_FL)的采樣時鐘被分開,并在閃光燈采樣時鐘路徑中插入延遲線,以允許調整閃光燈采樣時間。此調整通過監測 stage1 V 的殘余在前景中完成RES并通過調整閃光燈采樣時鐘延遲來最小化高頻輸入信號條件下的幅度。

圖 8.階段 1 殘基轉移函數。

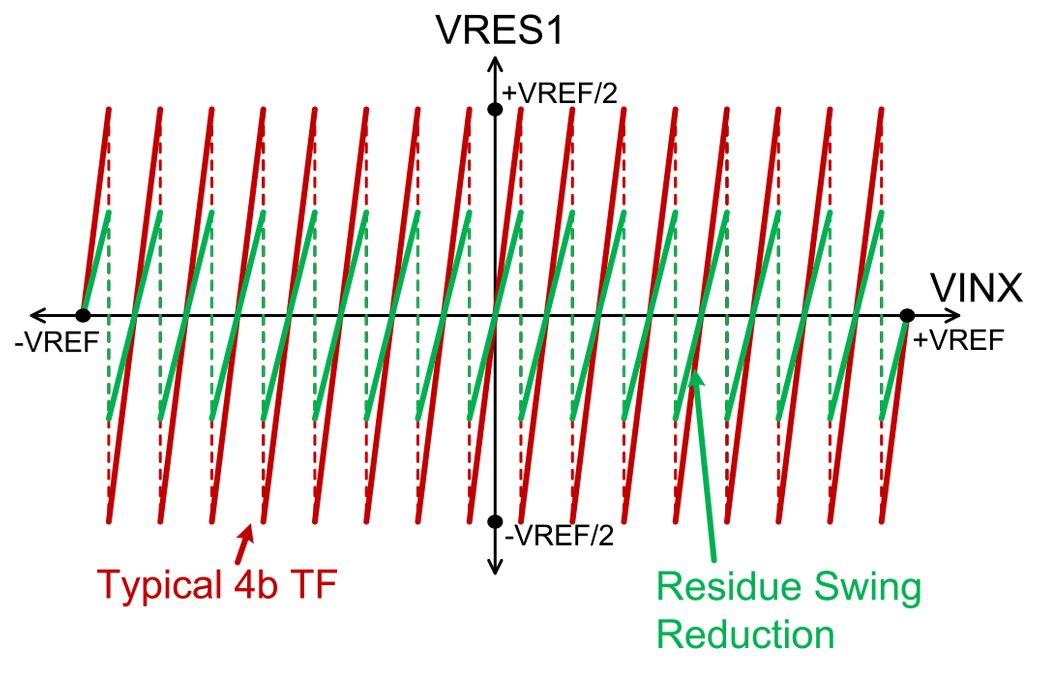

在4-b級中,MDAC的增益通常設置為2(4-1)= 8。然而,為了使 stage1 MDAC 能夠在核心電源下工作,在這項工作中殘余增益降低到 4,如圖 5 所示,其比率CS/CF= 4。圖8比較了增益為8的典型4-b級的兩個Stage1傳遞函數(TF)與增益為4的4-b級。雖然這種殘余增益降低使Amp1輸出端的擺幅減半并改善線性度,但它使以輸入為基準(即第2至5級)的后端噪聲加倍。然而,后端級為降低噪聲貢獻而增加的功率小于在階段1 MDAC中通過將其擺動減半而獲得的節能。圖8還顯示了4-b MDAC中16個比較器閃光躍遷的位置。

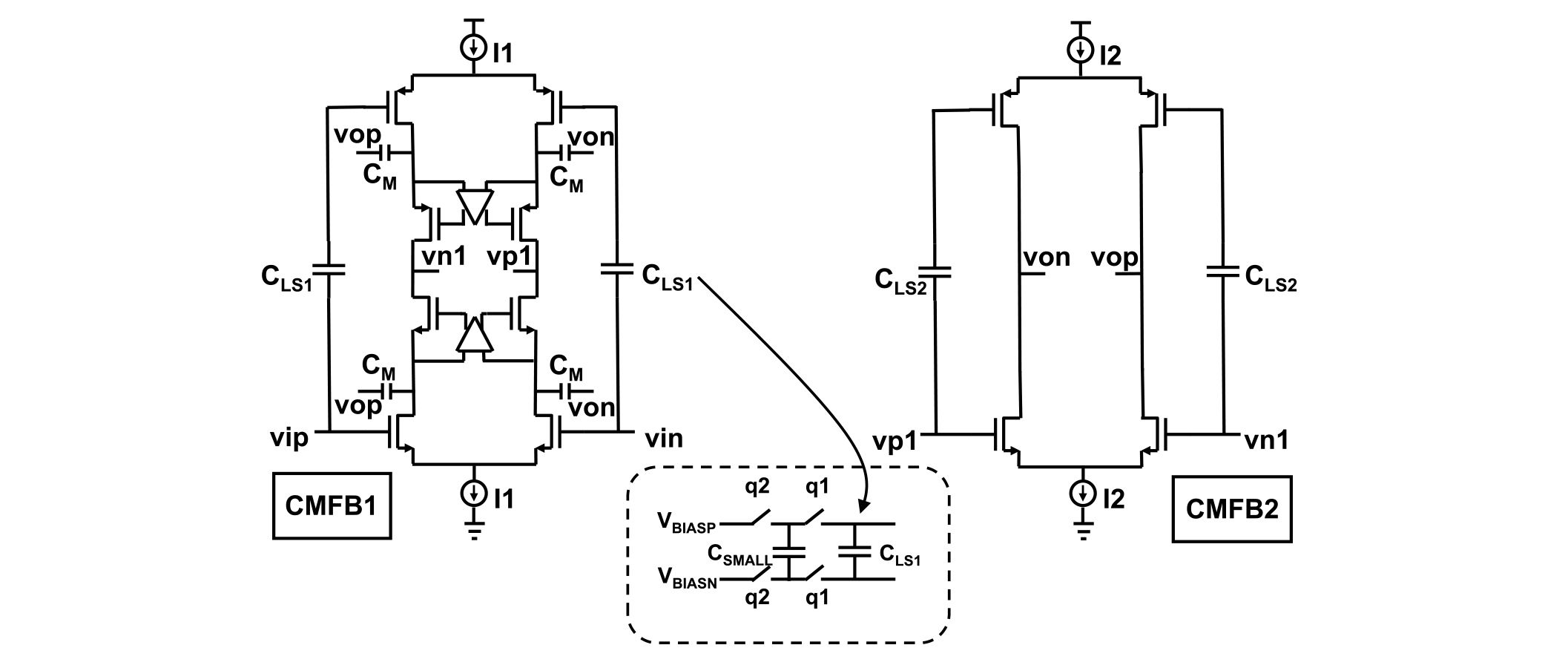

MDAC放大器的簡化晶體管級實現如圖9所示。該放大器采用兩級設計,采用分離式級聯補償方案。兩級均采用推挽互補架構,使電源效率翻倍(即雙gm/I)。然而,推挽式架構需要PMOS和NMOS的不同偏置點,這是通過使用動態電平轉換電容(CLS1和CMSS).每個電平轉換電容使用開關電容電路充電至所需的電平移位電壓,該電路工作在不重疊的互補時鐘q1和q2上[32]。如圖9所示,小型電容器C小充電至所需的電平偏移偏置電壓(V比亞斯普和V比亞森),并且該小電容器定期與電平轉換電容器并聯開關以刷新其電荷,從而建立電平轉換電壓。MDAC放大器的第一級采用主動級聯編碼,兩級均使用獨立的共模反饋電路,以實現更好的共模建立和穩定性。該放大器專為快速線性建立而設計,并針對低功耗進行了優化,這是通過利用減小擺幅、抖動和IGE校準技術實現的。

抖動被添加到兩個 MDAC(使用C抖動圖5所示的電容器)和閃光燈[28]。添加到閃光燈的抖動使殘余IGE誤差和階段1 MDAC殘差中的非線性線性化。添加到MDAC的抖動沿流水線向下傳播,并對后端ADC中的差分非線性(DNL)誤差進行線性化處理。只有MDAC抖動和閃光抖動之間的不匹配才會最終使用校正范圍,并且這些不匹配相對于校正范圍很小。隨機1位發生器(圖5中標記為IGE)驅動電容器CIGE將電荷注入MDAC,用于對MDAC中的IGE進行數字估計[31]。估算后,IGE將在后臺進行數字校正。

B. 前端

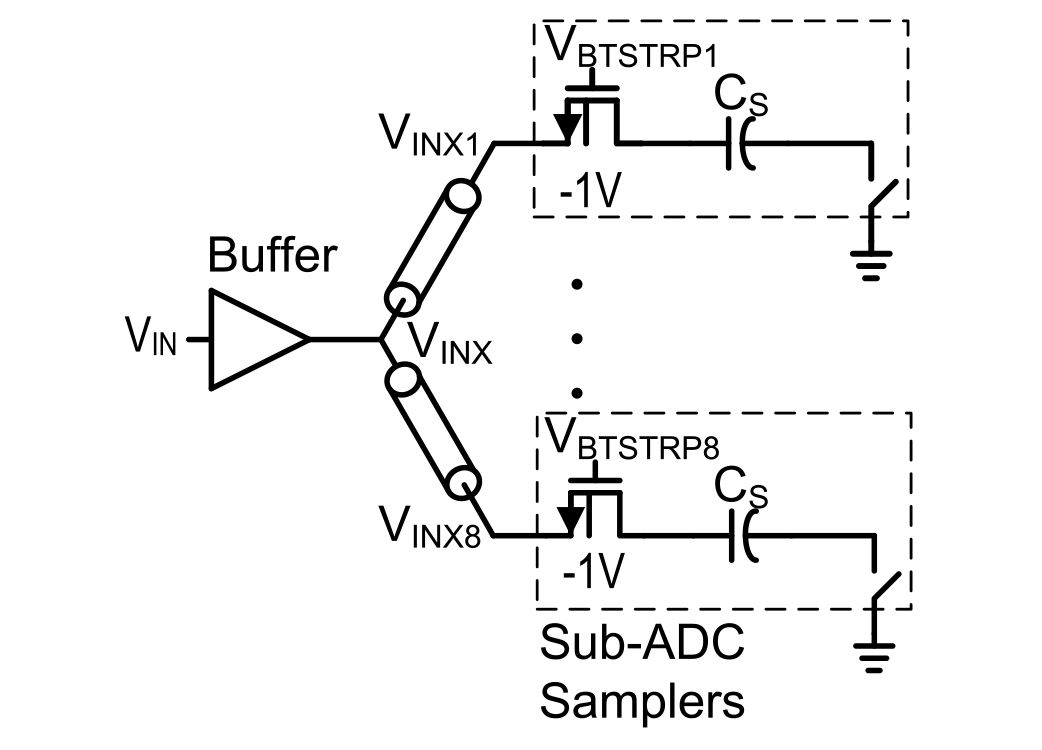

八路IL ADC的前端如圖10所示。圖中顯示了一個公共輸入緩沖器驅動八個子ADC中每個子ADC內的采樣網絡。這將隔離輸入V在從八個子ADC的負載,這改善了帶寬和線性度。為了最大限度地減少輸入緩沖器的負載和子ADC之間的串擾,八個子ADC中只有一個連接到緩沖器并隨時跟蹤緩沖器的輸出。也就是說,只有八個中的一個VBTSTRP[1:8] 隨時打開。七個關斷輸入開關在輸入緩沖器上存在顯著的非線性寄生,會降低高頻線性度,為了減少這種影響,這些輸入開關的后柵偏置至 –1 V 電壓以降低C某人非線性。

在選擇本工作中使用的單個公共輸入緩沖器與驅動八個子ADC中每個子ADC的單獨輸入緩沖器之間存在著權衡。在高頻輸入端實現目標帶寬和線性度的緩沖器的gm和功率由容性負載決定。當緩沖器的負載由采樣電容主導時CS,并且任何時候只有一個子ADC采樣,因此可以爭辯說,單個公共緩沖器的功耗比八個獨立的緩沖器低8×因為當其子ADC采樣時,每個單獨的緩沖器都必須燃燒相同的功率才能提供所需的交流電流,負載CS.然而,實際上,公共緩沖器的功耗并不低8×,因為到8個子ADC和7個關斷輸入開關的金屬布線增加了額外的寄生電容。但是,只要這兩個額外的寄生電容明顯小于7×CS,使用公共緩沖區可以顯著節省凈功耗。此外,對于單獨的輸入緩沖器,總電容呈現為V在也會增加,這將大大降低 BW。基于帶寬、功率和線性度的考慮,本文使用單個公共緩沖器。

圖 9.MDAC1 放大器晶體管級實現細節。

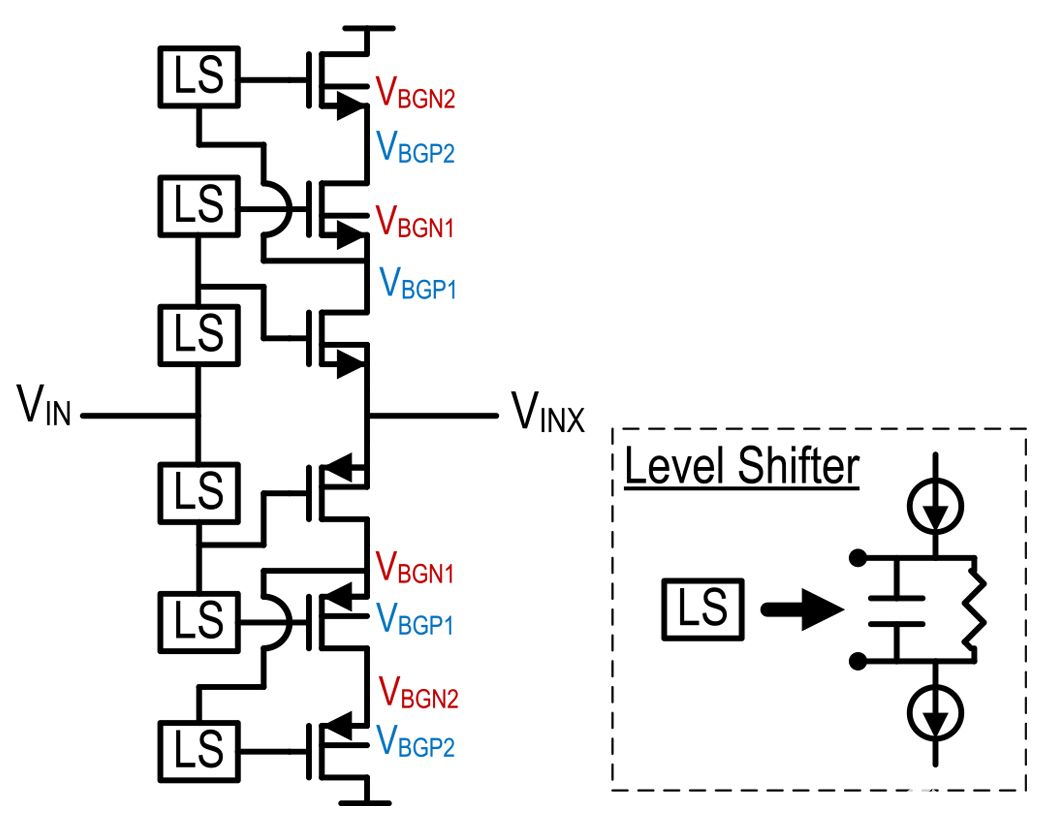

輸入緩沖器實現細節如圖 11 所示。該采用偽差分互補推挽式架構,使gm/I翻倍。然而,推挽式設計需要NMOS和PMOS器件的不同偏置點,這些偏置點是通過電平轉換(LS)電路實現的,該電路由電流源在高值電阻兩端產生偏置電壓,該偏置電壓由大型前饋電容旁路。兩級聯碼自舉到輸入端V在為了減少緩沖器輸入器件的漏極調制,這提高了線性度,但需要為緩沖器使用更高的電源電壓。

圖 10.前端電路顯示驅動八個子ADC采樣器的輸入緩沖器。

輸入緩沖器由2 V和–1 V電源軌供電,每個晶體管均偏置,以確保其飽和約>150 mV。VDS–VDSAT邊緣。而輸入設備和內部級聯直接從輸入驅動V在通過LS電路,外部級聯從內部級聯的源驅動。驅動外部級聯門的另外兩個選擇是輸入V在或緩沖區的輸出V英克斯.這兩種選擇都會降低緩沖器線性度,因為外部級聯碼的漏極未自舉到輸入端,從而在高輸入頻率下產生較大的非線性柵極電流。緩沖器中各種晶體管的后柵是自舉的,如圖11所示,以進一步提高緩沖器線性度。當最內層的輸入器件的后柵極本地連接到源極時,級聯碼的后柵連接到堆棧互補側的等效小信號點,這增加了后柵二極管的反向偏置,從而降低了非線性度。

圖 11.輸入緩沖區實現詳細信息。

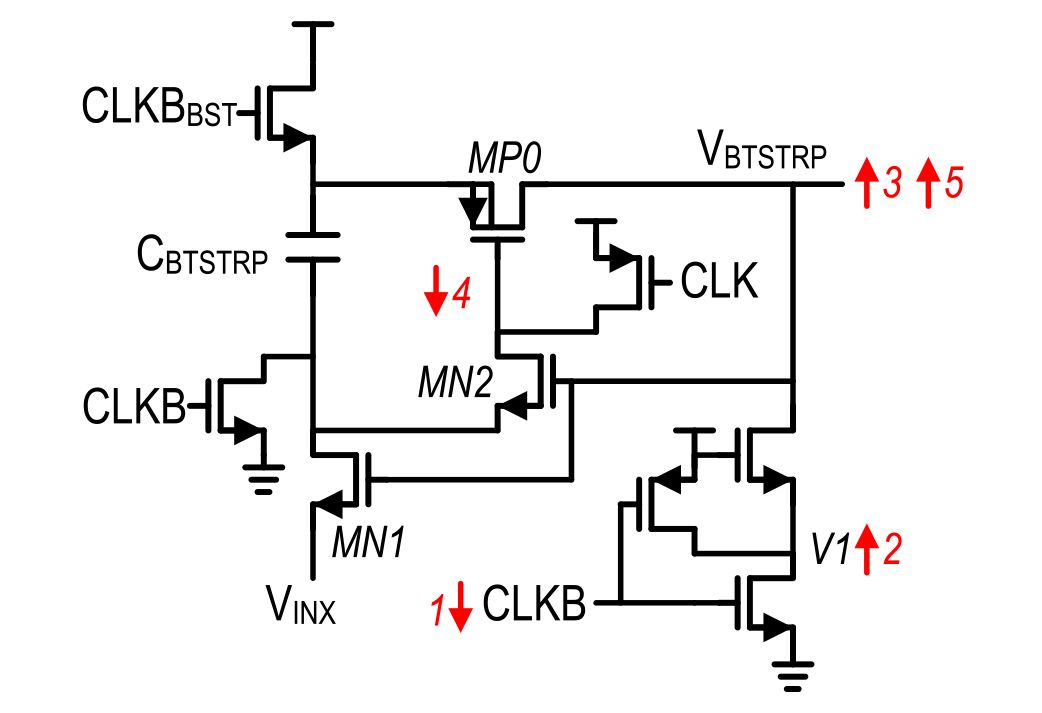

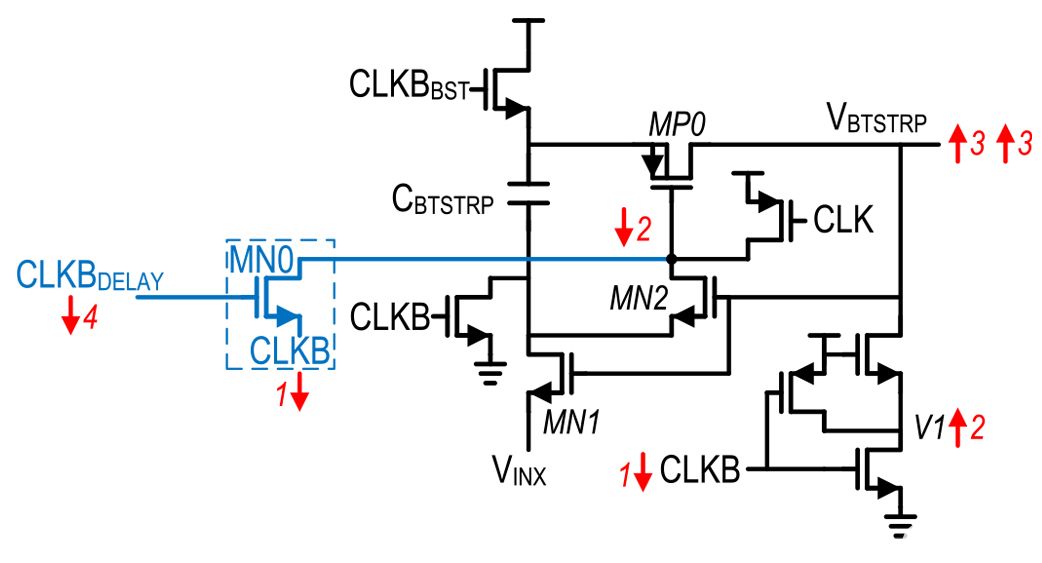

每個子ADC在10 GS/s時分配100 ps,用于跟蹤和采樣緩沖器輸出,因此快速導通自舉開關至關重要。傳統的自舉開關如圖12所示[25]。該開關的操作遵循圖 12 中所示的步驟順序,從 1 到 5。當 CLKB 及其增強版本中新網英國夏令時高,自舉電容CBTSTRP是收費的。當 CLKB 變為低電平時,首先 V1 變為高電平,然后輸出VBTSTRP被弱拉到 VDD-VTHNMOS,后者弱地打開 MN2 和 MN1,從而拉下 MP0 的柵極,最終拉動VBTSTRP通過將其連接到充電的高CBTSTRP電容器。這是開啟期間的正反饋電路,所以一次VBTSTRP足夠高,MN1和MN2強烈拉動MP0的柵極,直到整個電路達到自舉穩態操作。請注意,如果MP0的門可以在序列的早期拉低,則可以提高此自舉發生器的開啟速度。

圖 12.傳統的自舉開關柵極驅動生成電路[25]。

圖 13.自舉開關柵極驅動生成電路,增加了快速啟動電路。

在這項工作中,這是通過添加一個單獨的晶體管MN0來實現的,當CLKB變低時直接拉下MP0的柵極,如圖13所示。但是,如果 MN0 在 MN1 和 MN2 完全導通時保持導通狀態,則會通過向輸入端提供低阻抗來中斷自舉操作V英克斯.為了避免這種爭用,MN0 被 CLKB 的延遲版本關閉,中新網延遲,從而在加速自舉電路導通后使 MN0 不再影響自舉操作。

C. 順序交錯和隨機交錯

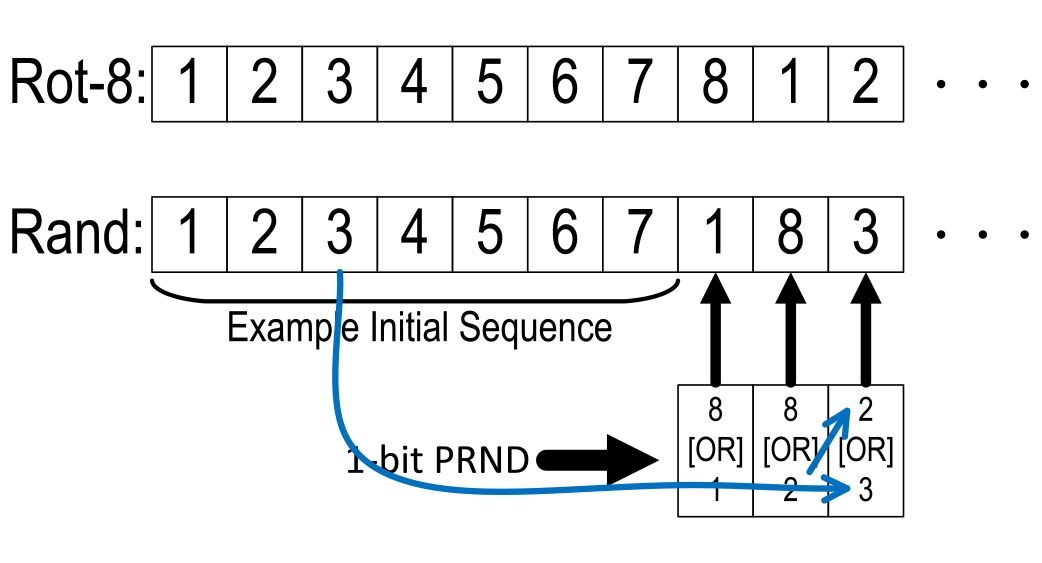

IL ADC通常以順序(旋轉)模式在子ADC之間循環。圖3中的8個子ADC對輸入信號進行采樣V在按順序旋轉八順序模式,如圖14上半部分的子ADC選擇模式所示。對于順序交錯,子ADC之間的任何不匹配都會導致頻譜中的雜散,如本節前面所述,本工作中對此進行了校準。然而,盡管進行了校準,殘留交錯雜散仍然存在,因為這些交錯雜散對校準后仍未校正的失配具有非常高的敏感性。此外,一些二階交錯失配(如子ADC之間的線性度失配)由于其復雜性而未進行校準。對于大信號輸入,具有交錯失配校準的順序IL ADC的SFDR通常受到采樣失真引起的HD2或HD3雜散的限制。

圖 14.交錯子ADC選擇模式,用于順序和隨機工作模式。

然而,隨著輸入信號變小,HD2和HD3通常分別隨著信號的平方和立方減小而改善,因此小信號SFDR會很快受到殘余交錯雜散的限制,這對于許多寬帶應用來說是不希望的。此外,在某些應用中,HD2和HD3雜散可能被規劃為落在目標目標頻帶之外,但殘余交錯雜散可能落在帶內,這同樣是不希望的。

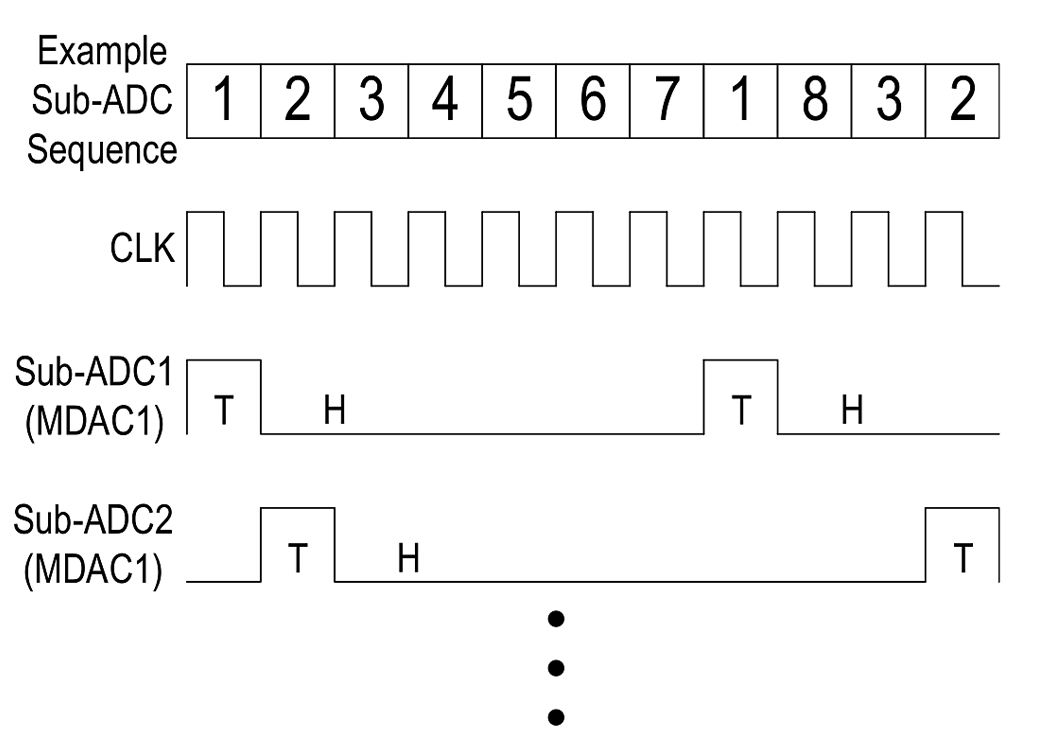

為了克服這種殘余交錯雜散限制,這項工作包括以全10 GS/s采樣速率隨機化子ADC選擇模式的能力。隨機化有助于將任何殘余交錯雜散轉換為噪聲,從而產生更清晰的頻譜,代價是本底噪聲的增加。為了實現隨機化,八個子ADC中的每一個都設計為以1.43 GS/s [=(10 GS/s)/7]運行,因此在七個時鐘周期后,子ADC再次可供選擇。這種冗余導致兩個子ADC隨時可供選擇,這兩個子ADC之間的選擇由1-b隨機發生器(偽隨機或PRND)控制。圖14的下半部分以圖形方式描述了隨機選擇序列。假設初始起始序列為1到7,則對于第8個采樣,子ADC 8和1均可用。例如,如果PRND為第8個樣本選擇子ADC 1,則子ADC 8保留在堆棧中的相同位置,子ADC 2被添加到堆棧中。對于第 9 個樣本,如果選擇了子 ADC 8,則子 ADC 2 將取代其位置,子 ADC 3 將取代堆棧中的子 ADC 2。在子ADC轉換后,樣本以正確的順序重新組裝,從而反轉隨機加擾序列。示例子ADC選擇序列的子ADC內的時序如圖15所示,其中MDAC1跟蹤(T)輸入信號一個周期,然后采樣并保持(H)至少六個周期,其中包括生成閃存數據和MDAC放大以產生殘余所需的時間[28]。隨機化時,增益、失調和時序失配的 IL 校準算法保持不變。為了估計時序偏差,前面提到,在給定的子ADC輸出和緊隨其后的樣本之間執行相關性,隨機化時,其他七個子ADC中的每一個都會隨機產生相關性。平均而言,即使在隨機化時,這種相關性仍然可以準確估計給定子ADC的時序偏差。

圖 15.各個子ADC相對于整個子ADC選擇模式的時序圖。

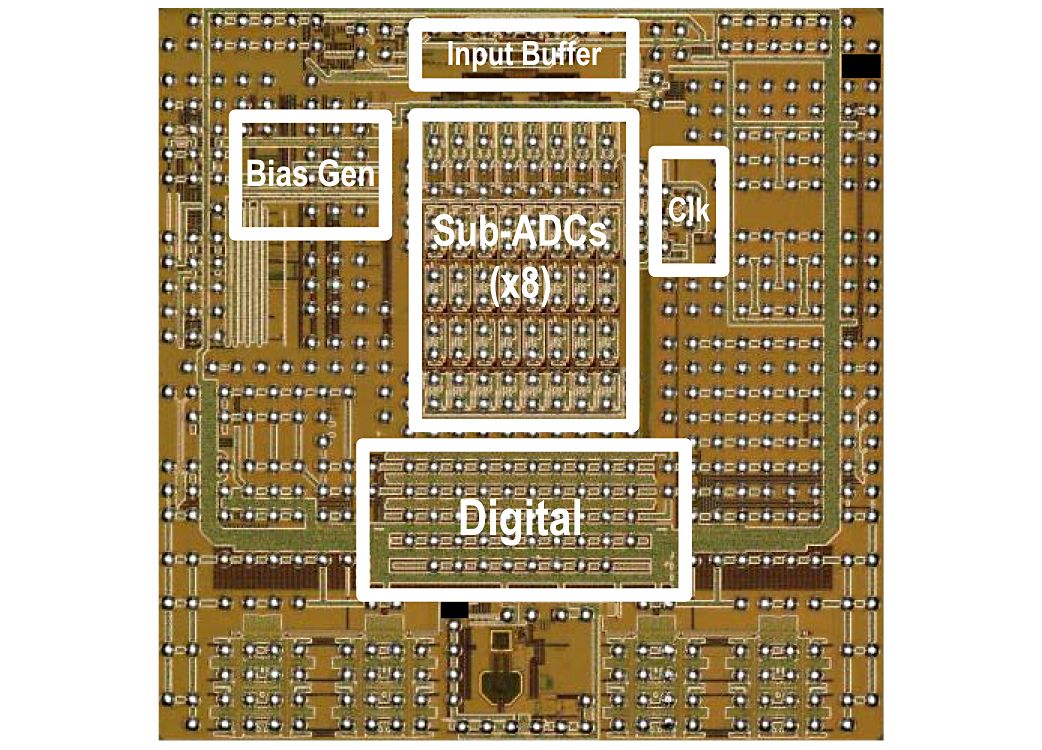

圖 16.模具照片 - 突出顯示區域:7.4 平方毫米,模具尺寸 4.5 毫米× 4.5 毫米。

測量結果

12-b 10-GS/s ADC 采用 28 納米 CMOS 技術制造。ADC的芯片照片如圖16所示,突出顯示了芯片的關鍵部分。輸入緩沖器位于頂部,其次是其下方的八個IL子ADC,然后是數字。時鐘接收器和所有時鐘相位發生電路位于右側,偏置發生位于左側。

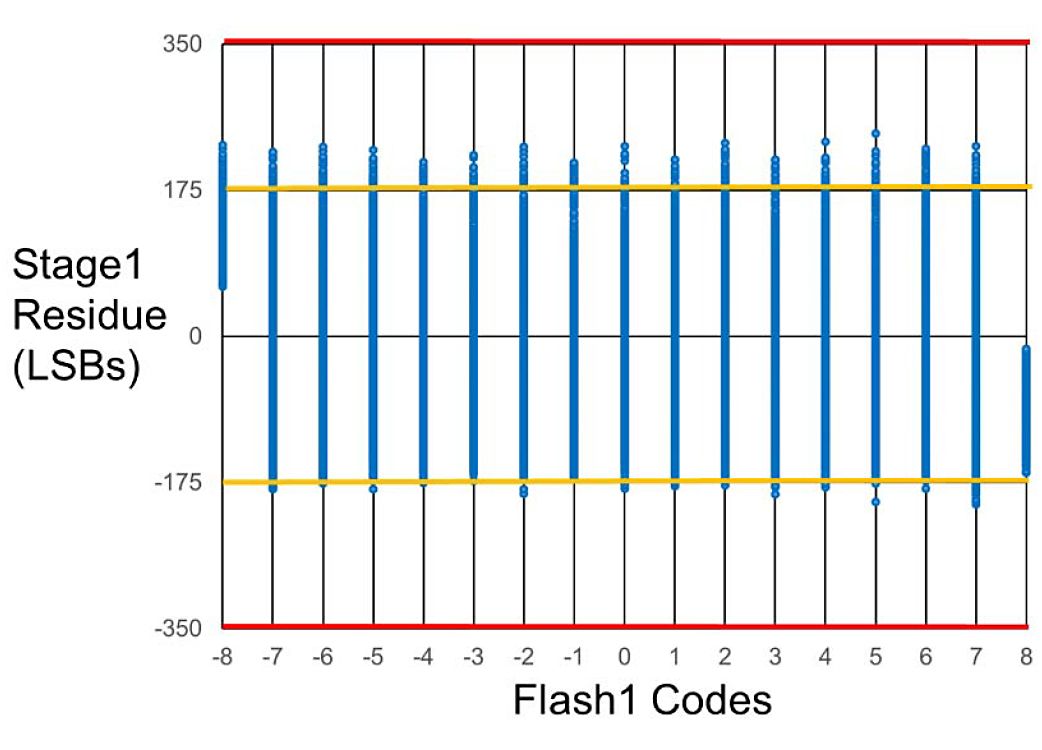

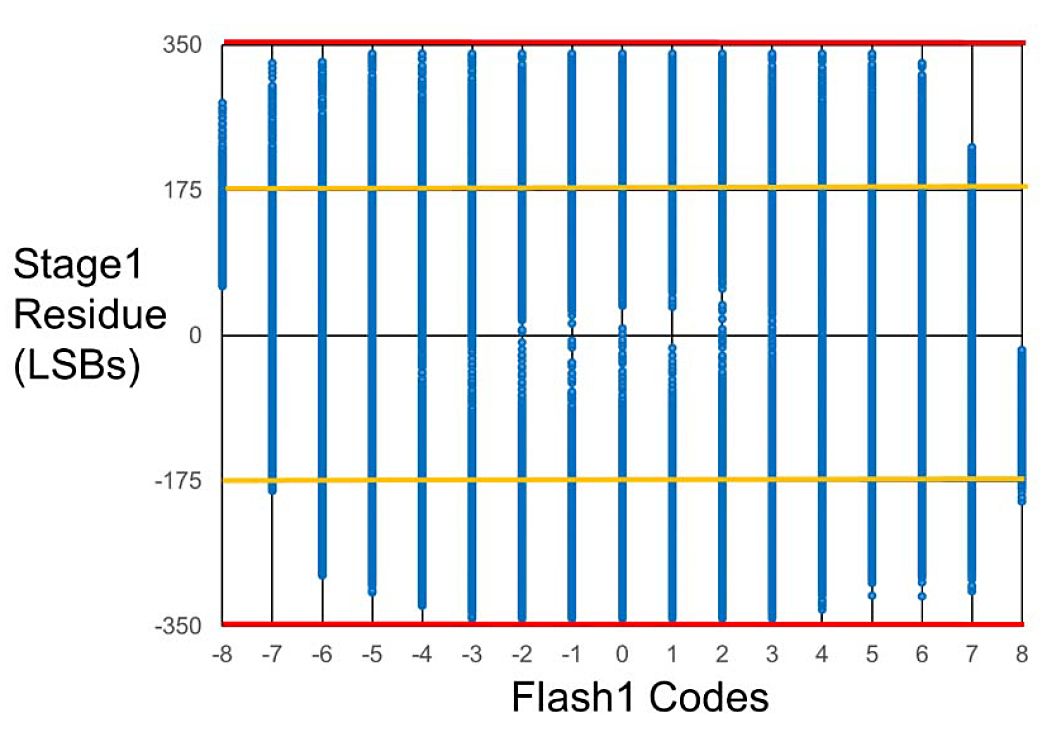

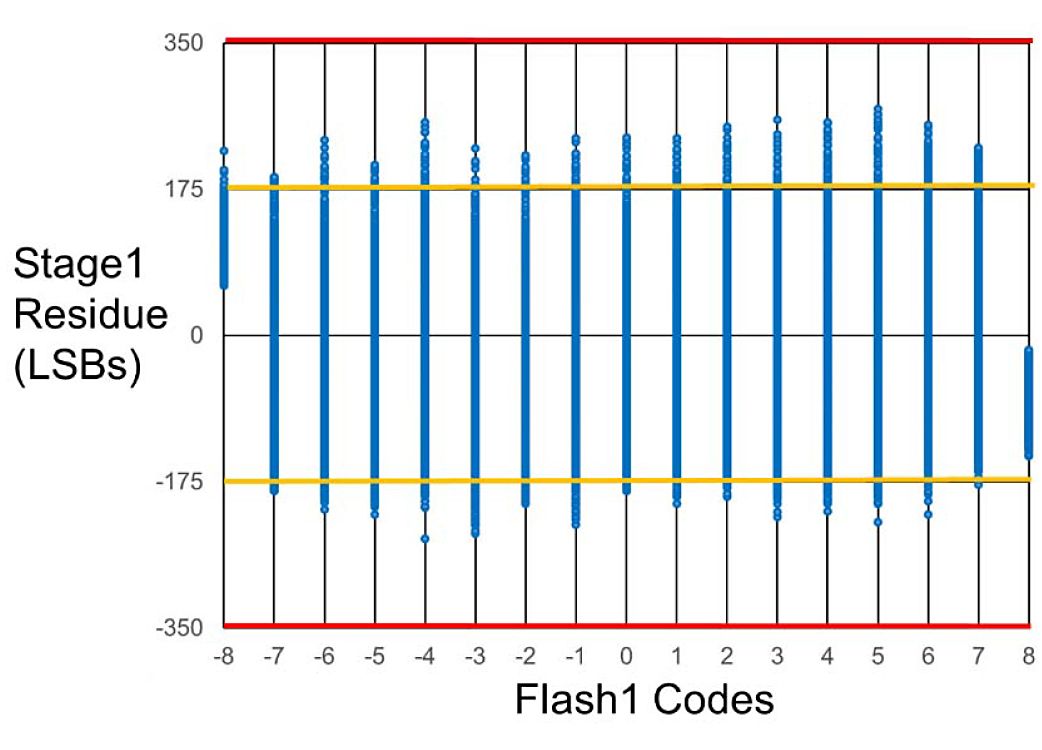

圖17顯示了其中一個子ADC測得的數字Stage1殘余傳遞函數(DSRTF),后端(級2至5)代碼在y軸上,flash1輸出代碼在x軸上。啟用閃光比較器背景偏移校準后,校正范圍的大部分仍未使用。接下來,圖18顯示了DSRTF以及ADC在對4 GHz信號進行采樣之前使用的所有校正范圍,然后對閃存采樣時鐘延遲進行微調以匹配MDAC。最后,圖19顯示了經過調整的閃光采樣時鐘延遲的DSRTF,即使輸入信號為4 GHz,校正范圍的大部分仍未使用。

圖 17.使用低頻 (127 MHz) 輸入和 flash1 背景校準測量的 DSRTF。

圖 18.使用高頻 (4 GHz) 輸入測量的 DSRTF,無閃存 1 采樣時鐘延遲調整。

圖 19.使用高頻 (4 GHz) 輸入和 flash1 采樣時鐘延遲調整測量的 DSRTF。

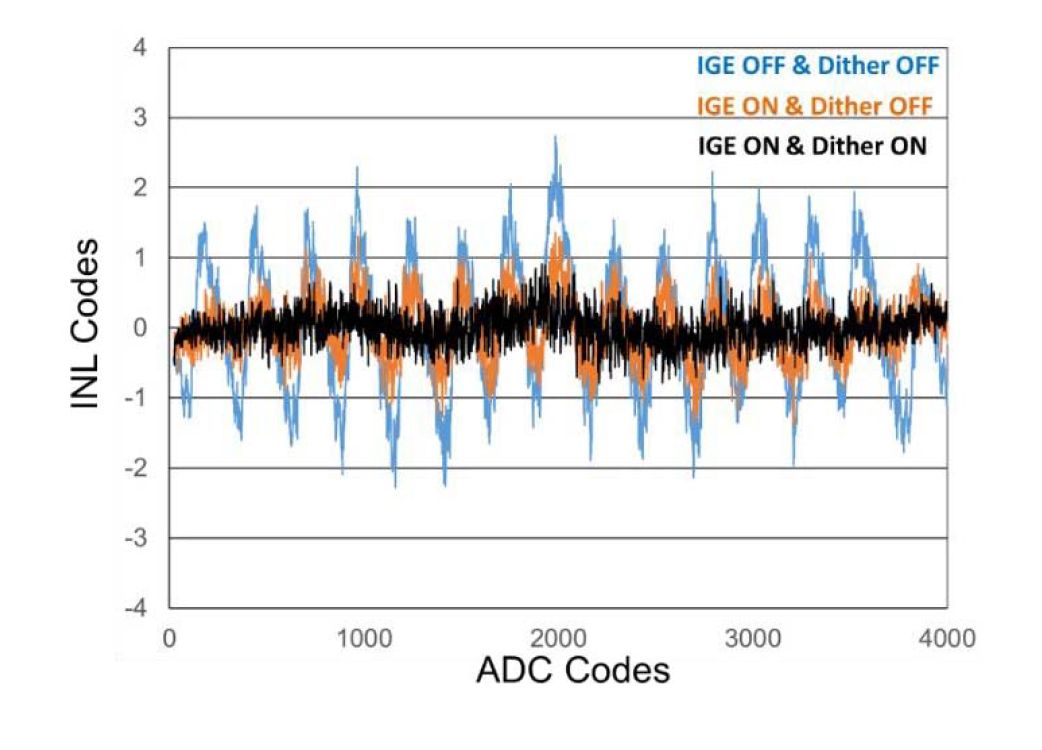

圖20顯示了三種情況下八個子ADC之一的實測積分非線性(INL)傳遞函數。禁用 IGE 校準和抖動后,INL 的連續性超過 ±2 LSB。啟用 IGE 校準后,可將不連續性降低到約 ±1.5 LSB。最后,還啟用了抖動,INL小于±0.7 LSB。 抖動和IGE校準可顯著改善子ADC線性度,并確保INL傳遞函數平滑。擁有沒有傳遞函數不連續性的線性子ADC是實現良好交錯性能的先決條件。

圖 20.測量的子ADC INL傳遞函數,帶或不帶抖動和IGE校準。

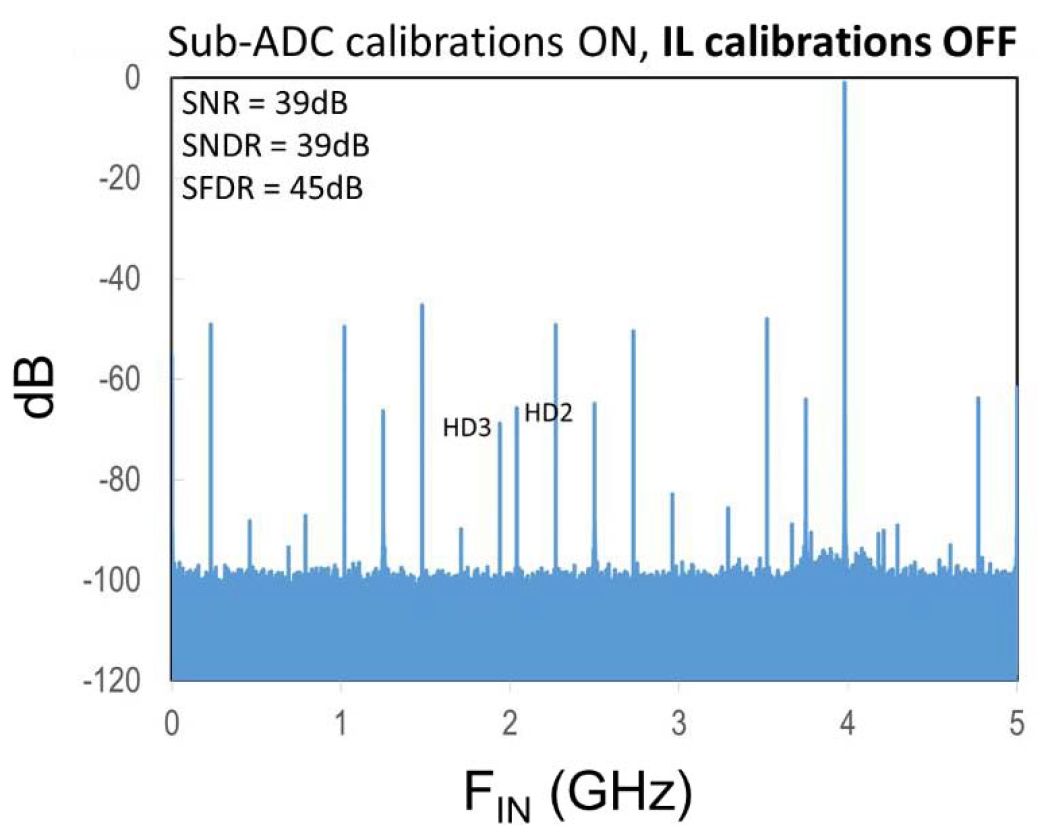

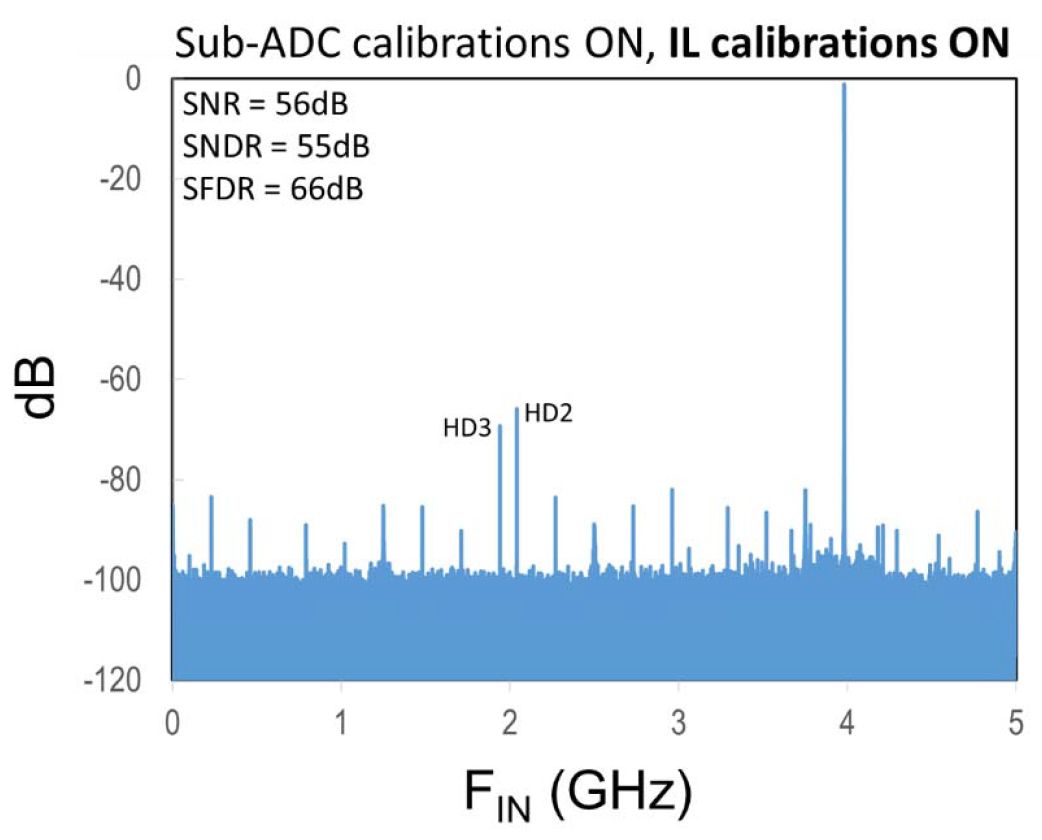

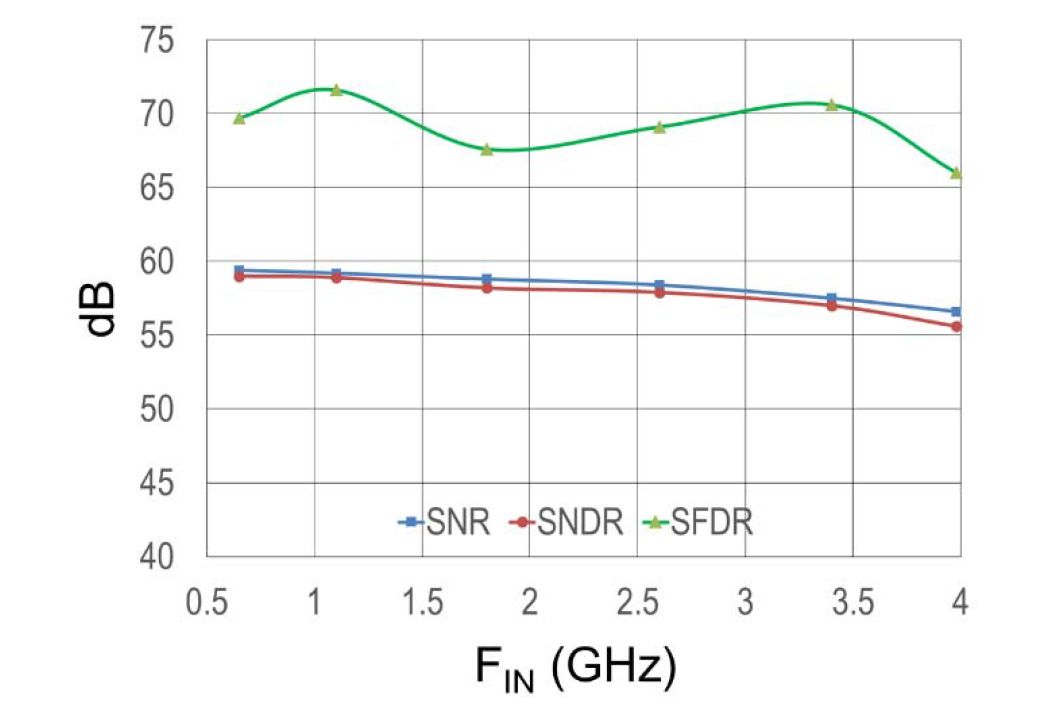

圖21顯示了IL ADC以10 GS/s的速度對4 GHz輸入信號進行采樣的快速傅里葉變換(FFT),子ADC校準和抖動已啟用,但沒有交錯校準。頻譜顯示較大的交錯失配雜散,限制了SFDR。如圖22所示,啟用交錯校準時,交錯失配雜散降低到80 dB以下,SFDR受HD2限制為66 dB,HD3限制為69 dB,而實現的SNR為56 dB,SNDR為55 dB。SNR、SNDR和SFDR的輸入頻率掃描如圖23所示。表I總結了這款12-b 10-GS/s ADC的性能規格,并列出了Schreier FOM (FOMS_HF)和Walden FOM (FOMW_HF) [8]。

| Resolution | 12b |

| FSAMPLE | 10GS/s |

| SNR | 56dB |

| SNDR | 55dB |

| SFDR | 66dB |

| 66dB | 4GHz |

| Power | 2.9W |

| FOMS_HF | 147dB |

| FOMW_HF | 631fJ/Conv-Step |

| BW | 7.4GHz |

| DR | 60dB |

| NSDsmall-signal | -157dBFS/Hz |

| Technology | 28nm |

圖 21.在禁用 IL 校準的情況下,以 10 GS/s 的速度測量 ADC FFT,輸入為 4 GHz。

圖 22.在 10 GS/s 下測量 ADC FFT,輸入為 4 GHz,啟用 IL 校準。

圖 23.測得的ADC輸入頻率掃描速度為10 GS/s。

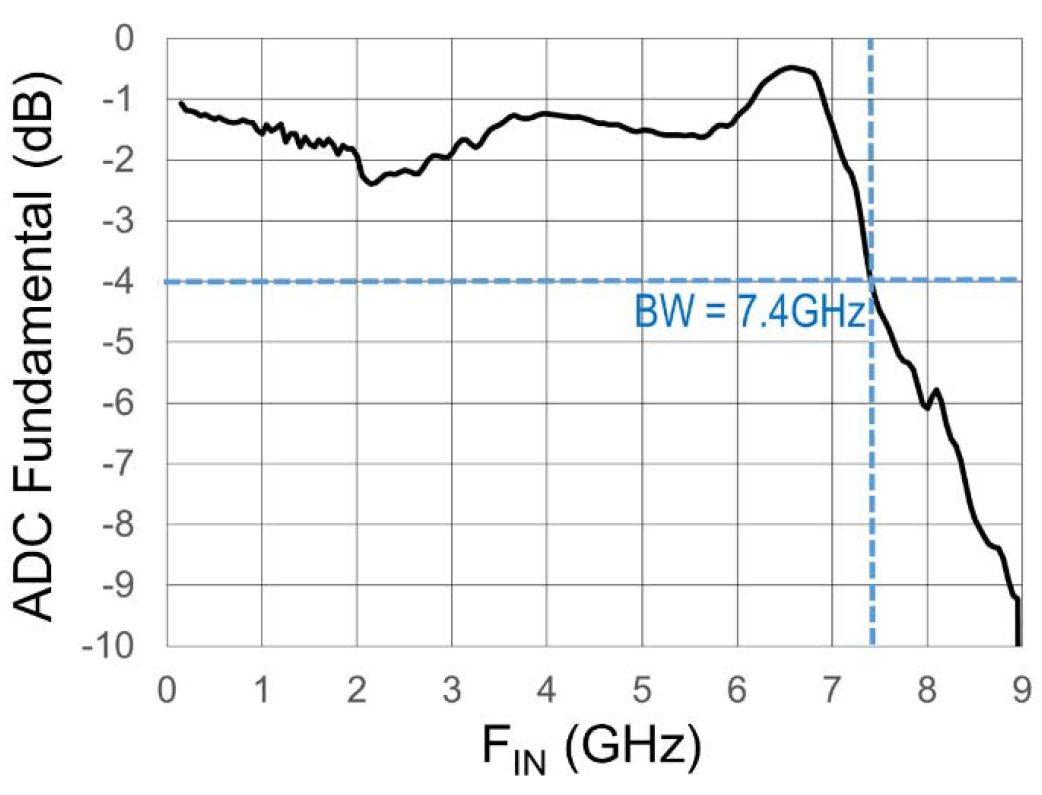

圖24顯示了該ADC測得的–3 dB帶寬,約為7.4 GHz。決定帶寬性能的主要電路是前端推挽輸入緩沖器和扇出驅動每個子ADC內的采樣網絡。

圖 24.測得的ADC輸入帶寬。

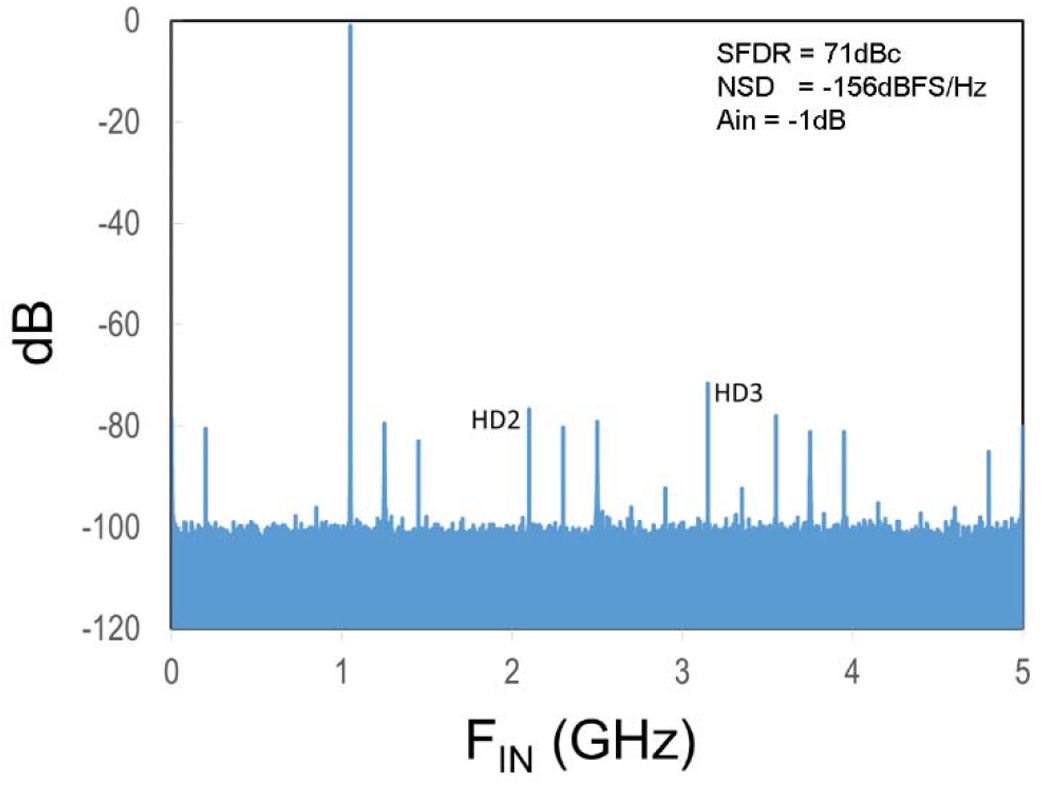

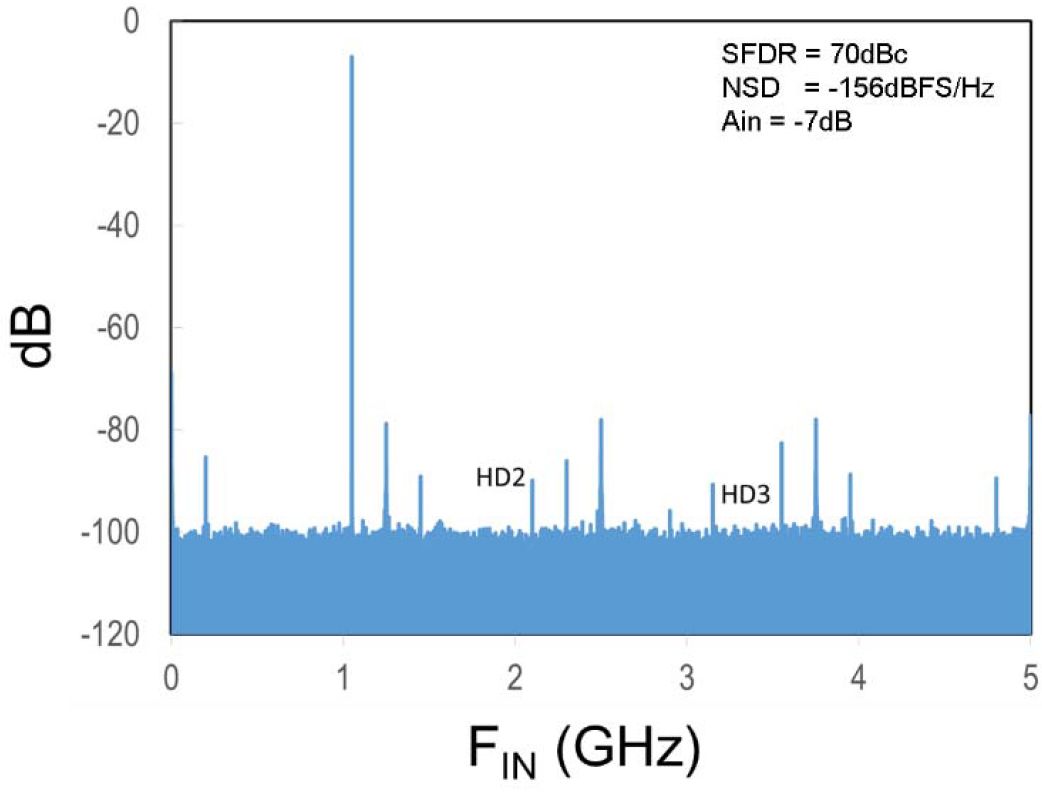

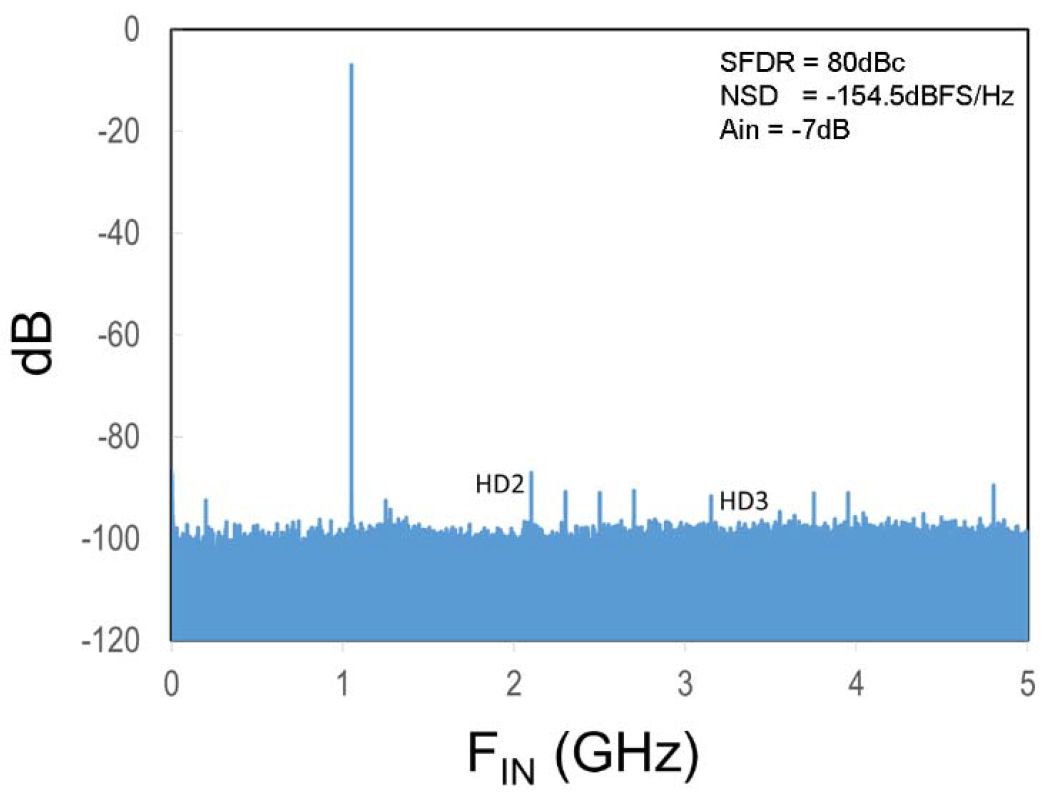

如第III-C節所述,該ADC能夠隨機選擇子ADC,通過降低殘余交錯雜散的幅度來提高頻譜性能。為了解釋隨機化的影響,接下來顯示了一系列測量的FFT光譜。圖25顯示了ADC的FFT,該FFT以10 GS/s的速度順序采樣接近滿量程的1 GHz信號,其中SFDR受HD3分量限制為71 dBc,交錯失配雜散通過校準抑制至80 dB電平。然而,如圖26所示,當輸入信號幅度下降6 dB時,HD2和HD3通過信號減小的平方和立方而改善,而SFDR現在被交錯失配雜散限制在70 dBc,這是不希望的,因為許多應用期望SFDR在較小的信號幅度下得到改善。現在,當啟用子ADC的隨機化時,如圖27所示,這些殘余交錯失配雜散被拖入本底噪聲,對于所示情況,SFDR提高了10 dB至80 dBc,而代價是NSD降低1.5 dB。

圖 25.帶滿量程信號的順序 IL 10-GS/s FFT。

圖 26.順序 IL 10-GS/s FFT 顯示具有小量程信號的主要殘余 IL 音調。

圖 27.隨機 IL 10-GS/s FFT 顯示小量程信號的殘余 IL 音調減少。

最后,ADC在10 GS/s時的功耗為2.9 W,其中輸入緩沖器約400 mW,8個子ADC為1800 mW,時鐘和數字為650 mW,基準電壓源和偏置生成功耗為50 mW。

圖 28.SNDR ≥ 50 dB 的 ADC 的施賴爾 FOM(在包含 ISSCC 2017 數據后從 [8] 過濾)。

與先進ADC的比較

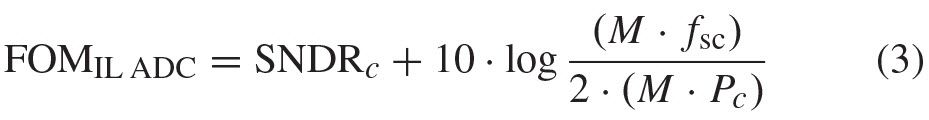

施賴爾FOM(如(1)所示)用于比較該12-b 10 GS/s ADC與文獻中其他ADC的性能。圖28顯示了基于Murmann [8]數據的FOM比較圖,其中ADC已按SNDR = 50 dB條件進行濾波,表II將這項工作與最近發布的ADC與最近發布的ADC進行了比較fS= 圖 28 中的 2.5 GS/s。這項工作在28納米CMOS中實現了[5]和[33]的采樣率幾乎兩倍,同時實現了類似的FOM。雖然[21]和[34]在16納米CMOS中實現了更好的FOM,但它們比這項工作慢2.5×。幾乎所有這些ADC都使用IL流水線架構。表 II 中這些 IL 流水線 ADC 使用的工藝技術范圍為 130 nm BiCMOS 至 16 nm CMOS。

| 規范 | 這項工作 | [5] 阿里 | [33] 吳 | [21] 吳 | [22] 施泰耶 | [34] 瓦茲 | [35] 陳 | [20] 塞特伯格 |

| FSAMPLE | 10GS/秒 | 5GS/秒 | 5.4GS/秒 | 4GS/秒 | 4GS/秒 | 4GS/秒 | 3GS/秒 | 2.5GS/秒 |

| 輸入鰭片 | 4千兆赫 | 2千兆赫 | 2.7千兆赫 | 1.9千兆赫 | 1.8千兆赫 | 1.9千兆赫 | 1.5千兆赫 | 1千兆赫 |

| SNDR @ fin | 55分貝 | 58分貝 | 50分貝 | 56分貝 | 56分貝 | 57分貝 | 51分貝 | 61分貝 |

| SFDR @ 鰭 | 66分貝 | 70分貝 | 65分貝 | 68分貝 | 64分貝 | 67分貝 | — | 78分貝 |

| 功率 (W) | 2.9 | 2.3 | 0.5 | 0.3 | 2.2 | 0.5 | 0.5 | 24 |

| FOMS @ fins | 147分貝 | 148分貝 | 147分貝 | 154分貝 | 145分貝 | 153分貝 | 146分貝 | 138分貝 |

| BW | 7.4千兆赫 | 5千兆赫 | — | — | 4千兆赫 | — | — | — |

| 過程 | 28納米 | 28納米 | 28納米 | 16納米 | 65納米 | 16納米 | 40納米 | 130納米雙氯合金 |

| 建筑 | IL 管材 | IL 管材 | IL 管材 | IL 管材 | IL 管材 | IL 管道/SAR | IL 管材 | IL 管材 |

總結和結論

本文介紹了一種 12-b 10GS/s ADC,該 ADC 在 28 nm CMOS 技術中交織了 8 個流水線子 ADC。無SHA流水線子ADC(包括MDAC放大器)采用內核電源供電,以實現低功耗,這是通過殘余縮放、閃存背景校準、抖動和IGE校準等技術實現的。在IL ADC中實現帶寬和線性度的挑戰可通過推挽互補輸入緩沖器來驅動IL子ADC,快速自舉開關可實現10 GS/s采樣操作。交錯不匹配通過背景校準技術解決。隨機選擇子ADC可減少殘余交錯雜散。

-

CMOS

+關注

關注

58文章

5995瀏覽量

238134 -

轉換器

+關注

關注

27文章

8963瀏覽量

150811 -

adc

+關注

關注

99文章

6644瀏覽量

548322 -

無線電

+關注

關注

60文章

2162瀏覽量

117685

發布評論請先 登錄

流水線ADC結構解析 流水線ADC和其它ADC的比較

如何設計一個適用于12bit流水線ADC采樣保持電路?

流水線ADC

流水線ADC的行為級仿真

用于低噪聲CMOS圖像傳感器的流水線ADC設計及其成像驗證

12bit200MSPS時間交織流水線ADC研究與設計

了解流水線型ADC

什么是流水線 Jenkins的流水線詳解

ADS5413 CMOS流水線模數轉換器(ADC)數據表

評論