一、開發板簡介

MP5610開發板搭載主控Altera FPGA芯片 CycloneⅤ 5CGXFC5C6F27C7N、海思HI3536V100、兩片鎂光DDR3芯片MT41J128M16JT-125、四片海力士DDR3芯片H5TQ4G63CFR-RDC、電源管理芯片TPS51100DGQ、TPS54284PWP、SDI輸入芯片LMH0344、HDMI輸入芯片ADV7610、HDMI輸出芯片ADV7513、D/A轉換芯片ADV7123、PHY芯片AR8031、USB芯片FT602Q等,是具有多種視頻輸入接口、多種視頻輸出接口、具備H.264視頻流解碼和USB3.0視頻信號輸出功能的FPGA開發板。開發板輸入端具有CVBS視頻輸入接口、HDMI視頻輸入接口、3G-SDI視頻輸入接口以及帶H.264視頻流解碼功能的千兆以太網視頻輸入接口,輸出端具備HDMI高清數字信號視頻輸出接口、VGA模擬信號視頻輸出接口、USB3.0視頻信號輸出接口和千兆以太網同學接口。

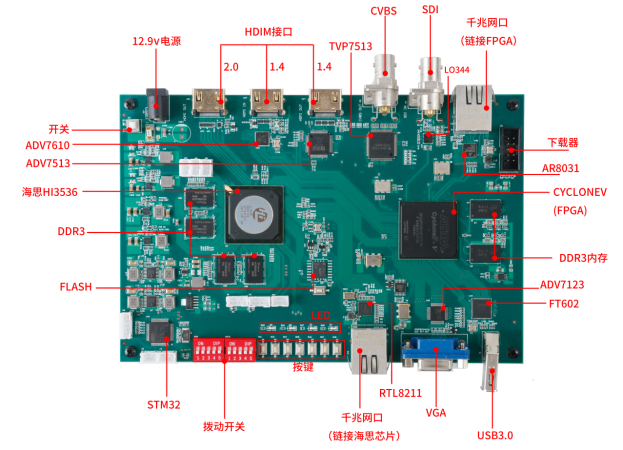

開發板成品圖如下圖1所示

通過上圖,我們可以看到,我們這個開發板上所有的接口。

1. FPGA

Altera FPGA芯片 CycloneⅤGX 5CGXFC5C6F27C7N。

2. DDR3

FPGA芯片連接有兩片大容量的2048M字節(共2GB)的鎂光DDR3-1600高速SDRAM,作為FPGA的數據存儲、圖像分析緩存、數據處理緩存。海思芯片連接有4片大容量的4096M字節(共16GB)的海力士DDR3高速SDRAM。

3. HDMI

低功耗、165Mhz HDMI接收芯片ADV7610和165Mhz高性能HDMI發送芯片ADV7513。

4. 視頻解碼器單芯片數字視頻解碼器TVP5146。支持RGB和YPbPr信號的模數轉換,支持NTSC、PAL和SECAM復合等的A/D轉換和解碼。

1. 千兆以太網接口

與FPGA相連的千兆以太網芯片為AR8031,與海思芯片相連的千兆以太網芯片為RTL8211。

2. VGA接口

采用數模轉換芯片ADV7123。330MSPS吞吐率、三倍10bit高速視頻數模轉換器。

3. USB3.0

USB視頻類橋芯片FT602,支持USB3.1 GEN 1超級速度(5Gbps)/USB 2.0高速(480Mbps),支持USB傳輸類型:控制/批量/中斷,支持多達四個視頻輸入通道。內置16KB FIFO數據緩沖RAM和IIC主接口,用于視頻設備配置。

4. 海思芯片

海思譯碼處理器HI3536。包括用于運行外圍驅動程序和應用程的主控處理器內核ARM Cortex A17 quad-core@maximum 1.4Ghz、用于相關視頻模塊控制的處理器內核ARM Cortex A7 single-core@maximum 900MHz。

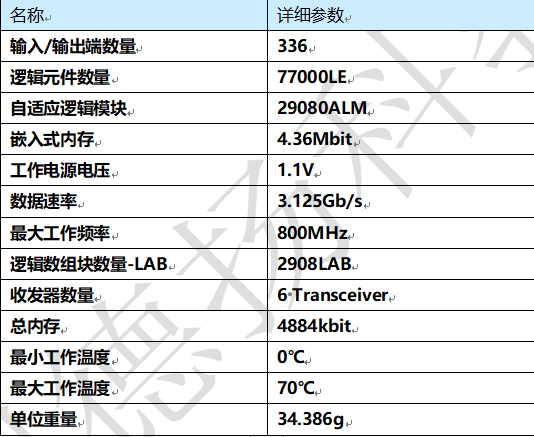

二、 FPGA芯片

開發板使用的是Altera 的CycloneⅤGX芯片,芯片型號為5CGXFC5C6F27C7N。邏輯元件數量77000LE,數據速率3.125Gb/s,最大工作頻率800MHz。此型號為FBGA-672封裝,輸入輸出端共336個。

CycloneⅤGX FPGA芯片實物圖

CycloneⅤGX 5CGXFC5C6F27C7N的主要參數表:

三、DDR3 SDRAM

MP5610發板上配有6片DDR3芯片。

其中兩片鎂光的DDR3 SDRAM芯片型號為MT41J128M16,存儲容量為16Meg*16*8Banks(2Gb),具體參數如下表:

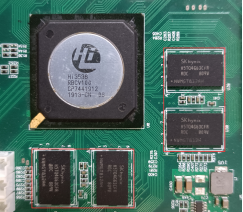

開發板中所在位置:

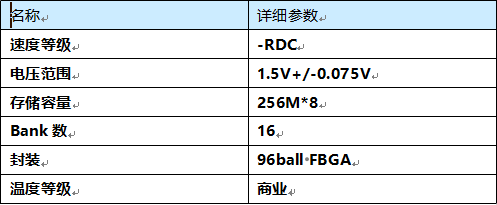

片海力士的DDR3 SDRAM芯片型號為H5TQ4G63CFR,是一個4294967296bit CMOS雙倍數據速率的同步DRAM,非常適合需要大內存密度和高帶寬的主存儲器應用,數據路徑內部流水線化,8位預取,帶寬非常高。具體參數如下表:

開發板中所在位置:

DDR3引腳分配詳見MP5610引腳配置表。

四、HDMI

HDMI接收采用ADV7610芯片,工作溫度范圍是-40℃~+85℃,是一款高質量的單輸入的HDMI接收器,支持HDMI規范中定義的所有的強制性3D TV。支持8位UXGA 60hz的格式,集成了CDC特性的CEC控制器。同時,ADV7610有一個四通道立體聲音頻輸出端口,用于從HDMI流中提取音頻數據,HDMI接收器有一個先進的靜音控制器,防止可聽的外部噪音在音頻中輸出。包含一個主組件處理器(CP),處理來自HDMI接收器的視頻信號,提供了對比度、亮度、飽和度調整、STDI檢測塊和同步對齊控制。采用先進的CMOS工藝制作,尺寸為6mm*6mm,封裝采用76ball CSP_BGA,通過無鉛認證。

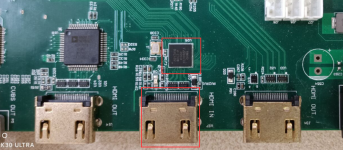

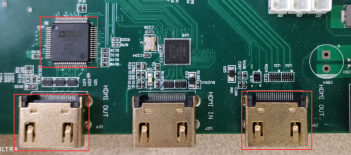

下面為實物圖:

HDMI發送采用ADV7513,它是一種165MHz、高清多媒體接口發送機,是DVD播放器/錄音機、數字機頂盒、a/v接收器、游戲機和pc的理想選擇。包含一個兼容HDMI v1.4/DVI v1.0的發射機,支持所有的HDTV格式。ADV7513支持HDMI v1.4特有的功能,包括3D視頻。ADV7513還支持x.v.Color,高比特率(HBR)音頻,和可編程輔助視頻信息(AVI)信息幀功能。ADV7513允許安全傳輸由HDCP v1.4協議指定的受保護的內容。

實物圖如下:

HDMI輸入輸出引腳配置詳見MP5610引腳配置表。

五、視頻解碼器

MP5610開發板具備視頻流解碼的功能,該功能由TVP5146數字視頻解碼芯片實現。TVP5146解碼器支持RGB和YPbPr組件信號的模數轉換,支持NTSC、PAL、SECAM復合和S-video組件YCbCr的A/D轉換和解碼。該芯片內部主要模塊包括:弱噪聲的魯棒同步檢測以及錄像機技巧模式、增益控制、亮度處理器、彩色信號處理器、組件的處理器、時鐘/定時處理器和電源控制、軟件控制節電待機模式、輸出格式化程序、IIC主機端口接口、VBI數據處理器。

實物圖如下:

TVP5610引腳配置詳見MP5610引腳配置表。

六、千兆以太網

MP5610開發板上有兩個千兆以太網通訊接口,一個與FPGA芯片相連,一個與海思芯片相連,可通過網線與PC連接,進行網口通信。

與FPGA相連的AR8031是高通的第四代,單端口,10/100/1000Mbps以太網物理層。它支持與mac的RGMII和SGMII接口。AR8031為廣泛的應用提供低功耗、第BOM成本解決方案,包括企業、運營商和家庭網絡、SFP模塊和介質轉換器。AR8031具有以下特點:

(1、 SGMII和RGMII MAC接口支持

2、 高通公司設計的綠色以太網(EDGE)節電技術

3、 光纖支持100 BASE-X和100 BASE-FX故障檢測

4、 集成MDI終端電阻器

5、 完全IEEE 802.3az支持

6、 支持高達10k字節的Jumbo幀

7、 具有恢復時鐘輸出的同步以太網支持

8、 單臺3.3V電源)

與海思開發板相連的RTL8211E是Realtek瑞昱推出的一款高集成的網絡接收PHY芯片,通過CAT 5 UTP電纜及CAT 3 UTP電纜傳輸網絡數據,該芯片在網絡通信中屬于物理層,用于MAC與PHY之間的數據通信。主要用于網絡接口適配器、網絡集線器、網關以及一些嵌入式設備中。RTL8211E的主要功能特性包括:

(1、 滿足10/100/1000Base-T IEEE802.3ab標準

2、 支持IEEE 802.3 RGMII接口

3、 支持網絡喚醒功能、中斷功能

4、 支持交叉檢測及自動校正

5、 支持半工、全工操作

6、 1000M通信用CAT 5網線可達到120M

7、 可提供三種網絡狀態的LED指示

8、 RGMII接口可支持3.3v、2.5v、1.8v、1.5v信號)

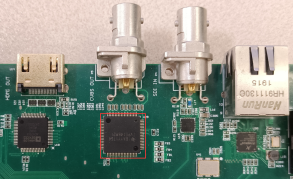

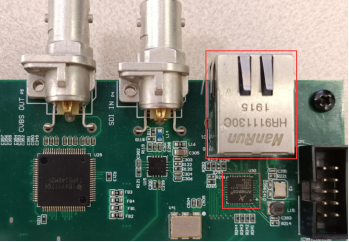

開發板的千兆以太網口實物如下圖所示:

千兆以太網的管腳分配詳見MP5610的管腳配置表。

七、D/A轉換芯片

MP5610開發板板載一片ADV7123數模轉換芯片連接VGA接口,該芯片是一個單片芯片上的三倍高速數模轉換器。它由三個具有互補輸出的高速10bit視頻dac、一個標準TTL輸入接口和一個高阻抗模擬輸出電流源組成。ADV7123有三個獨立的10bit的輸入端口。為保證所有組件正常工作,必須提供5v或者3.3v的電源和時鐘。有獨立的視頻控制信號,具有省電模式。采用5V CMOS制備工藝,單片的CMOS結構確保有更大的功能和更低的功耗。

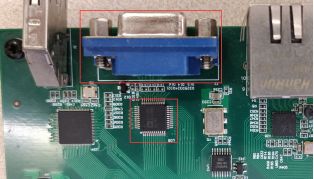

開發板的ADV7123以及VGA接口實物如下圖所示:

ADV7123的管腳分配詳見MP5610的管腳配置表

八、海思芯片

MP5620開發板板載一枚HI3536,是針對多通道高清或D1 NVR的專業高端Soc。Hi3536提供高性能的a-17處理器、視頻解碼引擎(支持各種協議最大16*1080p解碼)、高性能的視頻/圖形處理引擎(支持各種復雜的圖形處理算法)、雙通道高清輸出。這些特性使得Hi3536能夠提供高質量的圖像。此外,Hi3536集成了各種外圍接口,以滿足客戶對功能、特性和圖像質量的差異化需求,同時降低BOM成本。

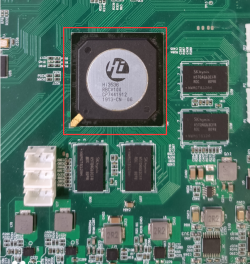

開發板的海思芯片實物如下圖所示:

九、時鐘管理

MP5610開發板為了準確適配不同用途的時鐘頻率,板載多個時鐘源。通過VCXO27.0000M產生FPGA使用的27MHz時鐘,同時經過ICS664-03和SN65LVDS1,轉換為148.5MHz的差分時鐘信號。由VCXO50.000M產生FPGA使用的50MHz時鐘。

時鐘的管腳分配詳見Clock管腳配置表。

十、JTAG調試口

MP5610開發板板載了一個2.54mm 10PIN的標準JTAG下載調試接口,方便用戶配置FPGA以及在線調試,JTAG接口與板卡內電路之間采用芯片隔離,保障FPGA芯片的安全。

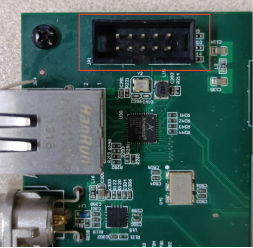

開發板JTAG接口實物如下圖所示:

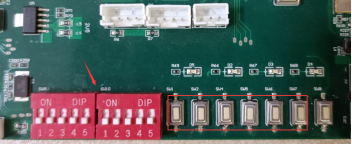

十一、復位

MP5620開發板復位信號由按鍵產生,對應的按鍵為SW8

開發板的復位按鍵實物如下圖所示:

復位信號的管腳分配詳見MP5610管腳配置表。

十二、LED燈

復位信號的管腳分配詳見MP5610管腳配置表。

開發板的用戶LED實物如下圖所示:

用戶LED的管腳分配詳見MP5610管腳配置表。

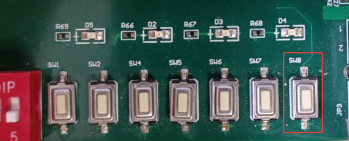

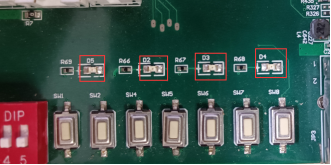

十三、按鍵和開關

MP5610開發板板載8個按鍵和10個開關。其中6個按鍵、10個開關可以由用戶支配。

開發板的按鍵和開關實物如下圖所示:

按鍵和開關的管腳分配詳見MP5610管腳配置表。

十四、電源

開發板使用12.9 V DC,通過圓孔插座供電

對于有疑問的用戶可以聯系客服接入技術支持。+W了解:M*D*Y*f*p*g*a*0*0*3

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603982 -

HDMI

+關注

關注

32文章

1712瀏覽量

152018 -

圖像處理

+關注

關注

27文章

1293瀏覽量

56781 -

開發板

+關注

關注

25文章

5068瀏覽量

97624

發布評論請先 登錄

相關推薦

正點原子fpga開發板不同型號

【北京迅為】《stm32mp157開發板嵌入式linux開發指南》第五章 Ubuntu使用apt-get下載

linux開發板和單片機開發的區別

G2D圖像處理硬件調用和測試-基于米爾-全志T113-i開發板

MP5610圖像處理開發板用戶手冊

MP5610圖像處理開發板用戶手冊

評論