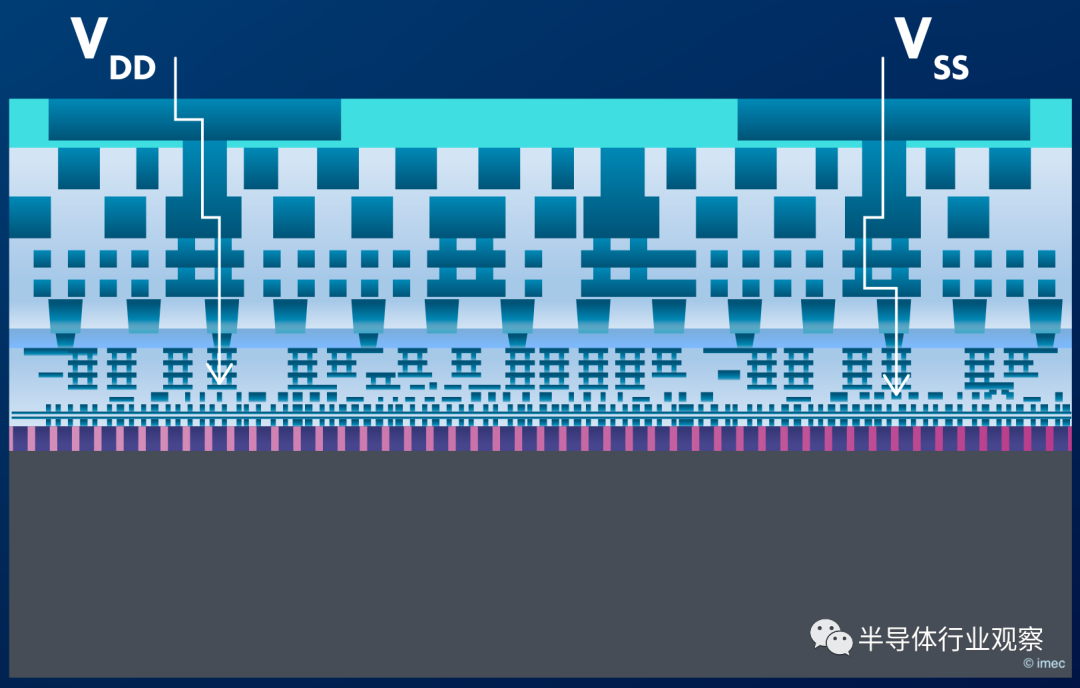

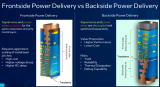

芯片上的供電網絡(power delivery network)旨在最有效地為die上的有源器件提供電源和參考電壓(即 VDD和 VSS)。傳統上,它被實現為通過晶圓正面的后端線 (BEOL) 處理制造的低電阻金屬線網絡。供電網絡與信號網絡共享這個空間,即設計用于傳輸信號的互連。

為了將功率從封裝傳輸到晶體管,電子穿過 BEOL 堆棧的所有 15 到 20 層通過金屬線和通孔,這些金屬線和通孔在接近晶體管時變得越來越窄(因此電阻更大)。在途中,它們會失去能量,從而導致功率傳輸或IR 下降。當到達更接近晶體管時,即在標準單元級別,電子最終進入在BEOL 的 M int層中組織的 V DD和 V SS電源和接地軌。這些軌道占據了邊界處和每個標準單元之間的空間。

從這里,它們通過中間互連網絡連接到每個晶體管的源極和漏極。

圖1.傳統前端供電網絡的示意圖。

但隨著每一代新技術的出現,這種傳統的 BEOL 架構都難以跟上晶體管縮放路徑的步伐。如今,“電源互連”在復雜的 BEOL 網絡中爭奪空間的競爭越來越激烈,至少占布線資源的 20%。此外,電源和接地軌在標準單元級別占據了相當大的面積,限制了標準單元高度的進一步縮放。在系統級,功率密度和 IR 壓降急劇增加,這讓設計人員難以維持穩壓器和晶體管之間的功率損耗允許的 10% 余量。

背面供電網絡的承諾

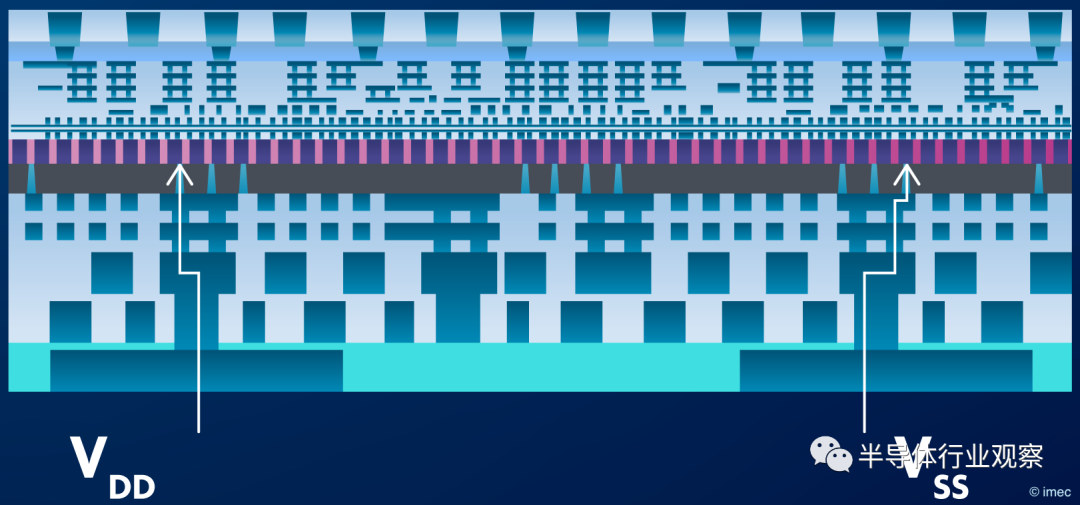

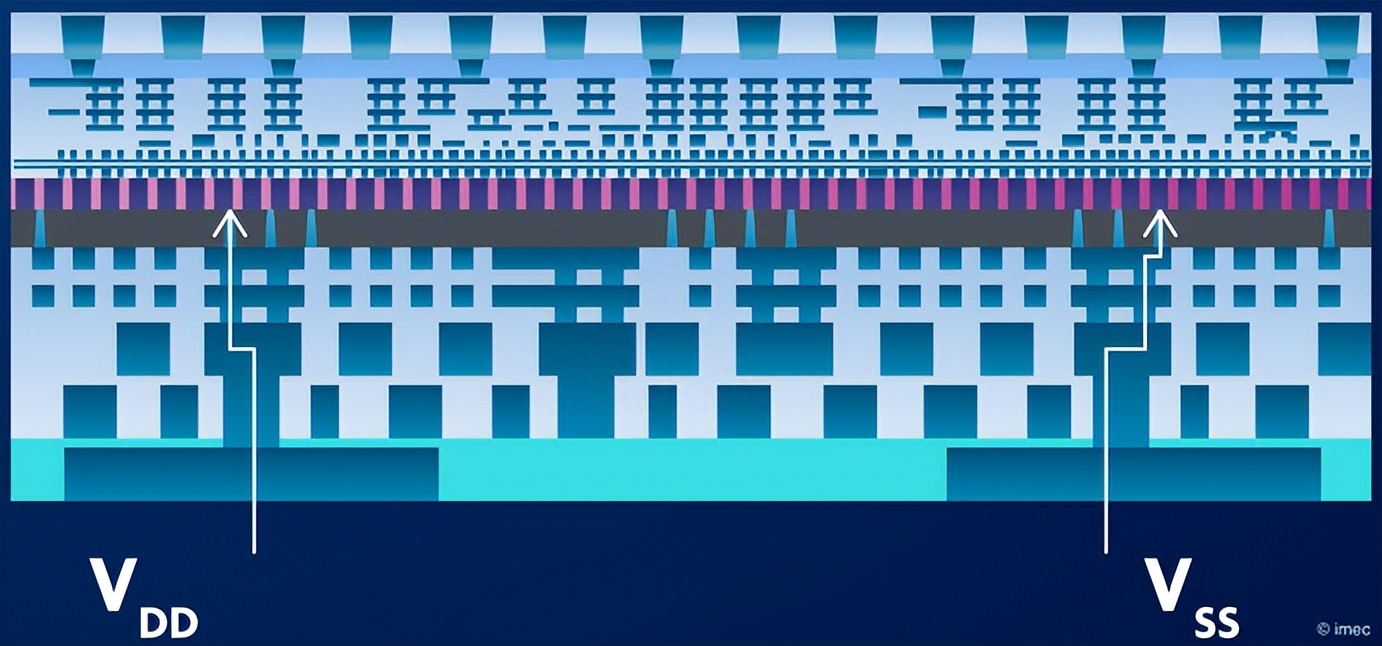

背面供電網絡有望解決這些問題。這個想法是通過將整個配電網絡移動到硅晶圓的背面來將電力傳輸網絡與信號網絡分離,而硅晶圓目前僅用作載體。

從那里,它可以通過更寬、電阻更小的金屬線將電力直接輸送到標準電池,而電子無需穿過復雜的 BEOL 堆棧。這種方法有望降低 IR 壓降,提高功率傳輸性能,減少 BEOL 中的布線擁塞,并且如果設計得當,還可以進一步擴展標準單元高度。

圖2.背面供電網絡允許將供電與信號網絡去耦。

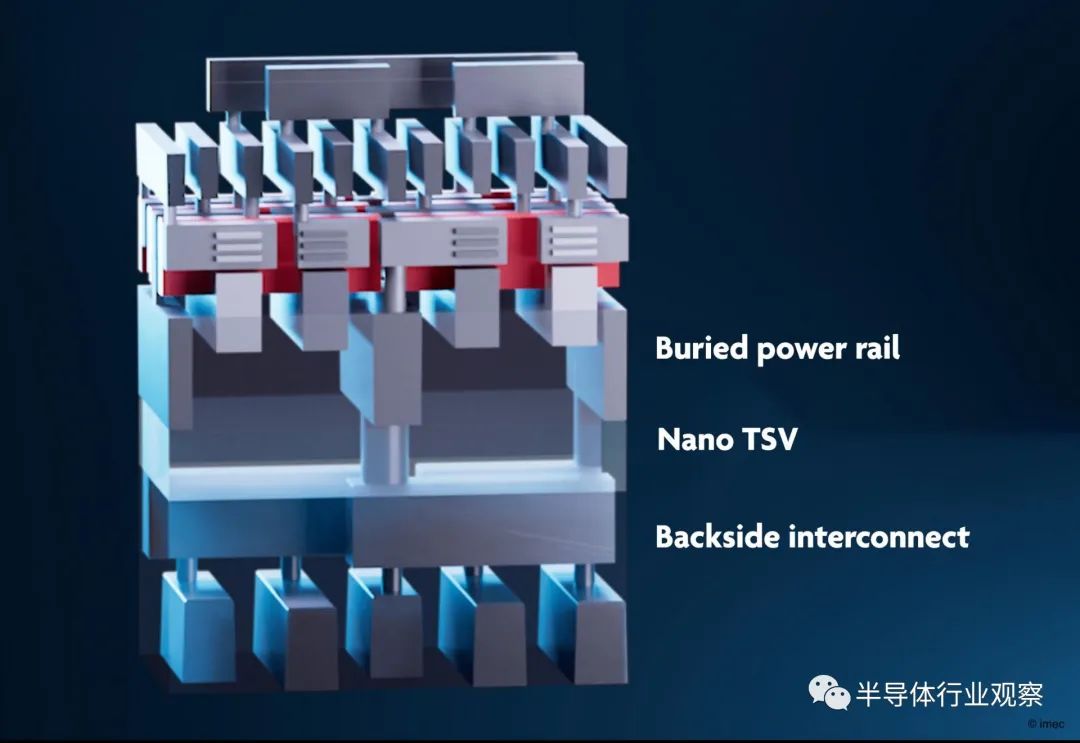

埋地電源軌和納米硅通孔:關鍵技術構建塊

在詳細介紹制造背面供電網絡的工藝流程之前,我們先介紹兩種技術推動因素:埋入式電源軌 (BPR) 和納米硅通孔 (nTSV)。

BPR 是一種技術縮放助推器,可進一步縮放標準單元高度并減少 IR 壓降。它是埋在晶體管下方的金屬線結構——部分在硅襯底內,部分在淺溝槽隔離氧化物內。它承擔了傳統上在標準單元級別的 BEOL 中實現的 VDD和 VSS電源軌的作用,這一從 BEOL 到生產線前端 (FEOL) 的歷史性轉變允許減少 M int軌道的數量,從而進一步縮小標準單元。此外,當垂直于標準單元設計時,可以放寬導軌的尺寸,從而進一步降低 IR 壓降。

當與 nTSV 結合時,BPR 的潛力可以得到充分利用,nTSV是在減薄晶圓背面加工的高縱橫比通孔。它們一起允許以最有效的方式將功率從晶圓背面傳輸到前端的有源器件,即在降低 IR 壓降方面獲得最大收益。

圖3.背面供電網絡實施的示意圖,其中納米片通過 BPR 和 nTSV 連接到晶圓的背面。

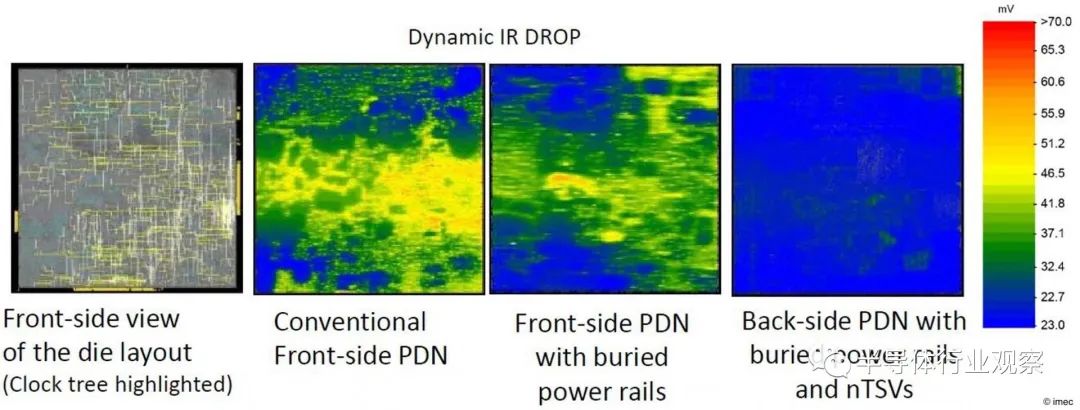

量化承諾

在 2019 年 IEDM 會議上,imec 研究與 Arm合作對這些承諾進行了量化。Arm 在其采用高級設計規則設計的中央處理器 (CPU) 之一上運行了仿真。他們比較了三種供電方式:傳統的前端供電、結合 BPR 的前端供電以及在 BPR 上使用 nTSV 的背面供電。就功率傳輸效率而言,后者顯然是贏家。片上功率熱圖顯示,與傳統的前端功率傳輸相比,具有前端功率傳輸的 BPR 可以將 IR 壓降降低約 1.7 倍。但是背面供電的 BPR做得更好:它們將 IR 壓降大大降低了 7 倍。

圖4在動態 IR 壓降方面比較不同的功率傳輸方法。

整體流程

下面,我們闡明了 BSPDN 的一個具體實現的工藝流程,其中nTSV——在極薄的晶圓背面處理——落在 BPR的頂部。這些器件,例如在晶圓正面處理的按比例縮放的 FinFET,通過 BPR 和 nTSV 連接到晶圓的背面。

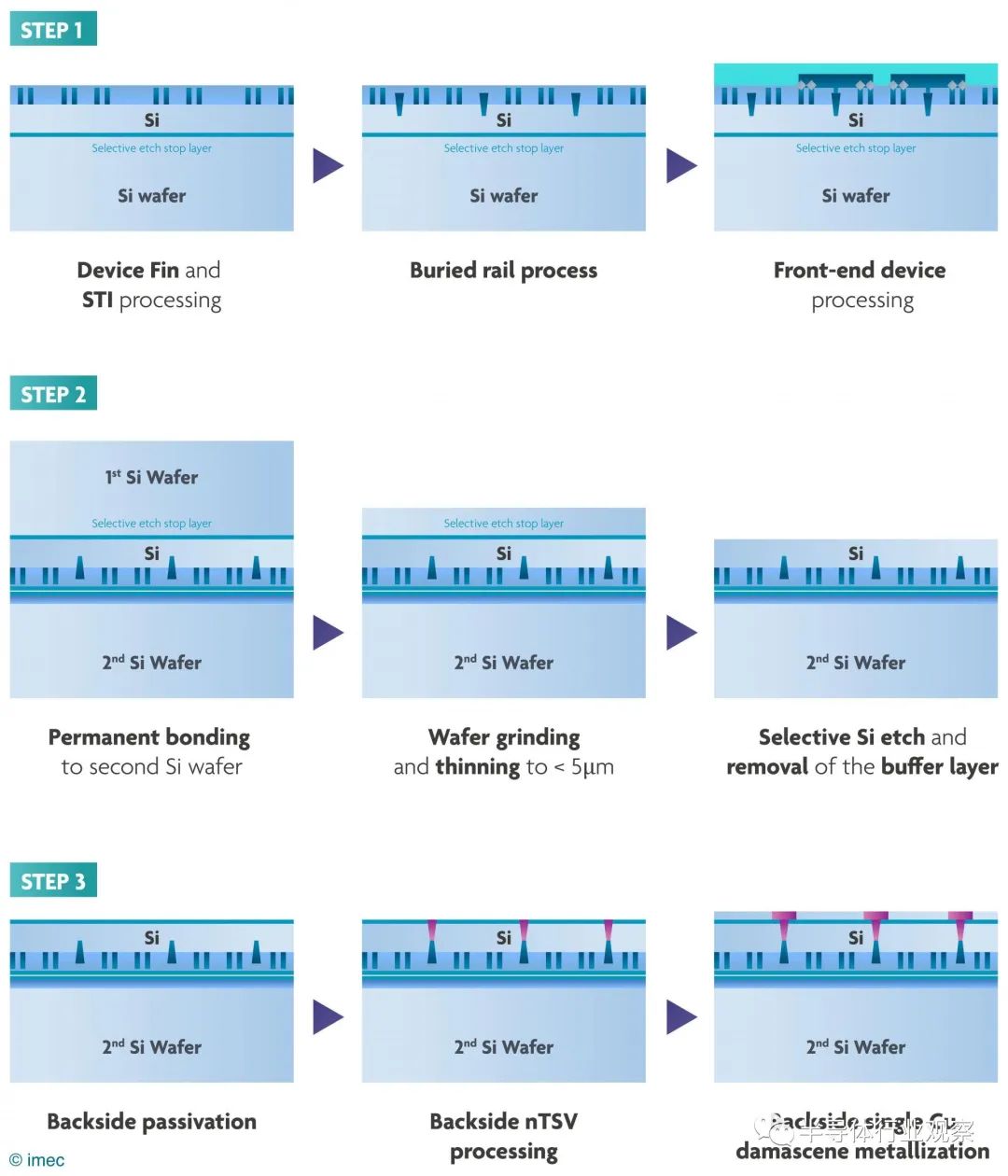

圖5.BPR 連接到 nTSV 的背面供電網絡的工藝流程。為簡化起見,步驟 1 中的一些細節已在步驟 2 和 3 中省略,包括 BPR 與設備之間的連接。

第一步:埋軌正面處理

工藝流程從在 300mm Si 晶圓頂部生長 SiGe 層開始。SiGe 層隨后用作蝕刻停止層以結束晶圓減薄(步驟 2)。接下來,在 SiGe 層的頂部生長一個薄的 Si 覆蓋層:制造器件和埋入電源軌的起點. 埋入式電源軌是在淺溝槽隔離之后定義的。在 Si 覆蓋層中蝕刻的溝槽填充有氧化物襯里和金屬,例如 W 或 Ru。由此產生的掩埋軌道通常寬約 30 納米,間距約 100 納米。然后金屬凹陷并被電介質覆蓋。在 BPR 實施后完成器件(在本例中為按比例縮放的 FinFET)的處理,并且 BPR 通過 VBPR 過孔和 M0A 線連接到晶體管源/漏區。銅金屬化完成正面處理。

第 2 步:晶圓間鍵合和晶圓減薄

翻轉包含器件和 BPR 的晶圓,并將“有源”正面鍵合到覆蓋載體晶圓上。這是通過在室溫下使用 SiCN-to-SiCN 電介質熔接,然后在 250°C 下進行鍵合后退火來實現的。

然后,可以將第一個硅片的背面減薄到 SiGe 蝕刻停止所在的位置。通過順序背面研磨、化學機械拋光 (CMP) 以及干法和濕法蝕刻步驟的組合實現減薄。SiGe 層在下一步中被移除,晶圓已準備好進行 nTSV 處理。

第 3 步:nTSV 處理和連接到 BPR

在沉積背面鈍化層后,通過硅對準光刻工藝從晶圓背面對nTSV 進行圖案化。nTSV 蝕刻穿過 Si(幾 100nm 深)并落在 BPR 的尖端。接下來,nTSV填充有氧化物襯里和金屬 (W)。在這個特定的實現中,它們以 200 納米間距集成,而不會占用標準單元的任何面積。該流程通過處理一個或多個背面金屬層來完成,通過 nTSV 將晶圓的背面電連接到正面的 BPR。

仔細研究關鍵流程步驟

實施背面供電網絡為芯片制造增加了新的步驟。在過去的幾年里,imec 展示了各種關鍵技術構建模塊,逐漸解決了新生產步驟的挑戰。

BPR:在生產線前端引入金屬

在建議的制造流程中,在器件處理之前,埋入式電源軌在 FEOL 中實現。這種實施意味著金屬導軌要經受后續設備制造過程中應用的高溫工藝步驟。對于芯片制造商而言,這似乎與幾十年前將 Cu 引入 BEOL 一樣具有破壞性。因此,用于制造 BPR 的金屬的選擇至關重要。Imec 可以成功地展示由難熔金屬(如 Ru 或 W 等具有高度耐熱性的金屬元素)制成的埋地電源軌的集成。在隨后的 FEOL 處理過程中保持金屬導軌蓋住是避免前端污染的一項額外措施。

Imec 認為,在可擴展性和性能方面,使用 nTSV 結合 BPR 是一種非常有前途的實現方案。背面供電網絡的其他實現也存在,每一種都在供電性能、標準單元面積消耗和前端離線復雜性之間進行權衡。

晶圓減薄:最小化厚度變化

需要將晶圓極度減薄到幾 100 納米的 Si,以暴露 nTSV 并最小化它們的電阻率(以及因此的 IR 壓降)。這嚴重限制了允許的厚度變化,這可能在不同的晶圓減薄步驟期間引起。Imec 與多個合作伙伴合作改進用于蝕刻的化學物質。例如,最終的濕法蝕刻能夠實現在 SiGe 層上停止的高選擇性軟著陸工藝。在減薄工藝的最后一步,SiGe 蝕刻停止層在需要對 Si 具有非常高選擇性的專用化學物質中被去除。這樣,可以暴露 Si 覆蓋層,總厚度變化低于 40nm。

另一個問題是由于(否則會散熱)Si 基板的極度變薄對器件自熱的熱影響。初步建模工作表明,自熱效應在很大程度上可以被晶圓背面的金屬線抵消,金屬線提供額外的橫向熱擴散。目前正在進行更詳細的熱模擬以獲得更多見解。

晶圓鍵合:精確的 nTSV/BPR 對準

晶圓鍵合步驟固有地扭曲了第一個“有源”晶圓。這種變形挑戰了在晶圓背面圖案化 nTSV 所需的光刻步驟。更具體地說,它挑戰了 nTSV 需要與底部 BPR 層對齊的精度。由于我們處理的是標準單元尺寸的特征,因此覆蓋要求應優于 10nm。然而,傳統的光刻對準不能充分補償晶圓變形。

幸運的是,晶圓間鍵合技術的進步可以顯著降低對準誤差和畸變值。此外,通過使用先進的光刻校正技術,覆蓋錯誤相對于 BPR 結構的 nTSV 光刻可以減少到小于 10nm。

不會降低設備性能

一個重要的問題仍然存在:新添加的工藝步驟,例如 BPR 集成、晶圓減薄和 nTSV 處理,是否會影響前端制造的器件的電氣性能?

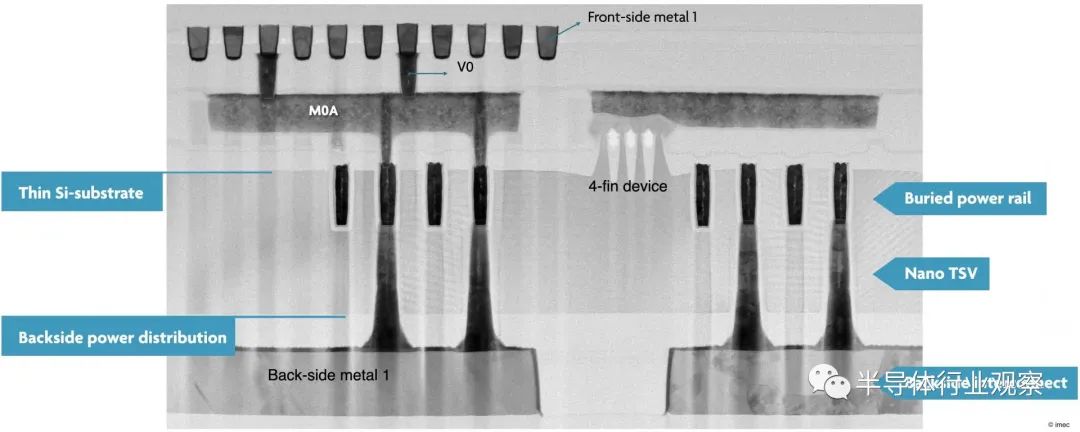

為了回答這個問題,imec 最近使用上述制造流程和改進的工藝步驟制造了一個測試產品。在此測試工具中,按比例縮小的 FinFET 通過 320 納米深的 nTSV 落在 BPR 上,以嚴格的覆蓋控制連接到晶圓的背面。BPR 還通過 M0A 層和 V0 通孔連接到正面金屬化層。除其他外,這種正面連接使研究人員能夠評估背面處理前后設備的電氣性能。通過該測試工具,imec 表明FinFET 性能不會因 BPR 實施和背面處理而降低,前提是在最后執行退火步驟以獲得最佳器件特性。

圖6.TEM 圖像顯示按比例縮放的 FinFET 連接到晶圓的背面和正面。

應用領域:高級邏輯 IC 和 3D-SOC 的擴展

一些芯片制造商已經公開宣布在 2nm 及以下技術節點的邏輯 IC 中引入背面供電網絡。這是納米片晶體管取得進展的時候。然而,新穎的路由技術可用于范圍廣泛的晶體管架構。Imec 的路線圖預見了它在先進技術節點中的引入,以及 6T 標準單元中的納米片晶體管。與 BPR 的結合將有助于將標準電池高度推至 6T 以下。

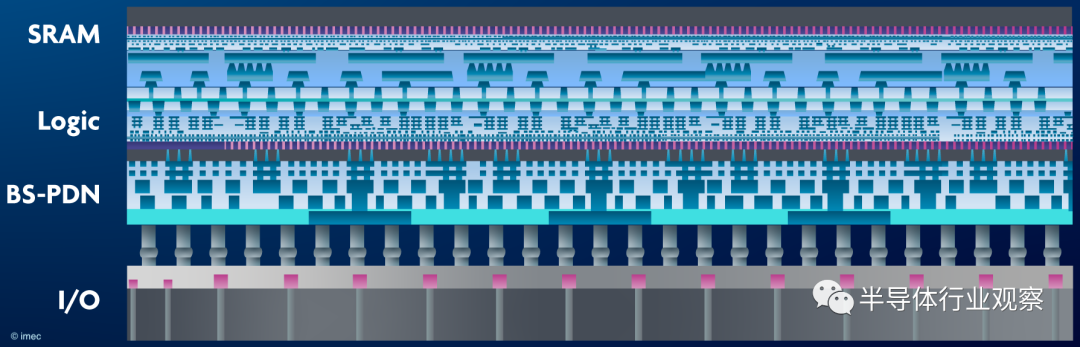

但應用領域不僅僅局限于 2D 單芯片 IC:它還有望提高3D 片上系統的性能(3D SOC)。想象一下 3D-SOC 實現,其中一些或所有存儲器宏被放置在頂部裸片中,而邏輯被放置在底部裸片中。在技術方面,這可以通過將“邏輯晶圓”的有源正面粘合到“存儲晶圓”的有源正面來實現。在此配置中,兩個晶圓的原始背面現在位于 3D-SOC 系統的外部。我們現在可以考慮利用“邏輯晶圓”的“自由”背面來為耗電大的核心邏輯電路供電。這可以通過與為 2D SOC 提議的相同的方式來完成。主要區別是:原來的虛擬覆蓋晶圓——之前為了使晶圓變薄而引入——現在被第二個有源晶圓(在本例中為存儲晶圓)取代。

圖7.具有背面功率傳輸實施的 3D-SOC 的示意圖。

盡管這種設計尚未通過實驗實施,但從 IR 壓降角度進行的初步評估非常令人鼓舞。使用高級節點研究過程設計套件 (PDK)在邏輯上的內存分區設計上驗證了所提出的解決方案。使用 nTSV 和 BPR 實施背面供電網絡顯示出可喜的結果:與傳統的正面供電相比,底部裸片的平均和峰值 IR 壓降減少了 81% 和 77%。這使得背面供電成為高級 CMOS 節點中 3D IC 供電的理想選擇。

對于 2D 和 3D 設計,通過在背面添加特定設備(例如 I/O 或 ESD 設備),可以將利用晶圓自由背面的概念擴展到其他功能。例如,Imec 將背面處理與實現 2.5D(即柱狀)金屬-絕緣體-金屬電容器 (MIMCAP) 相結合,用作去耦電容器。2.5D MIMPCAP 將電容密度提高了 4 到 5 倍,從而進一步改善了 IR 壓降。結果源自用實驗數據校準的 IR 壓降建模框架。

總結

未來的芯片很可能會打破通過前端供電的傳統。具有背面金屬、埋入式電源軌和 nTSV 的背面供電網絡在降低 IR 壓降、釋放 BEOL 布線壓力和改進標準單元高度縮放方面顯示出明顯的優勢。BPR集成、晶圓鍵合、晶圓減薄和nTSV工藝等關鍵工藝步驟正在逐步完善,為新的布線技術引入先進的邏輯技術節點和未來的3D SOC做準備。

審核編輯:郭婷

-

電源

+關注

關注

185文章

18385瀏覽量

256560 -

芯片

+關注

關注

460文章

52568瀏覽量

441905 -

穩壓器

+關注

關注

24文章

4704瀏覽量

96318

原文標題:如何從背面為芯片供電

文章出處:【微信號:cetc45_wet,微信公眾號:半導體工藝與設備】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

MAX40660數據手冊中的示例為單電源軌+3.3V供電,請問用+/-1.8V供電是否可行?

如何使用Fly-buck?為低電壓、低功耗工業應用供電

ADP505x可為多個電源軌和緊湊式設計的中型FPGA供電

為Xilinx Zynq 7000系列FPGA供電所需電源軌的參考設計

評論