PCIe在數(shù)據(jù)中心無處不在。為了支持新一代應用的更高性能要求,企業(yè)正在不斷提升速度和帶寬,進而使CXL的重要性日益提升。越來越多的芯片公司開始支持新的數(shù)據(jù)中心架構(gòu),因此獲得高性能接口IP解決方案將成為實現(xiàn)該生態(tài)系統(tǒng)的關(guān)鍵。

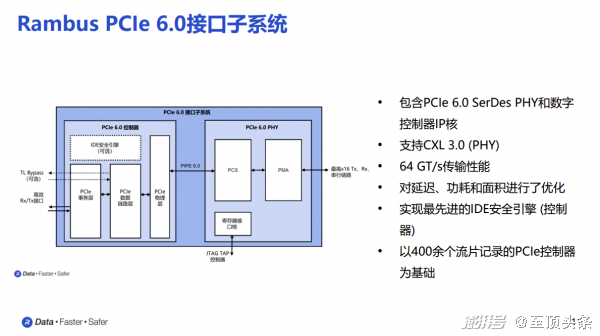

近日,Rambus宣布推出由PHY和控制器IP組成的PCI Express(PCIe)6.0接口子系統(tǒng)。Rambus PCIe 6.0接口子系統(tǒng)可通過一流的延遲、功耗、面積和安全性,支持下一代數(shù)據(jù)中心對性能的要求。

PCIe 6.0的應運而生

人工智能/機器學習(AI/ML)和數(shù)據(jù)密集型工作負載的快速發(fā)展正在推動數(shù)據(jù)中心架構(gòu)的持續(xù)演進,并要求更高的性能水平。

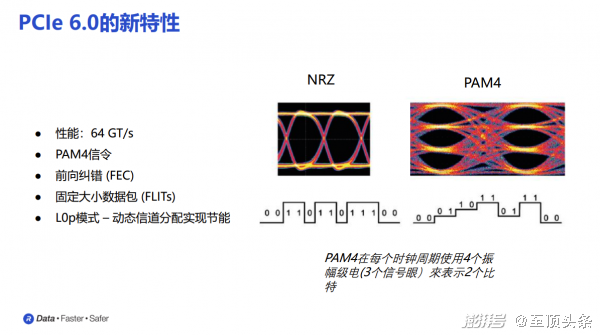

Rambus戰(zhàn)略營銷副總裁Matt Jones告訴記者,數(shù)據(jù)爆炸式增長對于數(shù)據(jù)傳輸速率有了更高的要求,和上一代5.0的32GT/s相比,PCIe 6.0的數(shù)據(jù)傳輸速率高達64GT/s。

為了進一步滿足PCIe 6.0達到64GT/s數(shù)據(jù)傳輸速率的需求,它的架構(gòu)必須要重新優(yōu)化和調(diào)整。同時,在整個電路和電路傳輸機制的配比上也是存在著巨大的差異。這當中有一個最大的變化,就是從NRZ到PAM4的轉(zhuǎn)變,NRZ指的是不歸零的編碼,PAM4是一個四電平脈沖輔助的調(diào)制。

全新的PAM4信令帶來PCIe 6.0兩大非常重要的改變。第一個改變就是采用前向糾錯(FEC),支持固定大小數(shù)據(jù)包(FLITs)。第二個重要的變化就是在PCIe 6.0當中采取的L0p模式。L0p模式可以讓PCIe 6.0實現(xiàn)動態(tài)信道分配,更好地實現(xiàn)產(chǎn)品設備的節(jié)能。

以前芯片開發(fā)人員單獨使用PHY和控制器,同時他們還必須進行重復冗雜的驗證工作,而Rambus PCIe 6.0接口子系統(tǒng)為芯片設計人員提供控制器和PHY解決方案,并將其完全集成和驗證為一個完整的子系統(tǒng),可在其芯片中實施,進一步降低了設計的復雜性。

PCIe 6.0和64GT/s數(shù)據(jù)傳輸速率的提升加速數(shù)據(jù)中心向異構(gòu)計算進行迭代和變化,包括數(shù)據(jù)中心本身的架構(gòu)會變得更加先進,不管是分布式計算還是可組合的架構(gòu),這些也都是隨著PCIe 6.0的推出會帶來的變化,提高數(shù)據(jù)中心的智能化水平。

這些會催生專門針對特別應用比如高性能計算所開發(fā)的不同加速器,進一步實現(xiàn)數(shù)據(jù)在不同組件之間傳輸效率的提升,云服務商的工作負載也都能夠在數(shù)據(jù)中心得到進一步的管理和優(yōu)化。

Matt Jones表示,為了實現(xiàn)PCIe 6.0在數(shù)據(jù)中心有更大大范圍的使用,我們需要確保整個數(shù)據(jù)中心內(nèi)部的生態(tài)系統(tǒng)可以支持這么快的數(shù)據(jù)傳輸速率,具體來講就是包括服務器本身的CPU還有它的芯片是要符合和支持最新的版本,其次,輸入、輸出設備也必須達到64GT/s的傳輸速率的基礎要求。

Rambus PCIe 6.0

新特性

Rambus PCIe 6.0接口子系統(tǒng)有以下主要特性:

支持PCIe 6.0規(guī)范,包括64GT/s數(shù)據(jù)傳輸速率和PAM4調(diào)制信號

實現(xiàn)低延遲前向糾錯(FEC),保證鏈路穩(wěn)健性

支持固定尺寸的FLIT,可實現(xiàn)高帶寬效率

向后兼容PCIe 5.0、4.0和3.0/3.1

通過IDE引擎(控制器)實現(xiàn)最先進的安全性

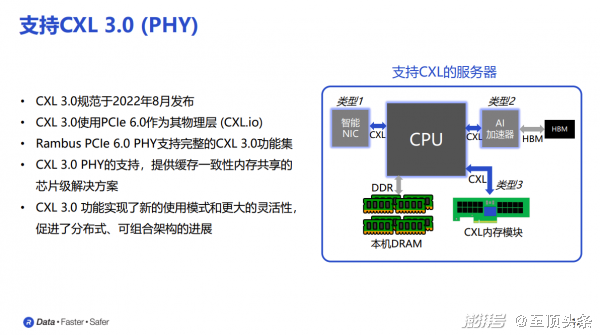

支持CXL 3.0,用于優(yōu)化內(nèi)存資源的新使用模式(PHY)

Matt Jones介紹說,Rambus PCIe 6.0接口子系統(tǒng)采用PHY和控制器的全集成,從而可以進一步降低延遲,更好的降低功耗,以及優(yōu)化具體產(chǎn)品和芯片的占用面積。

Rambus PCIe 6.0接口子系統(tǒng)的數(shù)據(jù)傳輸速率高達64GT/s,并且經(jīng)過全面優(yōu)化,可滿足先進異構(gòu)計算架構(gòu)的需求。該子系統(tǒng)中的PCIe控制器具備完整性和數(shù)據(jù)加密(IDE)引擎,專門用于保護PCIe鏈接和通過它們傳輸?shù)闹匾獢?shù)據(jù)。

另外它還提供對支持最新版本(3.0版本)的Compute Express Link(CXL)規(guī)范的全面PHY支持,支持緩存一致性內(nèi)存共享、擴展和池化的芯片級解決方案。

“作為PCIe 6.0子系統(tǒng)重要組成的PHY將全面支持CXL 3.0版本下全部特性和相關(guān)功能,更好地支持閃存一致性,從而推動數(shù)據(jù)中心的長期應用和發(fā)展。我們期待與客戶合作,利用CXL3.0解決方案,實現(xiàn)數(shù)據(jù)中心向分布式可組合架構(gòu)的變革。”Matt Jones說。

Rambus PCIe 6.0解決方案支持三大非常關(guān)鍵的目標市場以及終端市場,分別是存儲、智能網(wǎng)卡,以及加速器市場。因為以PCIe 6.0所支持非常高的數(shù)據(jù)傳輸速率,可以確保數(shù)據(jù)在不同服務器之間,以及系統(tǒng)組件之間安全的傳輸,以及在傳輸過程當中的安全性。

結(jié)語

當前中國數(shù)據(jù)中心市場蓬勃發(fā)展,而數(shù)據(jù)中心三年發(fā)展計劃和東數(shù)西算的發(fā)布和推進引領數(shù)據(jù)中心發(fā)展進入一個新的階段。創(chuàng)新驅(qū)動發(fā)展,新數(shù)據(jù)中心的發(fā)展也必將會采用越來越多的先進技術(shù)。

面向數(shù)據(jù)中心的發(fā)展訴求,Rambus能夠提供一系列的解決方案,包括業(yè)界領先的DDR5和DDR4在內(nèi)的內(nèi)存接口芯片;業(yè)界一流的HBM3和HBM2E、GDDR6等內(nèi)存子系統(tǒng)IP方案;支持PCIe 6.0、5.0、CXL 3.0、2.0接口子系統(tǒng)IP方案;以及支持數(shù)據(jù)中心、服務器中靜態(tài)數(shù)據(jù)、動態(tài)數(shù)據(jù)的加密,實現(xiàn)硬件級的安全IP方案。這些產(chǎn)品和方案極大助力數(shù)據(jù)中心的應用需求,比如企業(yè)級的內(nèi)存條、AI加速芯片、智能網(wǎng)卡、網(wǎng)絡交換機、內(nèi)存擴展和池化等。

Rambus大中華區(qū)總經(jīng)理蘇雷表示,整個行業(yè)希望數(shù)據(jù)中心的數(shù)據(jù)傳輸更快、更安全,資源利用率高,以及更低的綜合成本。Rambus將通過各項領先的技術(shù)和解決方案,全力以赴地服務中國客戶和數(shù)據(jù)中心市場。

“PCIe的應用場景越來越豐富,Rambus推出的PCIe 6.0相關(guān)產(chǎn)品有著非常廣泛的市場需求,比如數(shù)據(jù)中心、IoT、汽車IoT、汽車,以及政府相關(guān)應用。憑借行業(yè)領先的性能和來自Rambus的安全集成解決方案,我們正在通過創(chuàng)新真正使數(shù)據(jù)變得更快、更安全。”Matt Jones最后說。

審核編輯 :李倩

-

控制器

+關(guān)注

關(guān)注

112文章

16396瀏覽量

178512 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

4806瀏覽量

72209 -

PCIe

+關(guān)注

關(guān)注

15文章

1243瀏覽量

82766

原文標題:面向高性能數(shù)據(jù)中心和人工智能SoC Rambus推出PCIe 6.0接口子系統(tǒng)

文章出處:【微信號:Rambus 藍鉑世科技,微信公眾號:Rambus 藍鉑世科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

人工智能對數(shù)據(jù)中心的挑戰(zhàn)

PCIe加速卡在數(shù)據(jù)中心的應用

SOC芯片在人工智能中的應用

當今數(shù)據(jù)中心新技術(shù)趨勢

Supermicro推出面向AI數(shù)據(jù)中心的液冷超級集群

risc-v在人工智能圖像處理應用前景分析

SK海力士推出高性能數(shù)據(jù)中心SSD PEB110

Molex連接器助力構(gòu)建未來數(shù)據(jù)中心 充分發(fā)揮人工智能AI的力量

燧原科技與銳捷網(wǎng)絡攜手共筑AI數(shù)據(jù)中心高性能網(wǎng)絡新紀元

美光推出9550系列數(shù)據(jù)中心PCIe 5.0 SSD

人工智能數(shù)據(jù)中心的新型連接解決方案

夏普討論建立人工智能數(shù)據(jù)中心

SiTime推出面向人工智能數(shù)據(jù)中心的Chorus?系列MEMS時鐘發(fā)生器

面向高性能數(shù)據(jù)中心和人工智能SoC Rambus推出PCIe 6.0接口子系統(tǒng)

面向高性能數(shù)據(jù)中心和人工智能SoC Rambus推出PCIe 6.0接口子系統(tǒng)

評論