作者:Richard Anslow and Dara O’Sullivan

在本文的第一部分“為工業4.0實現可靠的有線狀態監控——第1部分”中,我們介紹了ADI公司的有線接口解決方案,這些解決方案可縮短客戶設計周期和測試時間,并加快工業CbM解決方案的上市時間。討論了幾個方面,包括選擇合適的MEMS加速度計和物理層,以及EMC性能和電源設計。此外,第 1 部分還介紹了三種設計解決方案和性能權衡。本文(第 2 部分,共 2 部分)重點介紹第 1 部分中介紹的 SPI 至 RS-485/RS-422 設計解決方案的詳細物理層設計注意事項。

為MEMS實現有線物理層接口的常見挑戰包括管理EMC魯棒性和數據完整性。然而,當在長RS-485/RS-422電纜上擴展時鐘同步接口(如SPI)時,以及在同一雙絞線(幻象電源)上組合電源和數據時,還存在一些額外的挑戰。本文討論以下關鍵注意事項,并提供設計物理層接口的建議:

管理系統時間同步

數據速率與電纜長度的關系建議

幻象電源實現的無源元件性能權衡

組件選擇和系統設計窗口

實驗測量

時間同步和電纜長度

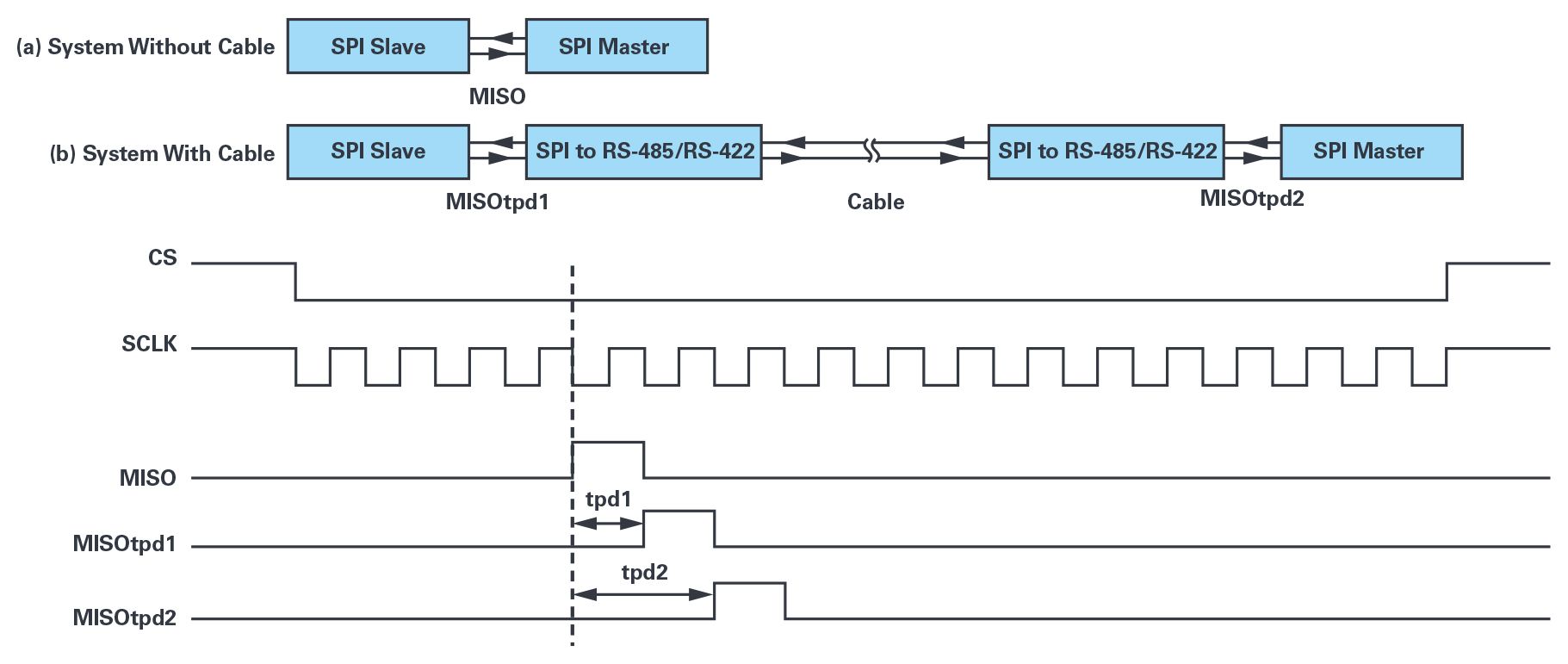

設計SPI至RS-485/RS-422鏈路時,電纜和組件會影響系統時鐘和數據同步。在長距離電纜傳輸中,SCLK 信號將通過電纜產生傳播延遲,對于 100 m 電纜,大約為 400 ns 至 500 ns。對于 MOSI 數據傳輸,MOSI 和 SCLK 通過電纜同樣延遲。但是,從從MISO發送到主站的數據將與SCLK不同步,其速度是電纜傳播延遲的兩倍。最大可能的SPI SCLK由系統傳播延遲設置,其中包括電纜傳播延遲以及主組件和從組件傳播延遲。

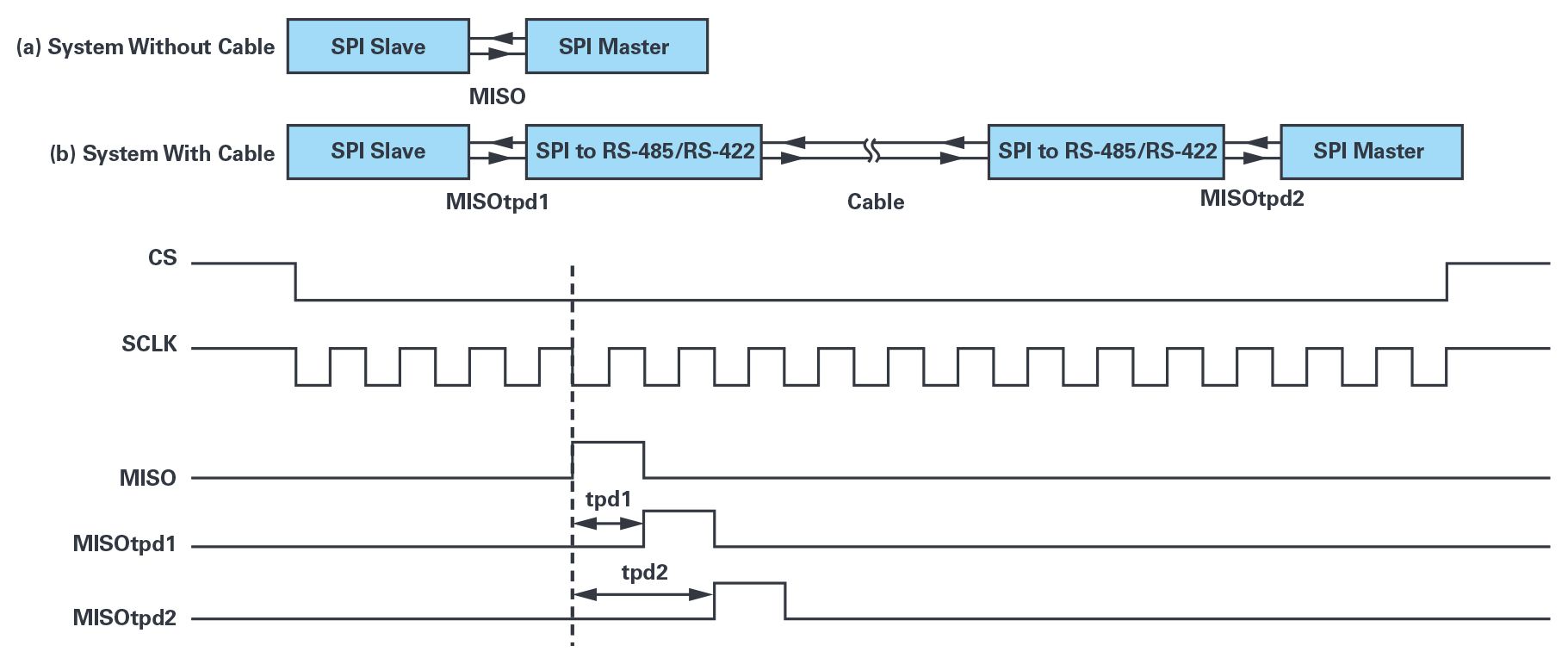

圖1說明了系統傳播延遲如何導致SPI主站的SPI MISO采樣不準確。對于沒有RS-485/RS-422電纜的系統,MISO數據和SPI SCLK將以很少或沒有延遲的方式同步。對于帶電纜的系統,SPI從站的MISO數據與SPI SCLK不同步,有一個系統傳播延遲,如圖1中的tpd1所示。MISO數據通過兩個系統傳播延遲(稱為tpd2)不同步地返回主站。由于電纜和組件傳播延遲導致數據向右移動,因此會出現不準確的數據采樣。

圖1.同步MISO數據和SPI SCLK,適用于帶或不帶長RS-485/RS-422電纜的系統。

為了防止MISO采樣不準確,可以減少電纜長度,降低SPI SCLK或在主控制器中實現SPI SCLK補償方案(時鐘相移)。理論上,系統傳播延遲應小于SCLK時鐘周期的50%,以實現無差錯通信,在實踐中,系統延遲限制為40%SCLK可以作為一般規則。

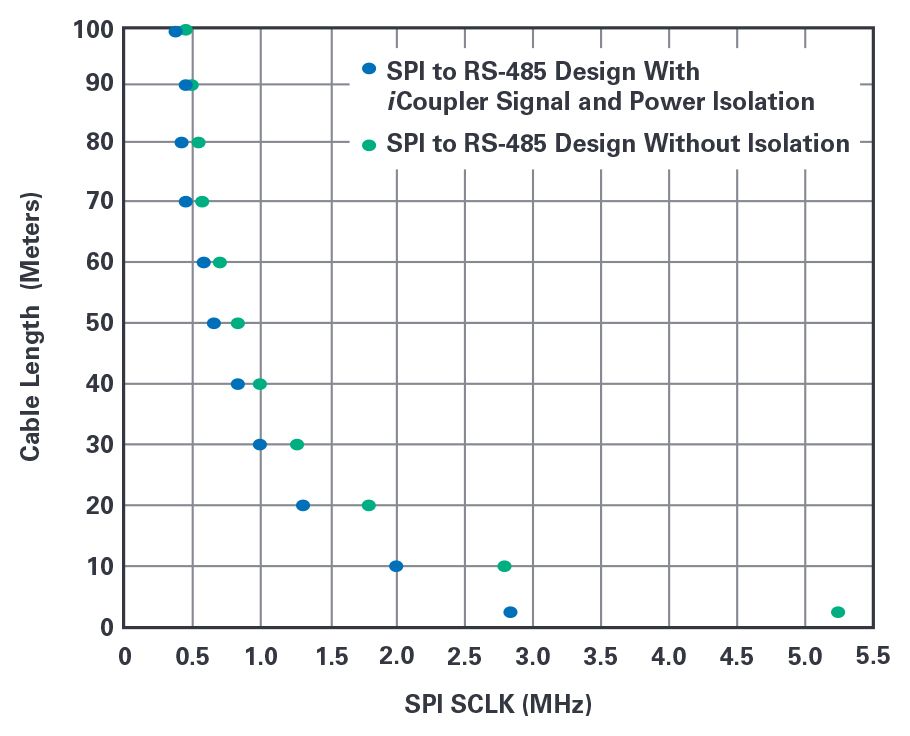

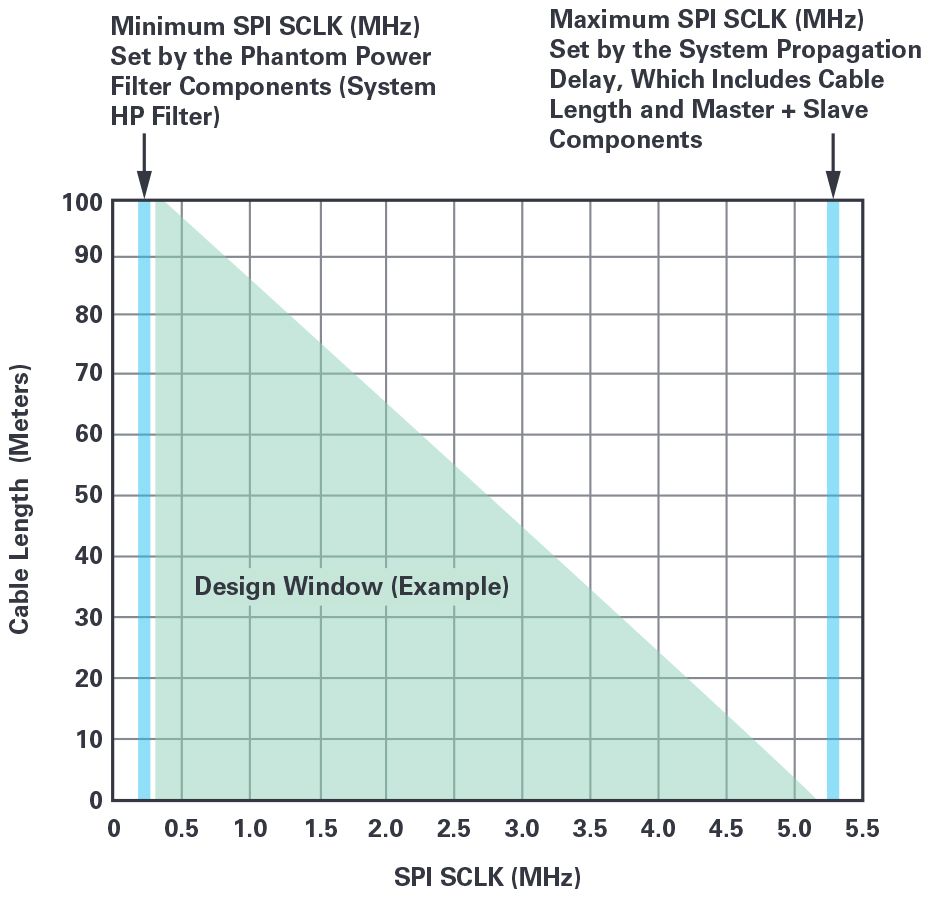

圖2提供了第1部分所述的兩種SPI至RS-485/RS-422設計的SPI SCLK與電纜長度的比較指南。1非隔離設計采用ADI公司的高速EMC魯棒型小尺寸RS-485/RS-422器件(ADM3066E和ADM4168E)。隔離式設計還包括ADI公司的iCoupler信號和電源隔離型ADuM5401器件,為SPI至RS-485/RS-422鏈路提供額外的EMC魯棒性和抗噪性。這種設計增加了額外的系統傳播延遲,從而限制了在較高SPI SCLK速率下的操作。對于較長的電纜(大于 30 m),強烈建議增加隔離,以幫助緩解接地環路和 EMC 事件,例如靜電放電 (ESD)、電氣快速瞬變 (EFT) 和耦合到數據傳輸電纜的高壓浪涌。當電纜長度擴展到30 m或更大時,隔離式和非隔離式設計的SPI SCLK與電纜長度性能相似,如圖2所示。?

圖2.SPI SCLK 與隔離和非隔離設計的電纜長度指南。

幻象電源

背景

幻象電源將電源和數據結合在一根雙絞線上,可在主設備、從設備之間實現單電纜解決方案。將數據和電源結合在一根電纜上,可在空間受限的邊緣傳感器節點上實現單連接器解決方案。

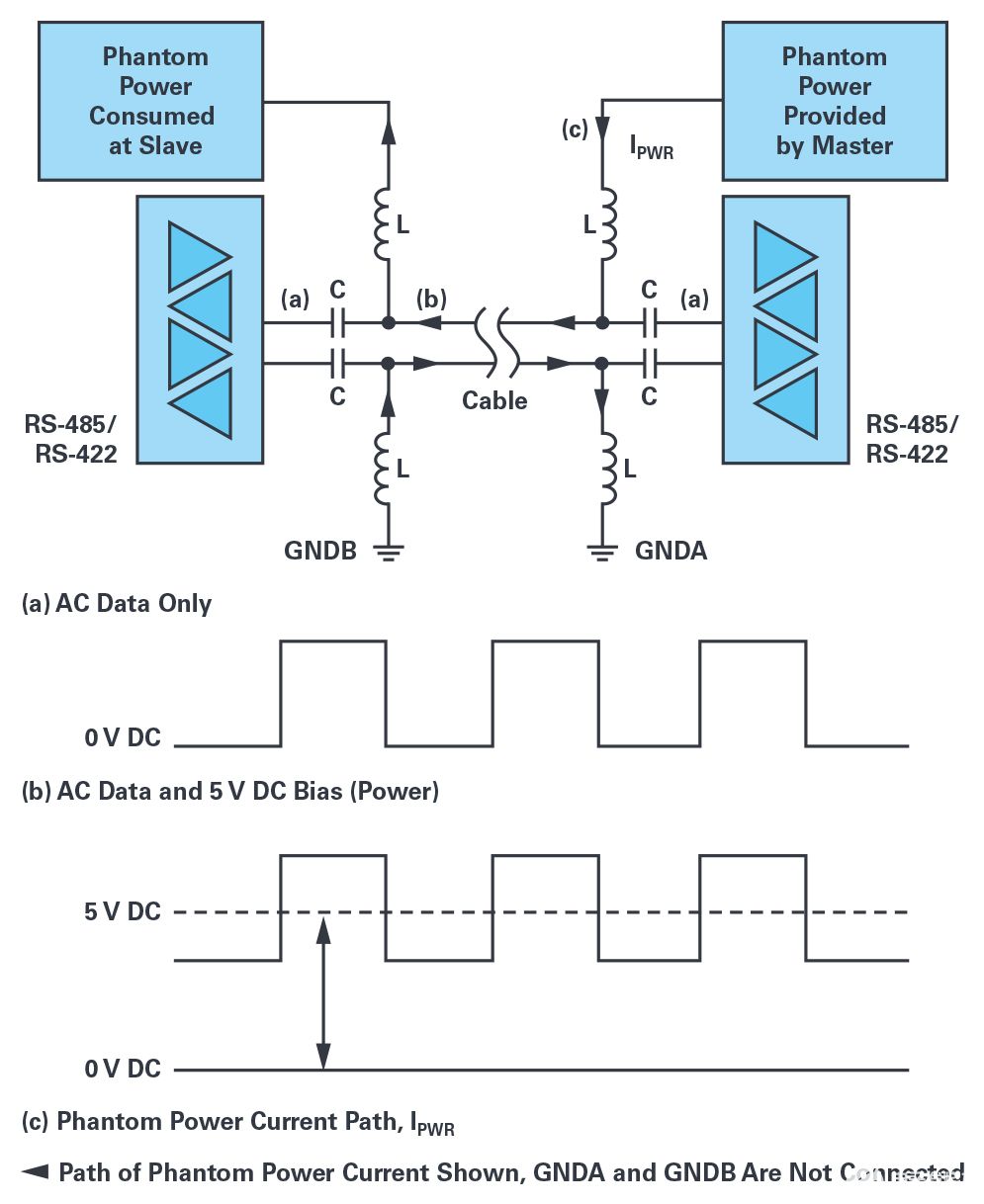

電源和數據使用電感電容網絡分布在一根雙絞線上,如圖3所示。高頻數據通過串聯電容耦合到數據線,這還可以保護RS-485/RS-422收發器免受直流總線電壓的影響,如圖3a所示。圖3顯示了通過連接到數據線的電感器連接到主控制器的電源。5V直流電源偏置交流數據總線,如圖3b所示。在圖3c中,電流路徑顯示為I壓水堆在主站和從站之間,使用電纜遠端狀態監控 (CbM) 從屬傳感器節點上的電感器從線路中提取功率。

圖3.幻象電源物理層交流和直流電壓電平。

高通濾波器

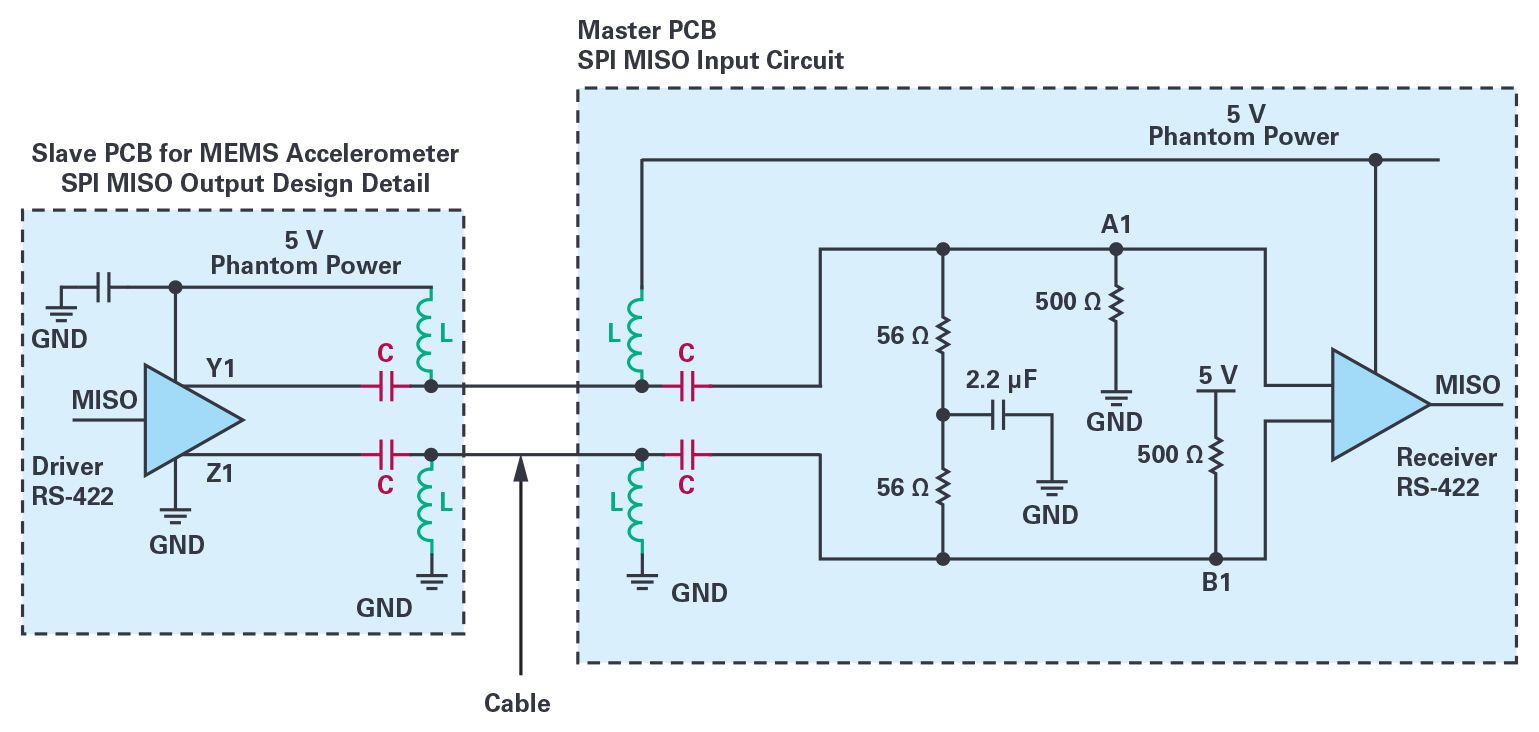

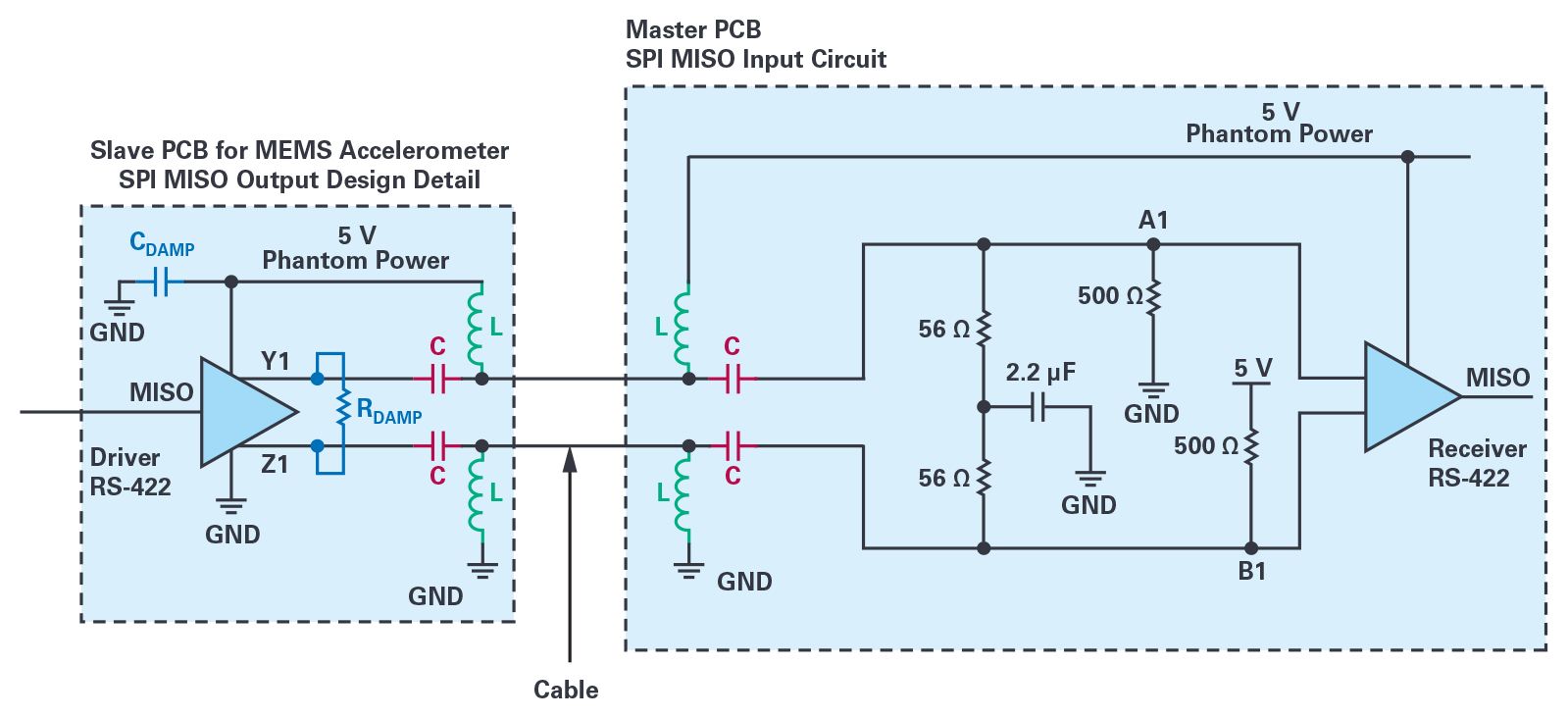

就本文而言,假設將幻象功率電感-電容網絡添加到兩根導線上,用于路由SPI MISO信號的RS-485/RS-422轉換。圖4顯示了RS-485/RS-422的主從SPI設計以及SPI MISO數據線的幻象電源濾波器電路。濾波電路是高通的,因此要求傳輸的數據信號在直流或非常低的頻率下沒有內容。

圖4.SPI至RS-485/RS-422設計和幻象電源濾波器電路。

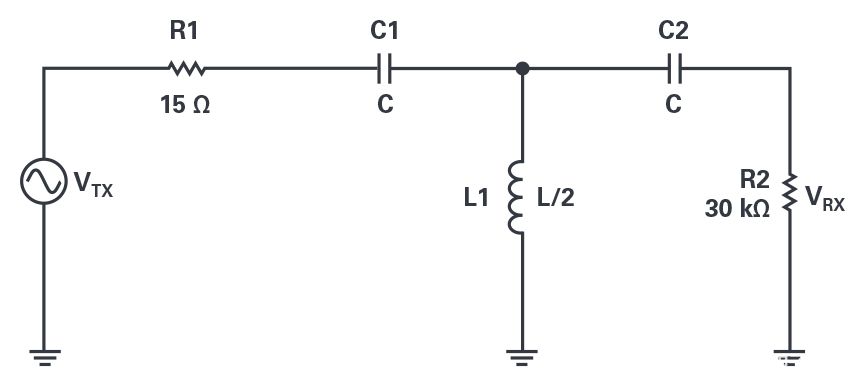

二階高通濾波器電路如圖5所示,這是圖4的簡化表示。發送RS-485/RS-422設備的電壓輸出標記為V德克薩斯州,具有R1 15 Ω輸出阻抗。R2 30 kΩ是接收RS-485/RS-422器件的標準輸入阻抗。可以選擇電感(L)和電容(C)值,以適應所需的系統數據速率。

圖5.用于RS-422發送和RS-485/RS-422接收數據路徑的二階高通濾波器。

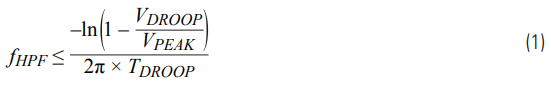

選擇電感(L)和電容(C)值時,需要考慮最大RS-485/RS-422總線電壓下降和下降時間,如圖6所示。存在標準,例如單雙絞線以太網,2其中規定了最大允許電壓下降和下降時間,如圖6a所示。對于某些系統,最大允許電壓下降和下降時間可能更大,受信號極越點的限制,如圖6b所示。

電壓下降和下降時間可以與圖5的仿真配合使用,以確定系統高通頻率。

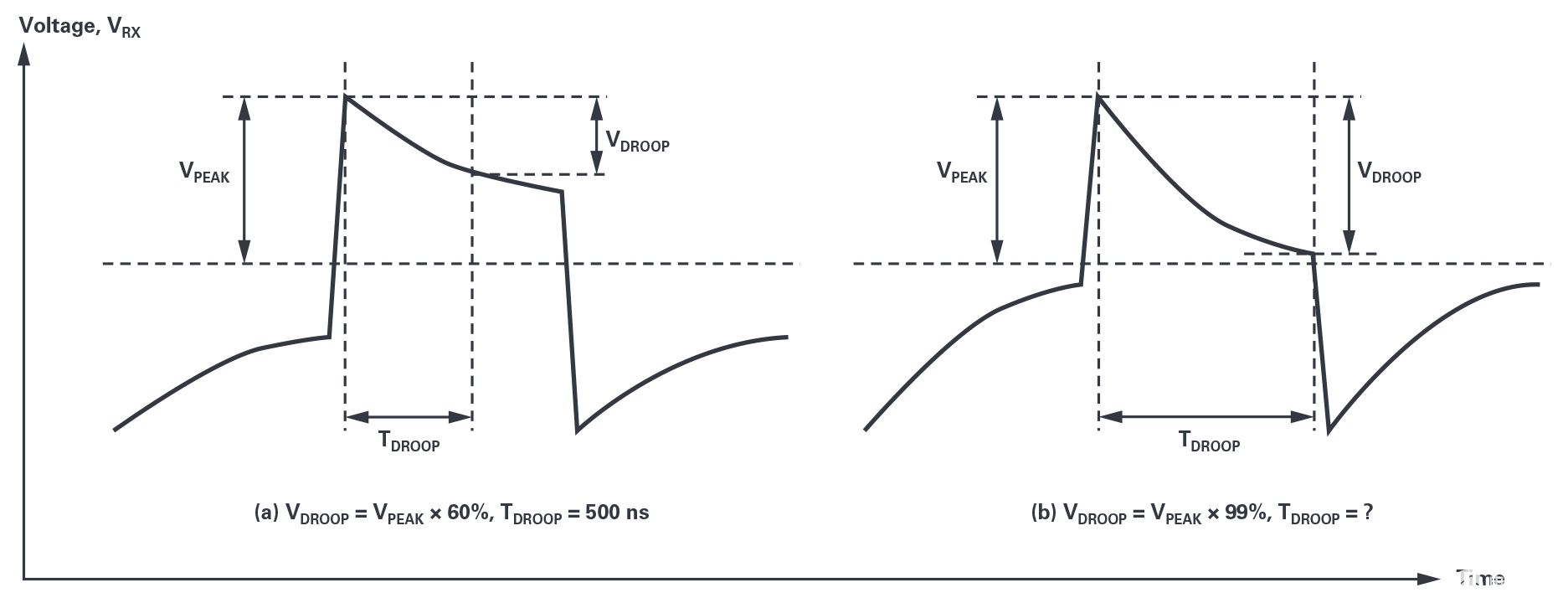

對于阻尼良好的系統,高通濾波器截止頻率與下降要求之間的關系由公式1給出。3

圖6.RS-422接收器的電壓下降和下降時間。

在向RS-485/RS-422通信系統添加SPI幻象電源時,很明顯,最小可能的SPI SCLK速率將受到幻象電源濾波器組件的限制。

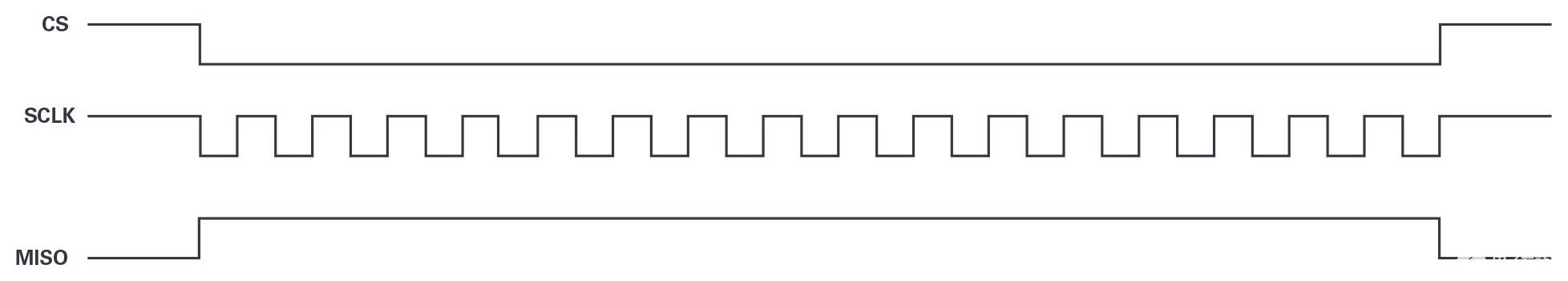

為了實現無位差錯的可靠通信,需要考慮最壞情況下的最小SPI SCLK,例如,所有SPI MISO采樣位均為邏輯高電平,如圖7所示。如果所有采樣的MISO位都是邏輯高電平,則會導致比特率低于系統SPI SCLK。例如,如果SPI SCLK為2 MHz,并且所有16位均為邏輯高電平,則幻象電源LC濾波器網絡的等效SPI MISO比特率為125 kHz。

圖7.SPI協議,帶MISO 16位突發,全邏輯高電平。

如“時間同步和電纜長度”一節所述,更長的電纜需要較低的SPI SCLK速率。但是,幻象電源限制了可能的最低SPI SCLK速率。平衡這些相反的要求需要仔細選擇和表征無源濾波器元件,尤其是電感器。

無源元件選擇

選擇合適的功率電感器時,需要考慮許多參數,包括足夠的電感、額定/飽和電流、自諧振頻率(SRF)、低直流電阻(DCR)和封裝尺寸。表1給出了選定的功率電感器和感興趣的參數。

額定電流需要滿足或超過遠程供電MEMS傳感器節點的總電流要求,并且額定飽和電流需要大得多。

電感不會對高于其引用SRF的交流數據呈現高阻抗,并且在某一點將開始具有容性阻抗特性。所選電感SRF會將SPI上可以使用的最大SPI SCLK限制為RS-485/RS-422物理層,如表1所示。在長電纜上工作時,可能無法到達電感SRF;例如,可能無法通過 10 m 的電纜達到 11 MHz(部件號 744043101 的 SRF)的 SPI SCLK 速率。在其他情況下,當在長電纜上工作時,電感SRF可以達到較低的SPI SCLK速率(2.4 MHz,1.2 MHz)。如前所述,在幻象電源濾波器網絡中使用時,電感也會限制盡可能低的SCLK速率。

較大的電感值采用 12.7 mm × 12.7 mm 封裝,而較小值的電感器采用 4.8 mm × 4.8 mm 封裝。

表2顯示,由于物理限制(內部繞組),在減小電感尺寸的相反要求之間進行權衡具有挑戰性。

| 部件號 | 升(微高) | 我額定(毫安) | 自諧振頻率 (SRF) (兆赫) | 直流電阻 (Ω) | 包裝尺寸(毫米) |

| 744043101 | 100 | 290 | 11 | 0.6 | 4.8 × 4.8 |

| LPS8045B-105 | 1000 | 230 | 1.3 | 3.22 | 8.0 × 8.0 |

| 76877530 | 1000 | 300 | 2.4 | 3.3 | 7.8 × 7.0 |

| SDR0805-102KL | 1000 | 210 | 3.0 | 4.5 | 7.8 × 7.8 |

| 7687714222 | 2200 | 260 | 1.2 | 6.5 | 10 × 10 |

| SRR1208-222KL | 2200 | 280 | 0.65 | 4.2 | 12.7 × 12.7 |

| 參數 | 對封裝大小的影響 |

| 足夠高的電感 | 電感值越高,內部繞組越大,封裝尺寸越大。 |

| 更高的SRF | SRF 越高,內部繞組越少,尺寸越小。 |

| 更高的額定電流和飽和電流 | 內部繞組更少,但封裝尺寸更大。 |

| 低直流電 | 為了實現更低的DCR,電線需要更粗,繞組更少。 |

選擇合適的直流阻斷電容器的限制僅限于瞬態過壓額定值和直流電壓額定值。直流電壓額定值需要超過最大總線電壓偏置,如圖3所示。在電纜或連接器短路期間,電感電流將變得不平衡,并將被端接電阻耗散。隔直電容器需要額定峰值瞬態電壓,以防短路。例如,在電感飽和電流約為1 A的低功率系統中,相應的隔直電容的額定電壓應至少為50 V dc。4

系統實施

設計窗口和組件選擇

在長RS-485/RS-422電纜上擴展時鐘同步接口(如SPI)時,以及在同一雙絞線(幻象電源)上組合電源和數據時,圖8總結了本文中提到的設計約束。可能的最小SPI SCLK由幻象電源濾波器組件設置,這些元件在SPI數據線上高通濾波器數據。最大SPI SCLK由幻象功率電感自諧振頻率(SRF)或系統傳播延遲(以SPI SCLK值較低者為準)設置。

圖8.設計窗口約束。

表3提供了建議的電感和電容值,以及通過仿真圖5并使用圖6和公式1作為指導確定的相應最小SPI SCLK。這假設 V下垂是 V 的 99%峰.該最小SPI SCLK還考慮了最壞情況,如圖7所示,其中數據突發中的所有位均為邏輯高電平。相應的電纜長度使用圖2估算。最大SPI SCLK由系統傳播延遲或電感SRF值設置。

下面是一個計算示例。

要確定最大 SPI SCLK,請執行以下操作:

指定系統所需的電纜長度。在本例中,我們將選擇 10 m 的 RS-485/RS-422 電纜。

使用圖2確定系統可能的最大SPI SCLK。對于 10 m 的電纜,這大約是 2.6 MHz SPI SCLK。將最大SPI SCLK降額10%以允許LC元件容差,從而提供2.3 MHz的SPI SCLK。最大可能的SPI SCLK也可能受到所選電感的SRF的限制。

要確定最小 SPI SCLK,請執行以下操作:

考慮一個SPI協議,其中MISO線路上的所有位都是邏輯高電平。在本例中,我們將選擇16位SPI協議,其中16位SPI MISO數據將在32次SCLK轉換期間采樣。如果所有 16 位均為邏輯高電平,則有效比特率為 2.3 MHz / 32 = 72 kHz。

使用圖5和V上的72 kHz方波德克薩斯州、電纜 V 遠端的電壓波形接收可以模擬各種 L 和 C 值。隨著電纜長度的增加,電感值和電感封裝尺寸也會增加。電容值也會增加。

L 和 C 值的選擇是主觀的,取決于所需的下降設置,如圖 6 所示。對于此示例,我們將假設 V下垂= V峰×99%。

使用 100 μH 電感器和 3.3 μF 電容以及 V 上的 72 kHz 方波德克薩斯州產生 T下垂7 μs,其中 V下垂= V峰×99%。

一 噸下垂6 μs 至 7 μs 相當于 2.3 MHz 至 2.6 MHz SPI SCLK。

如果選擇100 μH (744043101)電感,則2.6 MHz的SPI SCLK低于11 MHz的電感SRF。

如果使用100 μH電感和3.3 μF電容,則元件PCB面積最小。當使用更大的電感器時,例如1000 μH或2200 μH,元件PCB面積可以增加三倍。理論最大值SPI SCLK由電感SRF設置,這在實踐中可能是不可能的,例如,在沒有時鐘補償的系統中,使用100 μH(744043101)在11 MHz時。

| L (μH) 和部件號 | 碳 (微F) | 最大SPI SCLK (MHz) | Max SPI SCLK Set By | Min SPI SCLK | 最大 RS-485/ RS-422 電纜長度 (m) |

| 100 (744043101) | 3.3 | 5.2 | 系統傳播延遲 | 2.6兆赫 | 10 |

| 1000 (76877530) | 4.7 | 2.4 | 電感器SRF | 700千赫 | 60 |

| 2200 (7687714222) | 10 | 1.2 | 電感器SRF | 350千赫 | >100 |

如果使用更大的電感,例如2200 μH,則需要在網絡中增加電容和電阻來抑制系統諧振。附加組件為藍色,標記為 R潮濕(1 kΩ) 和 C潮濕(47 μF),見圖9。

圖9.為更大的電感和電容濾波器添加額外的系統阻尼。

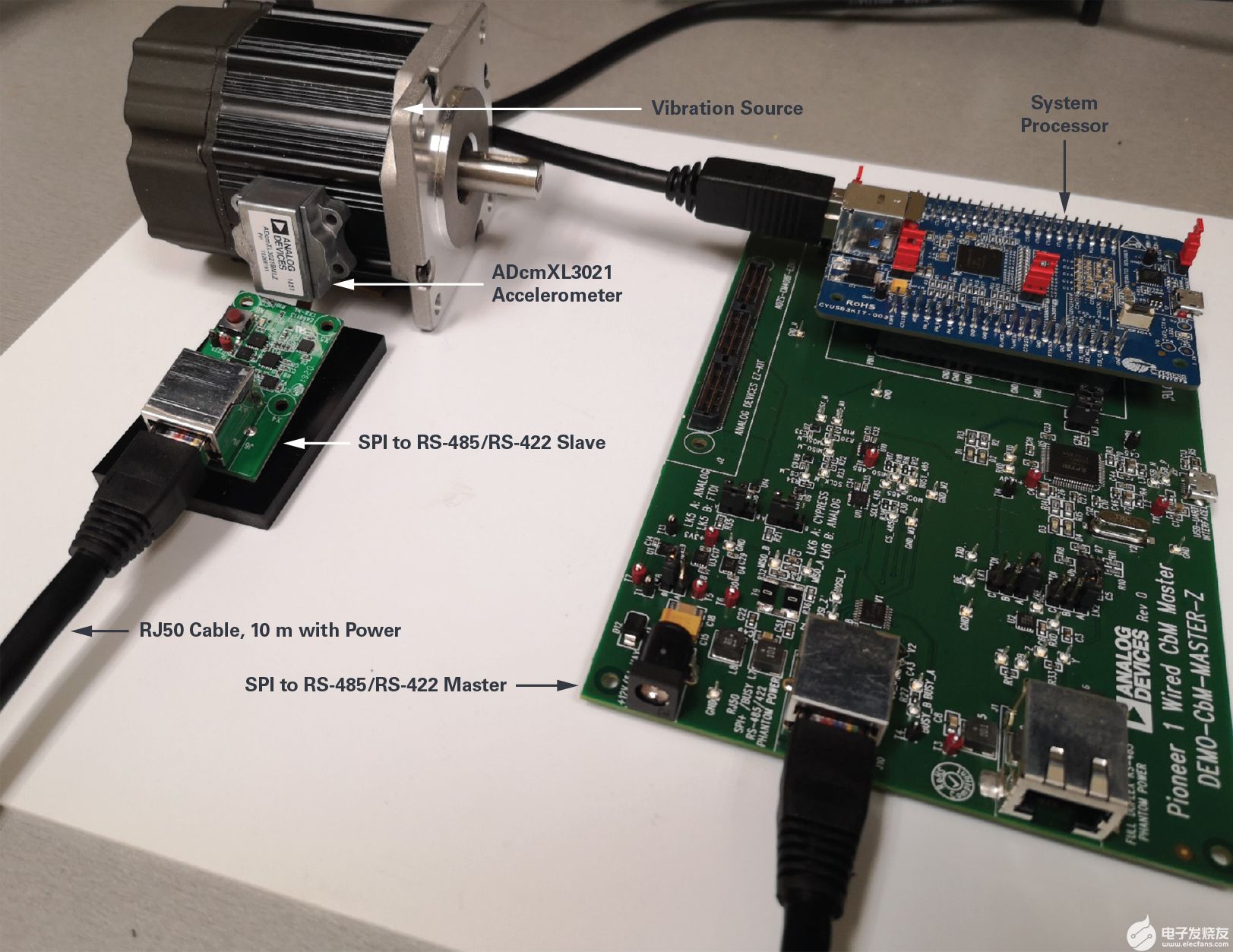

實驗設置

圖10顯示了ADI公司的有線CbM評估平臺,以下簡稱先鋒1。該系統使用本文第 1 部分中介紹的 SPI 至 RS-485/RS-422 設計解決方案。Pioneer 1還包括ADcmXL3021寬帶寬、低噪聲、三軸MEMS加速度計,該加速度計將高性能與各種信號處理相結合,以簡化CbM系統中智能傳感器節點的開發。SPI 至 RS-485/RS-422 從機將 ADcmXL3021 SPI 輸出擴展回主控制器 10 m 以上,用于振動數據分析。SPI 至 RS-485 設計使用幻象功率 100 μH 電感器和 3.3 μF 電容,以最大限度地減小從接口解決方案的尺寸,其尺寸為 26 mm × 28 mm(不包括接口連接器)。

圖 10.先鋒1有線狀態監測評估系統。

幻象電源線上的交流數據波形

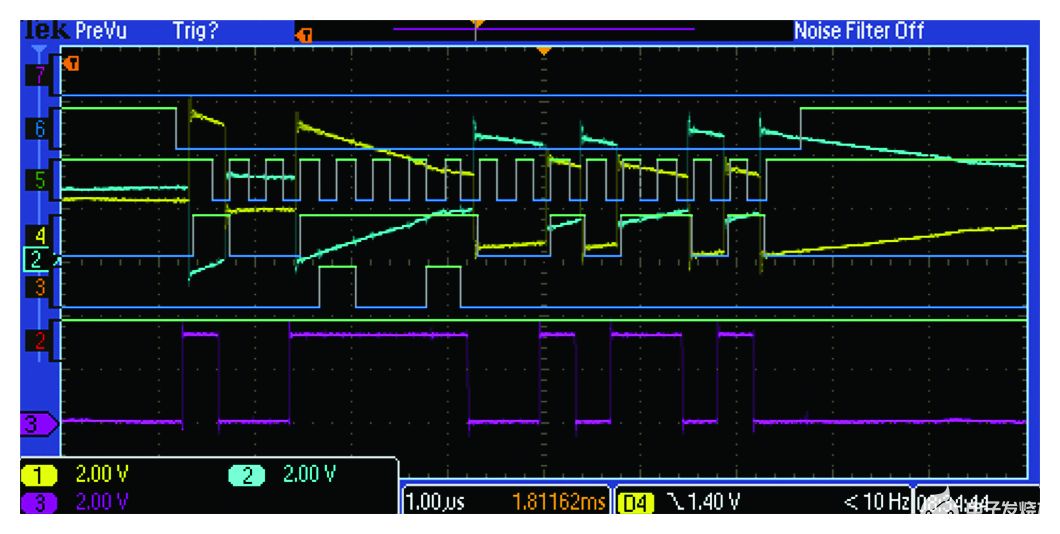

圖11和表4描述了在SPI主機和從機以及RS-485/RS-422差分電壓總線上測量的電壓。這些電壓是使用圖10中的示例應用設置測量的。模擬信號1(黃色)和2(藍色)是在SPI從輸出端測量的MISO信號(紫色)的差分總線電壓表示。數字信號4(黃色)顯示了在主控制器采樣的MISO。SPI主站的MISO信號與SPI從站MISO的極性和相位相匹配,傳播延遲很小。

圖 11.在SPI主機和從機以及RS-422差分電壓總線上測量的電壓。

| 參數 | 對封裝大小的影響 |

| 2 數字(紅色) | ADcmXL3021 忙于在主站測量 |

| 3 數字(橙色) | ADcmXL3021 MOSI 在主站測量 |

| 4 數字(黃色) | ADcmXL3021 味噌在主站測量 |

| 5 數字(綠色) | ADcmXL3021 標準數據終端測量 |

| 6 數字(藍色) | ADcmXL3021 CS 作為主設備測量 |

| 3 模擬(紫色) | ADcmXL3021 從站測得的味噌 |

| 2 模擬(藍色) | RS-422 Z引腳總線電壓狀態對應MISO;差分 Y 到 Z 對應于 3 個模擬(紫色)和 4 個數字(黃色) |

| 1 個模擬(黃色) | RS-422 Y引腳總線電壓狀態對應MISO;差分 Y 到 Z 對應于 3 個模擬(紫色)和 4 個數字(黃色) |

幻象電源線上的直流正確性

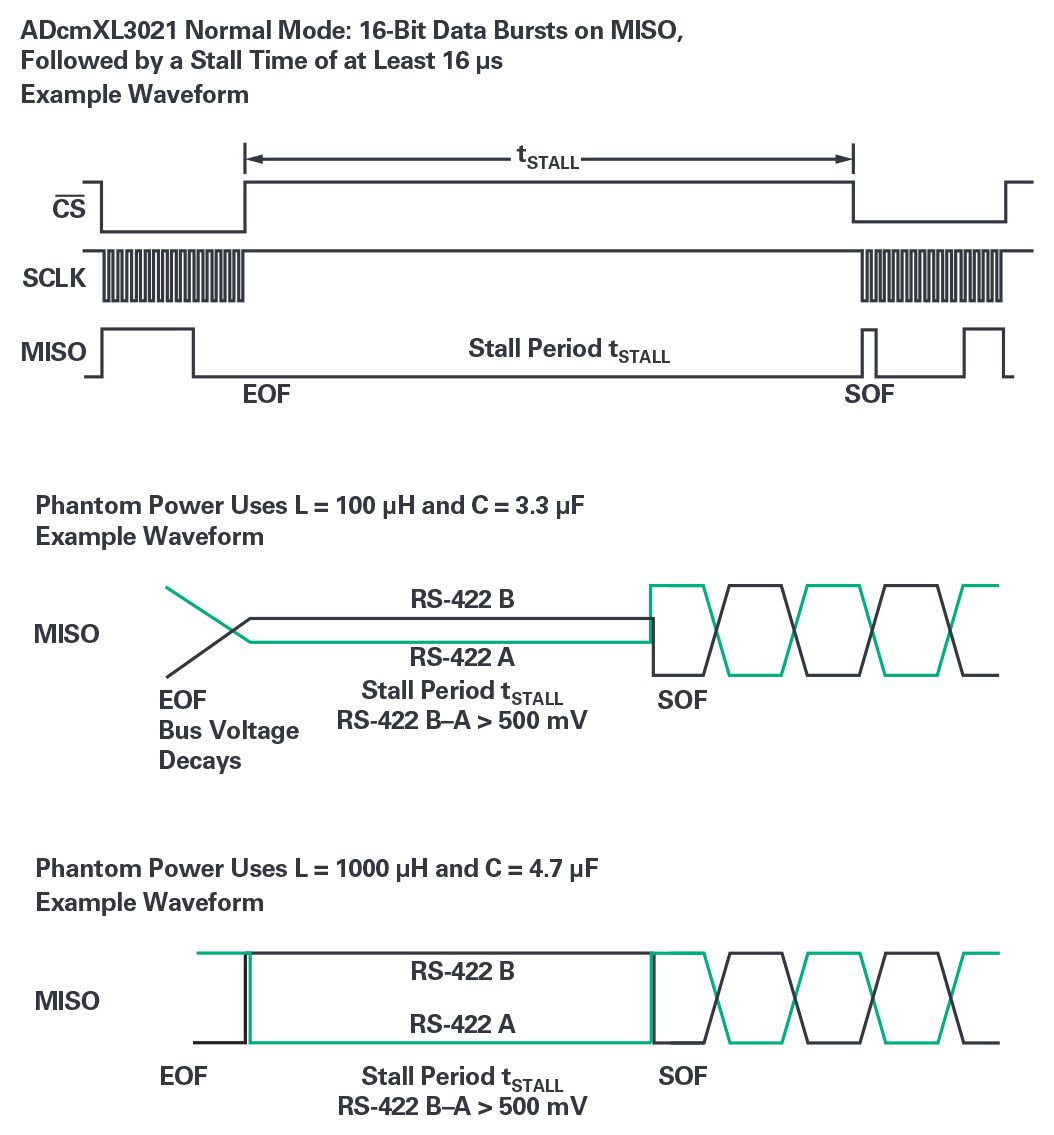

圖12顯示了ADcmXL3021的正常模式,其中包括一個SPI協議,該協議在MISO上發送16位數據突發,然后是失速周期(最小16 μs),然后是另一個16位數據突發。

圖 12.幻象電源線上的直流正確性。

在幻象電源網絡中,使用100 μH電感和3.3 μF電容:

在幀結束時(EOF),RS-485/RS-422總線電壓衰減回穩定的直流狀態。

失速周期直流穩態需要為500 mV>差分電壓RS-422 B-A,這反映了ADcmXL3021 MISO高阻態,并確保ADM4168E收發器輸出端的邏輯為0。如果使用500 Ω電阻,則可以保證這種空閑狀態的正確性,如圖4濾波電路所示。

然后,幀的下一個開始(SOF)將從低電平正確過渡到高電平,或者保持低電平,具體取決于ADcmXL3021的MISO數據輸出。

失速周期RS-485/RS-422總線穩態未與SPI SCLK邊沿對齊,因此隨機噪聲不會影響該時間段內的SPI MISO數據采樣。

在幻象電源網絡中,使用1000 μH電感和4.7 μF電容:

EOF、失速周期和SOF遵循ADcmXL3021 MISO輸出,總線電壓電平在失速期間不會衰減回500 mV最小直流穩態。可能會出現一些電壓電平衰減,但不會達到500 mV電平。

有線評估解決方案

ADI公司開發了Pioneer 1有線系統評估解決方案,以支持ADcmXL3021三軸MEMS加速度計。如本維基指南所述,先鋒1評估套件還可以借助維基指南中描述的擴展板支持表5中所示的MEMS器件。

| 部分 | 噪聲密度(微克/√赫茲) | 范圍(g) | 帶寬(赫茲) | # 軸 |

| ADcmXL3021 | 26 | 50 | 10000 | 3 |

| ADXL357 | 80 | 10, 20, 40 | 1000 | 3 |

| ADXL372 | 200 | 3200 | 3 | |

| ADXL355 | 20 | 2, 4, 8 | 1000 | 3 |

| ADXL313 | 250 | 0.5, 1, 2, 4 | 1600 | 3 |

| ADXL363 | 550 | 2, 4, 8 | 200 | 3 |

| ADXL375 | 200 | 1600 | 3 | |

| ADXL362 | 175 | 2, 4, 8 | 200 | 3 |

| ADXL345 | 420 | 2, 4, 8, 16 | 1600 | 3 |

| ADXL350 | 1, 2, 4, 8 | 1600 | 3 | |

| ADXL343 | 不 | 2, 4, 8, 16 | 1600 | 3 |

| ADXL312 | 340 | 1.5, 3, 6, 12 | 1600 | 3 |

審核編輯:郭婷

-

mems

+關注

關注

129文章

4075瀏覽量

192791 -

emc

+關注

關注

172文章

4121瀏覽量

186031 -

加速度計

+關注

關注

6文章

715瀏覽量

46618

發布評論請先 登錄

SPI至RS-422/RS-1設計解決方案的詳細物理層設計注意事項

RS-485和RS-422接口介紹

RS-232、RS-422和RS-485串行數據接口標準

使用RS-422和RS-485進行便捷,可靠的數據傳輸

USB/RS-485/RS-422/UT-850轉換器使用說

RS-485/RS-422 Circuit Implemen

RS-422 and RS-485 Application

RS-422和RS-485的應用說明資料免費下載

【理論】RS-232、RS-485、RS-422通信接口標準介紹

評論