如標(biāo)題所寫,我們今天聊一聊IC設(shè)計(jì)種的ECO。在展開關(guān)于ECO的概念之前,我們先大致捋下數(shù)字IC設(shè)計(jì)的流程,有助于我們后面的討論。

數(shù)字IC設(shè)計(jì)流程簡述

1、確定項(xiàng)目需求

根據(jù)市場或者芯片功能要求,設(shè)計(jì)芯片的spec,得到可行的芯片設(shè)計(jì)方案。

2、系統(tǒng)級(jí)設(shè)計(jì)

用系統(tǒng)建模語言對(duì)各模塊進(jìn)行描述

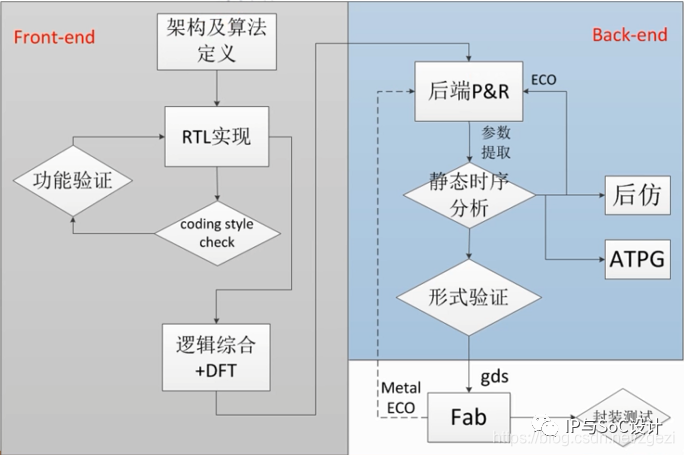

3、前端設(shè)計(jì)

RTL設(shè)計(jì)、功能仿真、硬件原型驗(yàn)證、電路綜合、DFT、STA

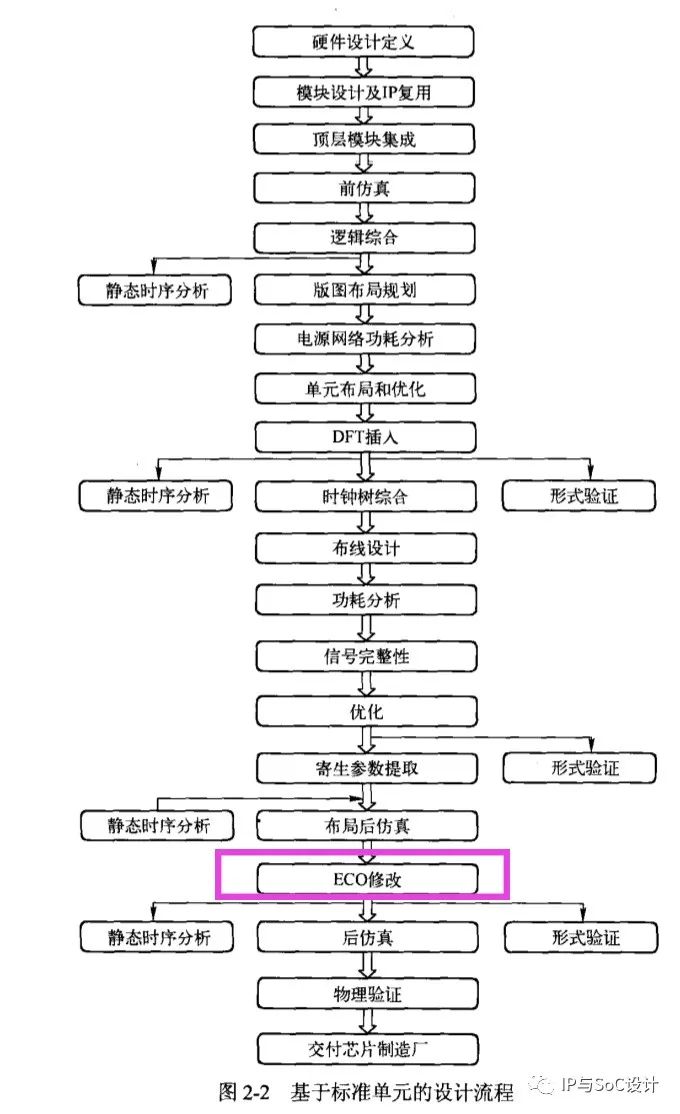

4、后端設(shè)計(jì)

版圖設(shè)計(jì)、物理驗(yàn)證、后仿真

在復(fù)雜的設(shè)計(jì)流程中,bug是難以避免的。對(duì)于芯片設(shè)計(jì)而言,bug自然是越早發(fā)現(xiàn)越好。但是仿真驗(yàn)證差不多,進(jìn)入RTL freeze階段后,一旦發(fā)現(xiàn)新的bug,就變得有些麻煩。

因?yàn)镽TL freeze前,你可以通過修改RTL來更正你發(fā)現(xiàn)的bug。然而RTL freeze之后,后端人員做好了floorplan,或者已經(jīng)開始布局布線,這個(gè)時(shí)候再去重新做一遍,既耗時(shí)耗力,又會(huì)惹怒后端。這顯然不是好的選擇。

如果這個(gè)時(shí)候即將tapeout,甚至已經(jīng)tapeout,根本就沒有機(jī)會(huì)修改RTL了。

這個(gè)時(shí)候,我們就需要ECO,來修正我們的失誤了。

什么是ECO?

ECO,即Engineering Change Order的縮寫,指工程改變命令。

什么意思呢?簡單來說就是手動(dòng)修改集成電路的過程,換句話說,就是直接手動(dòng)修改netlist。

一般應(yīng)用于數(shù)字芯片版圖設(shè)計(jì)。

對(duì)于數(shù)字IC設(shè)計(jì)而言,ECO這一步實(shí)際上是正常設(shè)計(jì)流程的一個(gè)例外。它是對(duì)設(shè)計(jì)的layout進(jìn)行局部的小范圍的修改和重新布線,而不影響到設(shè)計(jì)的其它部分的布局布線,所以其它部分的時(shí)序信息沒有改變。

根據(jù)功能的不同,ECO可以分為功能改變和非功能改變。功能改變是指由于來自客戶對(duì)設(shè)計(jì)的追加需求(spec改變)或者設(shè)計(jì)的最后階段發(fā)現(xiàn)芯片存在 bug 的情況下進(jìn)行的 ECO;而非功能改變則是為了在不改變 RTL 網(wǎng)表的基礎(chǔ)上修復(fù)部分時(shí)序以及串?dāng)_等問題而做的 ECO。

說到底,ECO的目的就是省錢省時(shí)間。

那么在不同階段,進(jìn)行ECO,有什么樣的區(qū)別呢?

在階段上,數(shù)字IC設(shè)計(jì)中的ECO大體可以分為:tapeout前的ECO,tapeout過程的ECO,tapeout后的ECO。

Tapeout前的ECO

在RTL freeze后,tapeout前這一階段,RTL已經(jīng)沒法修改,但是好歹也沒有進(jìn)入tapeout,還有補(bǔ)救的機(jī)會(huì)。

此時(shí)數(shù)字前端負(fù)責(zé)寫coding的工程師需要在final RTL的基礎(chǔ)上,通過寫ECO腳本的方式來實(shí)現(xiàn)功能上的ECO。

ECO代價(jià):時(shí)間成本,相對(duì)較小

Tapeout過程中的ECO

當(dāng)數(shù)字后端實(shí)現(xiàn)后的design,timing已經(jīng)符合signoff標(biāo)準(zhǔn),DRC已經(jīng)clean,LVS已經(jīng)pass,IR drop,MVRC,F(xiàn)ormality,DRCPLUS等都已經(jīng)pass。

但是,數(shù)字前端設(shè)計(jì)工程師還沒來得及做完大部分case的后仿,而且芯片又面臨著Timing-TO-Market的壓力。此時(shí),進(jìn)入tapeout階段。

為什么不給自己留更多余地呢?因?yàn)閒oundary會(huì)先做base layer的加工。只要后期仿真發(fā)現(xiàn)的問題,不需要再添加額外的cell,就不耽誤之前的tapeout(此處有點(diǎn)像流水線)。即使發(fā)現(xiàn)需要新加幾個(gè)cell,這個(gè)時(shí)候仍然可以通過替換后端實(shí)現(xiàn)過程中所加的ECO cell或者spare cell來實(shí)現(xiàn)。

ECO代價(jià):時(shí)間成本較大

Tapeout后的ECO

當(dāng)芯片已經(jīng)tapeout回來,我們?cè)跍y試過程中卻發(fā)現(xiàn)了必須修復(fù)的bug。這個(gè)時(shí)候做ECO的代價(jià)相對(duì)前面兩種,就要大很多。

改動(dòng)少的可能僅需要改幾層Metal layer,改動(dòng)大的話可能需要?jiǎng)邮畮讓覯etal layer,甚至重新流片。在此階段,前端設(shè)計(jì)工程師需要出具ECO方案,同時(shí)讓后端工程師進(jìn)行評(píng)估,主要評(píng)估需要改動(dòng)的層數(shù),timing 是否能快速收斂等方面的風(fēng)險(xiǎn)。

在一次次確認(rèn)后,敲定方案,進(jìn)行ECO。

ECO代價(jià):時(shí)間與金錢成本巨大

由此可見,即使ECO能夠亡羊補(bǔ)牢,但是為了節(jié)省更多的時(shí)間和金錢成本,還是盡早發(fā)現(xiàn)問題,盡早解決吧。

關(guān)于ECO的分類:

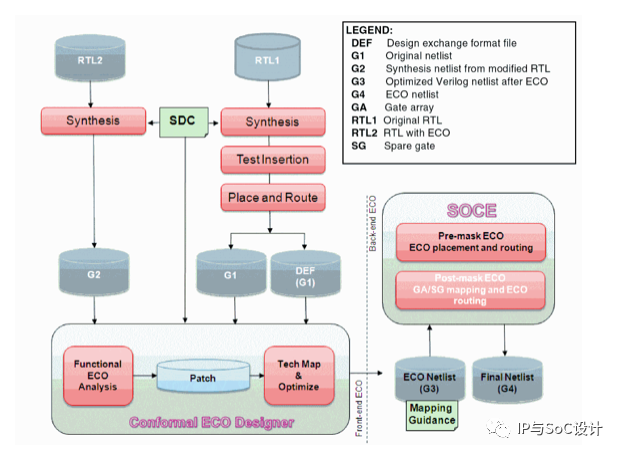

常見的ECO可以分為pre mask ECO和post mask ECO,也就是任何layer都可以動(dòng)到的ECO和只修改metal layer的ECO。

兩者的區(qū)別在于,pre mask ECO的晶體管和布線層都還沒有開始做出mask,此時(shí)可以往netlist里面添加cell。而post mask ECO的晶體管層已經(jīng)開始進(jìn)行加工了,但是布線層還沒有加工,還能修改,可以通過ECO改變各種已有cell的連線關(guān)系,但是不能添加新的cell,有一定局限。

換句話說,從freeze到tapeout之間的ECO叫pre mask ECO;tapeout之后,已經(jīng)加工完芯片的晶體管,但是還沒有做晶體管連線期間的ECO叫做post mask ECO。

Pre mask ECO:

Pre mask ECO比Post mask ECO要靈活得多。在tapeout之前,如果發(fā)現(xiàn)有任何需要修改的地方,都可以用這種方法。它可以改成百上千個(gè)單元。該操作主要是針對(duì)靜態(tài)時(shí)序分析和后仿真中出現(xiàn)的問題,對(duì)電路的網(wǎng)表直接進(jìn)行修改,待網(wǎng)表修改完畢之后反饋到PR工具中對(duì)標(biāo)準(zhǔn)單元的布局和連線進(jìn)行小范圍的改動(dòng)。當(dāng)然,直接對(duì)網(wǎng)表進(jìn)行修改是存在風(fēng)險(xiǎn)的,所以之后一定要進(jìn)行形式驗(yàn)證(formal verification),確保功能實(shí)現(xiàn)。

Post mask ECO:

Post mask ECO是利用預(yù)先留好的備用單元(Spare Cell),做的邏輯修改。如果后期發(fā)現(xiàn)Timing存在問題(或者想小動(dòng)Function),可以利用附近的Spare Cell搭配上層金屬連線來修改電路結(jié)構(gòu)。比起Pre mask ECO,這種ECO受限于Spare Cell的位置,所以它的修改規(guī)模十分有限。

Spare Cell:

Foundry提供一種服務(wù),允許客戶在wafer加工到poly以及M1層的時(shí)候,讓大部分wafer暫時(shí)停止加工,而少量wafer繼續(xù)加工直至完成。之后可以對(duì)這些完成了的wafer上的die進(jìn)行測試,如果發(fā)現(xiàn)存在功能或者時(shí)序上的問題,那么可以通過利用那些預(yù)布在die上的spare cell來解決。

由于絕大部分的金屬層都沒有加工,因此在不修改標(biāo)準(zhǔn)單元布局的情況下,只用改動(dòng)幾層金屬的mask并利用spare cell去修復(fù)這些問題。如此一來,也大大降低了流片的風(fēng)險(xiǎn)。而Post mask ECO則提供了一種根據(jù)silicon測試結(jié)果進(jìn)行Debug的方法。

Post mask ECO 可行的前提是設(shè)計(jì)里有足夠的可供新功能實(shí)現(xiàn)的cell, 如Spare cell, Freed cell, GA cell。

Freed cell,這些cell原本服務(wù)于原始的邏輯功能,但是因?yàn)檫壿嫻δ芨模会尫懦鰜恚热灰驯会尫殴士梢杂糜趤韺?shí)現(xiàn)新的功能。GA cell,是內(nèi)部晶體管沒有鏈接的cell,是可以被“編程”的cell,在做ECO 時(shí),通常用最底層金屬如M1 將GA cell 內(nèi)部的晶體管鏈接起來,以實(shí)現(xiàn)對(duì)應(yīng)的邏輯功能,如:與或非、選擇器、寄存器等。

而Post mask ECO的修復(fù)則受制于這些cell的位置,可以說是不太靈活了。

從邏輯和物理來看,ECO又可以分為Logic ECO和Physical ECO。Logic ECO是對(duì)網(wǎng)表的邏輯功能的修改。在芯片設(shè)計(jì)的后期階段,前端工程師可能會(huì)發(fā)現(xiàn)設(shè)計(jì)上的某些bug,進(jìn)而需要對(duì)電路做修改,而此時(shí)的schedule已經(jīng)不允許進(jìn)行重新綜合,因此會(huì)選擇在PR的網(wǎng)表上進(jìn)行邏輯修改,一般情況是會(huì)增加一些邏輯或者將某些邏輯的net重新連接;而Physical ECO主要是針對(duì)PR工具無法完全修復(fù)的問題進(jìn)行手動(dòng)修正。一般包括Timing ECO,drc fix等。

ECO的實(shí)際運(yùn)用與技巧

對(duì)于版圖工程師來說,經(jīng)常會(huì)碰到一些function ECO的需求:

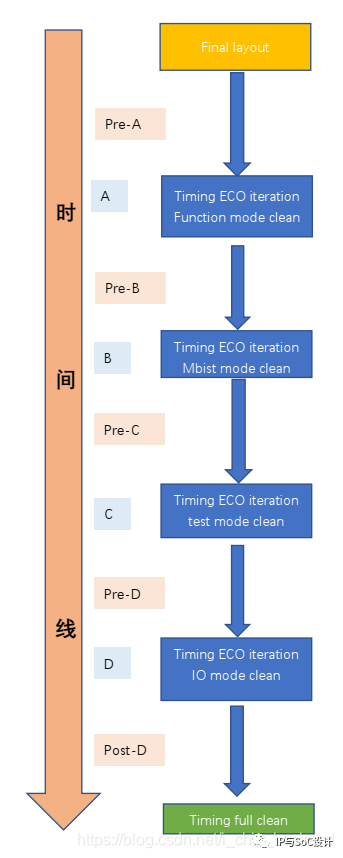

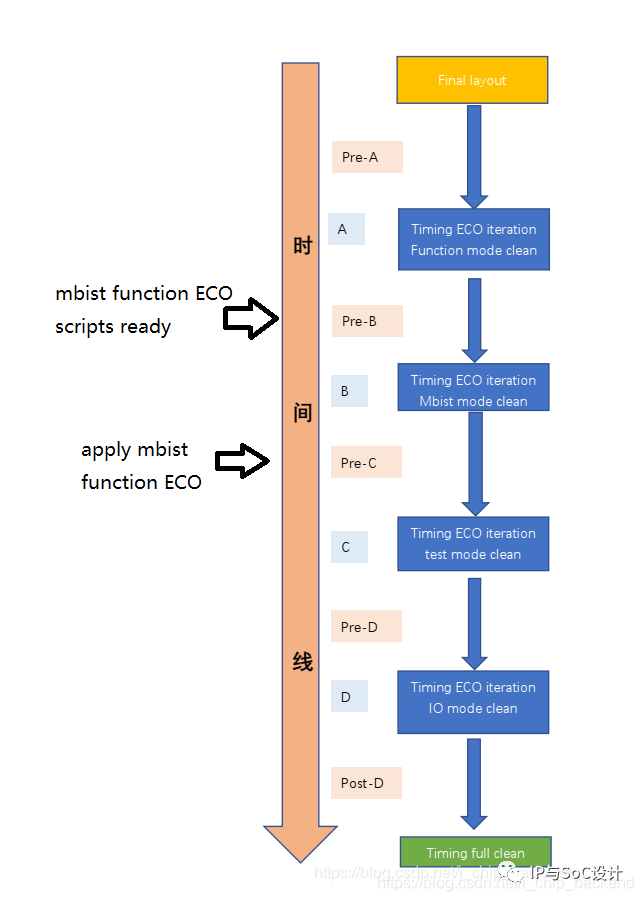

從上圖可以看到,為了保證數(shù)據(jù)庫有優(yōu)先級(jí)的收斂,最后的timing ECO會(huì)分為幾個(gè)主要步驟

·功能模式的時(shí)序修復(fù):function mode

·存儲(chǔ)器自測模式的時(shí)序修復(fù):mbist mode

·其他測試模式的時(shí)序修復(fù):test mode

·芯片接口時(shí)序修復(fù):IO mode

功能模式的重要性、工作量和難度都是最大的,需要盡早修復(fù),然后是其他的模式。整個(gè)流程基本上是按照步驟和優(yōu)先級(jí)完成整個(gè)芯片的時(shí)序修復(fù)的。

改變功能的ECO被稱之為function ECO,但是實(shí)際上,這種ECO可能是針對(duì)真正的function mode的,也有可能是針對(duì)mbist 邏輯的,或者有可能是針對(duì)at-speed test mode的。

由于function ECO會(huì)引起潛在的timing arc的變化,因此帶入function ECO的時(shí)間點(diǎn)是有講究的。一般來講,只會(huì)在一種模式的timing修復(fù)告一段落的時(shí)候,才會(huì)帶入這個(gè)模式的function ECO。

假如在時(shí)間節(jié)點(diǎn)Pre-B,前端準(zhǔn)備好了一個(gè)比較大的function ECO,這個(gè)ECO是給mbist服務(wù)的。通常需要先驗(yàn)證這個(gè)腳本的正確性,如果腳本本身沒問題,在這個(gè)Pre-B的時(shí)候并不帶入,因?yàn)檫@個(gè)時(shí)候整個(gè)mbist的時(shí)序還不夠穩(wěn)定。

等到了Pre-C的時(shí)間節(jié)點(diǎn),mbist的時(shí)序修復(fù)基本完成的階段,這時(shí)可以代入這個(gè)ECO。理論上講,新出來的timing violation都是由于這個(gè)腳本引起的。

增量設(shè)計(jì)工作模式,是ECO階段的重重之重,任何違背增量設(shè)計(jì)方案的舉動(dòng),都會(huì)造成局部損耗,甚至更糟的結(jié)果。

功能ECO的腳本生成的探究和技巧

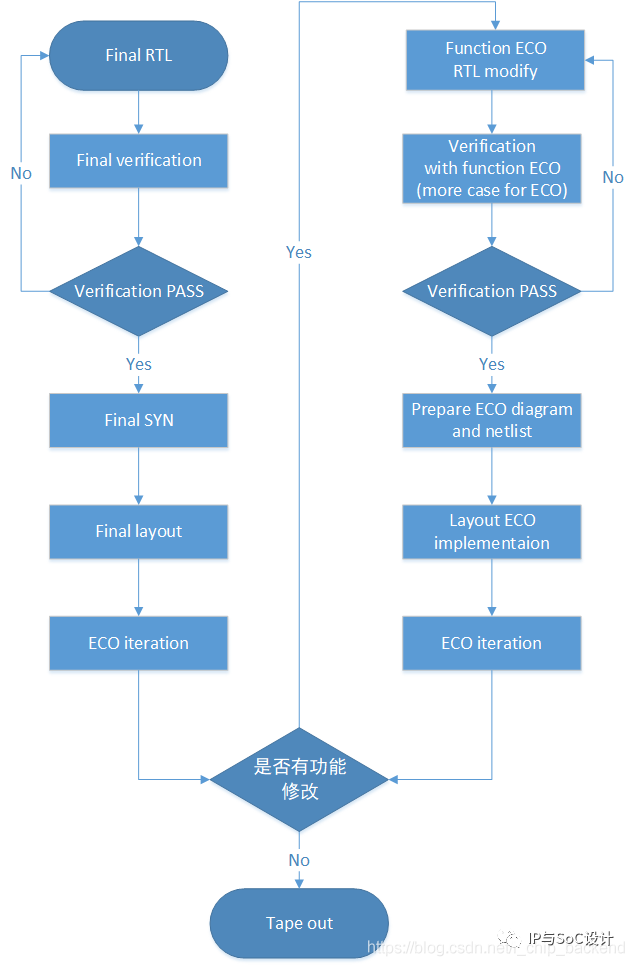

后端一般會(huì)在最終layout的節(jié)點(diǎn),給前端分享最終layout版本的網(wǎng)表。一般為了閱讀方便,后端都是給前端一個(gè)不帶PG信息的netlist。前端同學(xué)在完善數(shù)據(jù)庫的過程中,同時(shí)也會(huì)對(duì)各種問題進(jìn)行評(píng)估,最終給出解決方案:

·軟件改動(dòng)

·約束用戶行為

·硬件改動(dòng)

如果有任何需要在硬件方面做的功能修改,前端會(huì)先保證RTL修改、驗(yàn)證完成后,對(duì)相應(yīng)的final layout的網(wǎng)表進(jìn)行修改。

綜上所述,一個(gè)function ECO的誕生過程大抵如下:

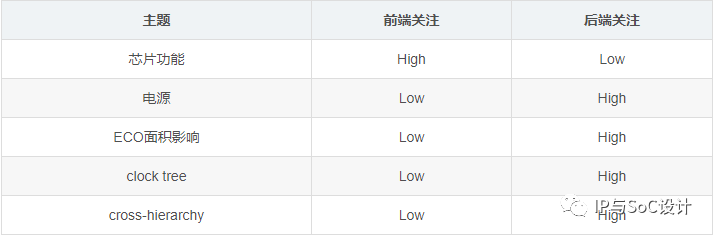

前端主要關(guān)注功能,后端主要關(guān)注實(shí)現(xiàn),對(duì)于下面的幾個(gè)主題的關(guān)注度,這里展示一下:

前端基于final layout的網(wǎng)表,改出來一版帶function ECO的功能網(wǎng)表,這個(gè)流程基本就算大功告成了。

ECO版圖實(shí)現(xiàn)的技巧和經(jīng)驗(yàn)

在ECO中,版圖的實(shí)現(xiàn)是非常重要的步驟。是否能完成STA的腳本期望,是數(shù)據(jù)庫能否走向收斂的關(guān)鍵點(diǎn)。一般的STA對(duì)應(yīng)的ECO和相應(yīng)的修復(fù)方法如下:

ECO的物理實(shí)現(xiàn)就是兩種情形

·size_cell

·add buffer

這里邊最會(huì)產(chǎn)生的影響其實(shí)是面積和器件的位置變動(dòng)(dis-placement)

器件的位置變動(dòng)帶來的影響都可能導(dǎo)致ECO無法如期進(jìn)行,因?yàn)樵袛?shù)據(jù)庫的cell的放置被調(diào)整,之前的繞線需要做相應(yīng)的調(diào)整,同時(shí)帶來更多的timing/驅(qū)動(dòng)能力的問題,這樣就會(huì)給數(shù)據(jù)庫帶來不期望的抖動(dòng)。

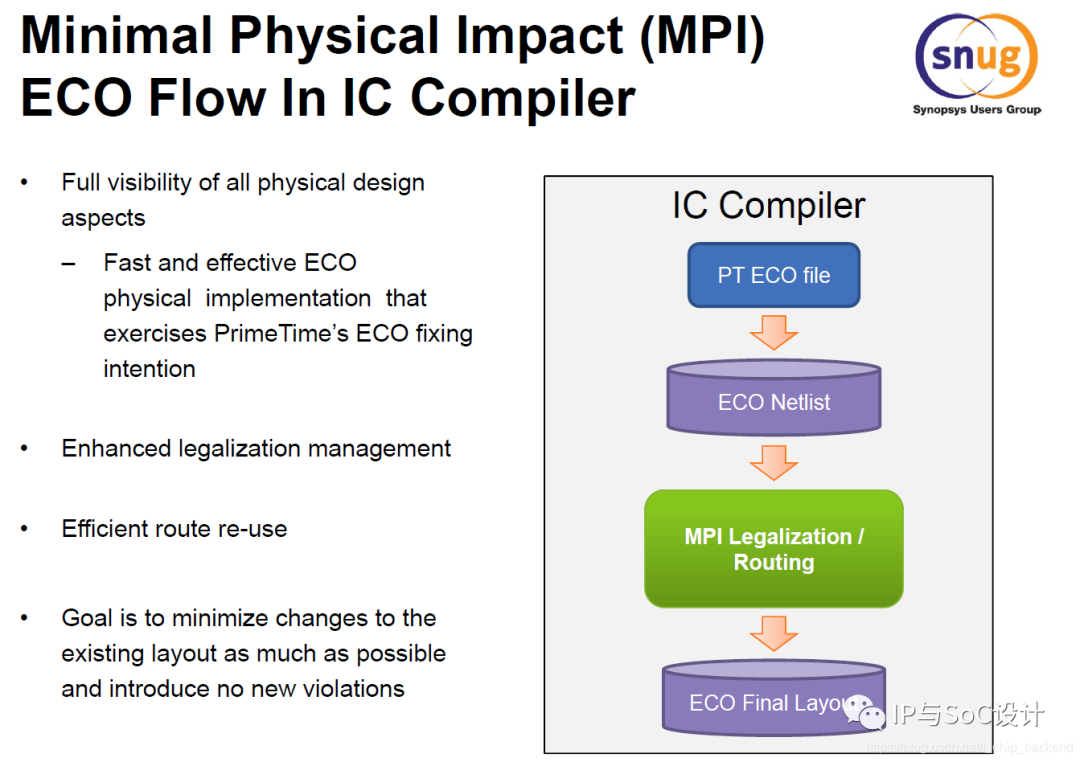

為了盡可能保證原有數(shù)據(jù)庫的狀態(tài),這里引入一個(gè)新名詞:Minimal Physical Impact Flow(MPI)。

較小的dis-placement帶來更為穩(wěn)定的版圖數(shù)據(jù),繞線的挑戰(zhàn)也比較小,這是MPI的核心思想。

ECO收尾階段的風(fēng)險(xiǎn)和注意點(diǎn)

在ECO收尾階段,所有決策和行動(dòng)都需要慎重,否則出了問題就叫苦不迭了。

先說結(jié)論,兼顧metal fill,MCMM以及VT cell的靈活使用,是ECO后期成功收斂的關(guān)鍵要素。

MCMM,全稱為:multi_corner和multi_mode,而multi_corner(PVT):process/voltage/tmperature。

multi_mode:function/scan_shift/scan_capture。

看到它的全稱,想必你就明白它的重要性了。

至于metal fill,先進(jìn)工藝是需要fill的支持,來保證流片的物理需求,fill是基于繞線和布局的,如果繞線或者布局改變了,就需要重新跑fill。所以在先進(jìn)工藝,一定不能忽略fill對(duì)timing的影響,tapeout之前,一定要保證fill的信息完全和真實(shí)的數(shù)據(jù)庫匹配,這樣跑出來的timing才完整可信。

ECO的時(shí)序信息通常是增量示的,除非你改變了繞線。這是需要在ECO后期階段牢記的一點(diǎn)。

對(duì)于一個(gè)數(shù)據(jù)庫,經(jīng)常會(huì)遇到在接近TO的ECO的迭代中,會(huì)冒出一些和修復(fù)timing沒有關(guān)系的微小的setup/hold violation。這個(gè)大多是由于繞線的細(xì)微改變,而導(dǎo)致的時(shí)序變化。這個(gè)時(shí)候,VT cell就會(huì)派上用場。

時(shí)間是TO前最值錢的,使用VT cell進(jìn)行ECO,最大的方便時(shí)省略了ECO 繞線、寄生參數(shù)的抽取和STA的re-run。這三個(gè)步驟的時(shí)間是非常長的。有了VT cell的幫忙,這些時(shí)間統(tǒng)統(tǒng)可以省略。

經(jīng)歷了這么一系列流程與注意事項(xiàng),我們終于可以完成ECO,確保tapeout順利,獲得一塊good chip。

以上,經(jīng)過筆者粗淺的總結(jié)和整合,將ECO相關(guān)的知識(shí)點(diǎn)與大家分享。

審核編輯 :李倩

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1360瀏覽量

105861 -

ECO

+關(guān)注

關(guān)注

0文章

52瀏覽量

15201

原文標(biāo)題:科普:數(shù)字IC設(shè)計(jì)中的ECO是什么?

文章出處:【微信號(hào):IP與SoC設(shè)計(jì),微信公眾號(hào):IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

【RA-Eco-RA6M4開發(fā)板評(píng)測】+01+開箱測評(píng)+UART+PWM+LED

開關(guān)式霍爾IC的應(yīng)用實(shí)例

霍爾IC的原理和分類

GaAs IC 1 位數(shù)字衰減器 skyworksinc

GaAs IC 1 位數(shù)字衰減器 15 dB LSB DC-2 GHz skyworksinc

PPS注塑IC元件封裝中的應(yīng)用優(yōu)勢與工藝

【RA-Eco-RA4M2開發(fā)板評(píng)測】2+uart方式

有獎(jiǎng)試用!!RA-Eco-RA4M2-100PIN-V1.0開發(fā)板試用活動(dòng)報(bào)名

AN-643:數(shù)字可變光衰減器中ADuC832 MicroConverter IC和對(duì)數(shù)轉(zhuǎn)換器AD8305的閉環(huán)控制電路實(shí)現(xiàn)

評(píng)論