相控陣雷達系統利用許多發射和接收通道來發揮作用。從歷史上看,這些平臺是使用單獨的發射和接收集成電路(IC)構建的。這些系統使用單獨的芯片用于發射(Tx)電路中的數模轉換器(DAC)和接收(Rx)電路中的模數轉換器(ADC)。這種分離導致了許多大尺寸、高成本、高功耗的系統,以實現實現所需功能所需的通道數。由于制造和校準的復雜性,這些系統通常也需要較長的上市時間。然而,最近一種利用集成收發器的方法將許多曾經被認為是不同的功能組合到單個IC中。使用這些 IC 可實現小尺寸、低功耗和成本、高通道數相控陣雷達平臺,并加快上市時間。

集成收發器簡介

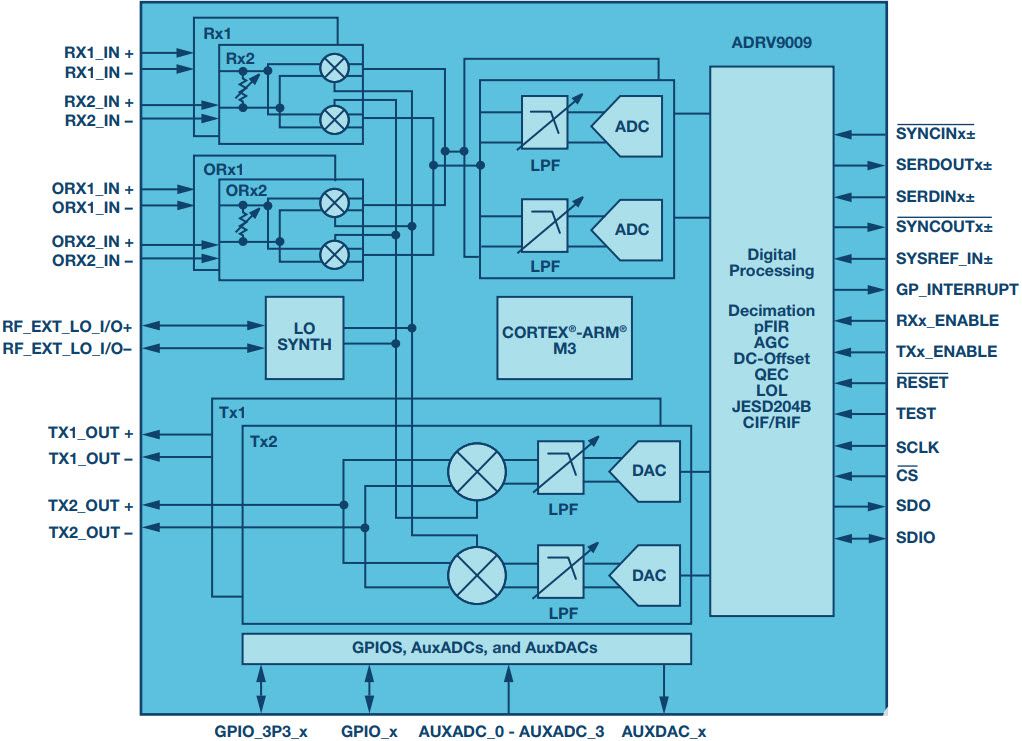

集成收發器(如圖1所示)將多種功能組合到單個IC上。例如,新型收發器將DAC、ADC、本振(LO)頻率合成器、微處理器、混頻器等集成到單個12 mm×12 mm單片產品中。此外,該產品結合了兩個接收通道和兩個發射通道,以及數字信號處理(DSP)組件,以實現系統所需的瞬時帶寬。還提供應用程序接口(API),用于在客戶平臺上操作收發器。增益和衰減控制可以通過利用片上前端網絡來實現。提供內置初始化和跟蹤校準例程,以提供許多通信和軍事應用所需的性能。

圖1.ADRV9009是集成收發器的一個示例,它將許多功能集成到單個IC中。

這些集成收發器能夠通過注入稱為REF_CLK的單個參考時鐘信號來創建發射器和接收器所需的所有時鐘信號。 然后,片內鎖相環(PLL)合成DAC/ADC采樣、LO生成和微處理器時鐘所需的所有時鐘。如果內部LO相位噪聲不足以滿足客戶應用的需求,用戶可以選擇注入自己的低相位噪聲外部LO。

來自該器件的數據通過標準化的JESD204b多千兆串行數據接口卸載。該接口可實現大量同時數據接收和傳輸。新的集成收發器解決方案有助于提供接口IP,以簡化客戶的上市時間。如果需要確定性延遲和數據同步,用戶可以利用內置的多芯片同步(MCS)功能并發出SYS_REF信號,作為初始通道對齊序列(ILAS)的主定時參考。1

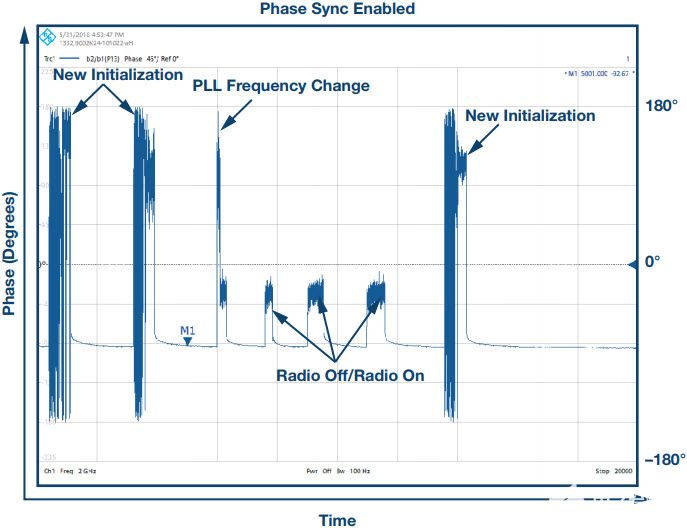

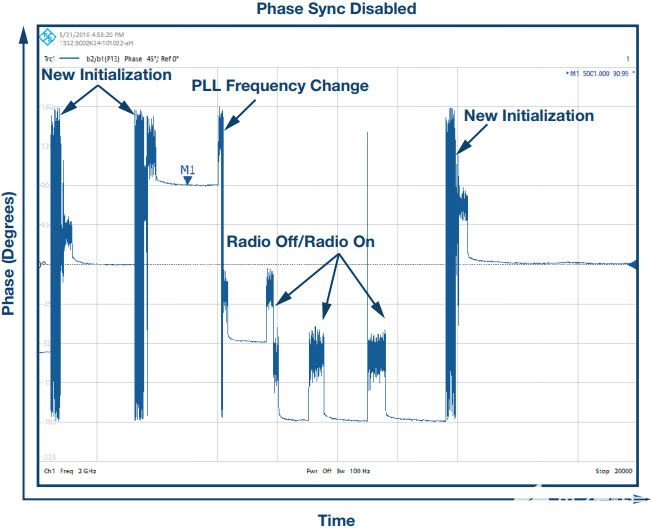

此外,使用內置的RFPLL相位同步功能,Tx或Rx通道的LO相位可以相對于主參考相位確定。通過同時利用MCS和RFPLL相位同步功能,可以在初始化器件、調諧或在軟件中打開和關閉無線電時復制相位對齊。新型集成收發器的示例提供了啟用這些功能的確定性相位。

圖2.內置的RFPLL相位同步功能為系統提供了相對于主參考源的確定性相位關系。

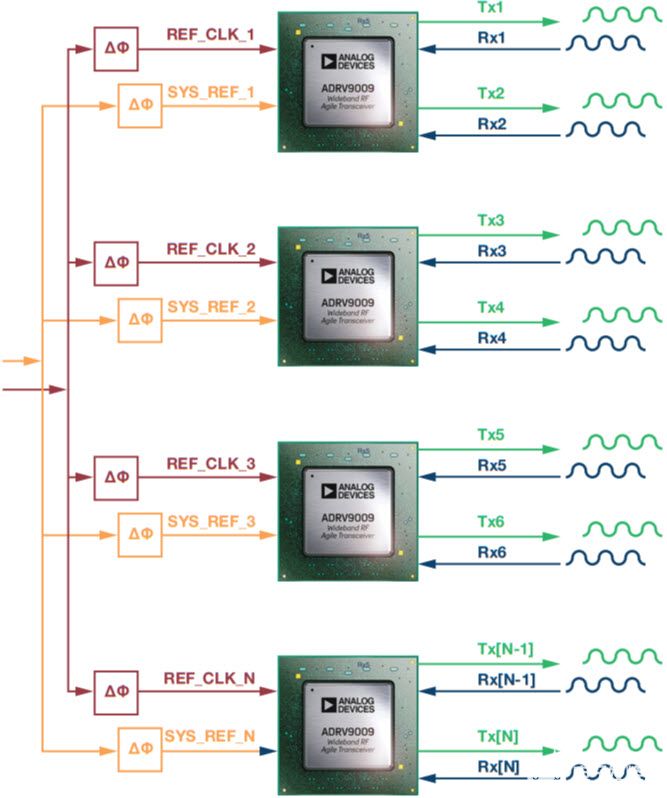

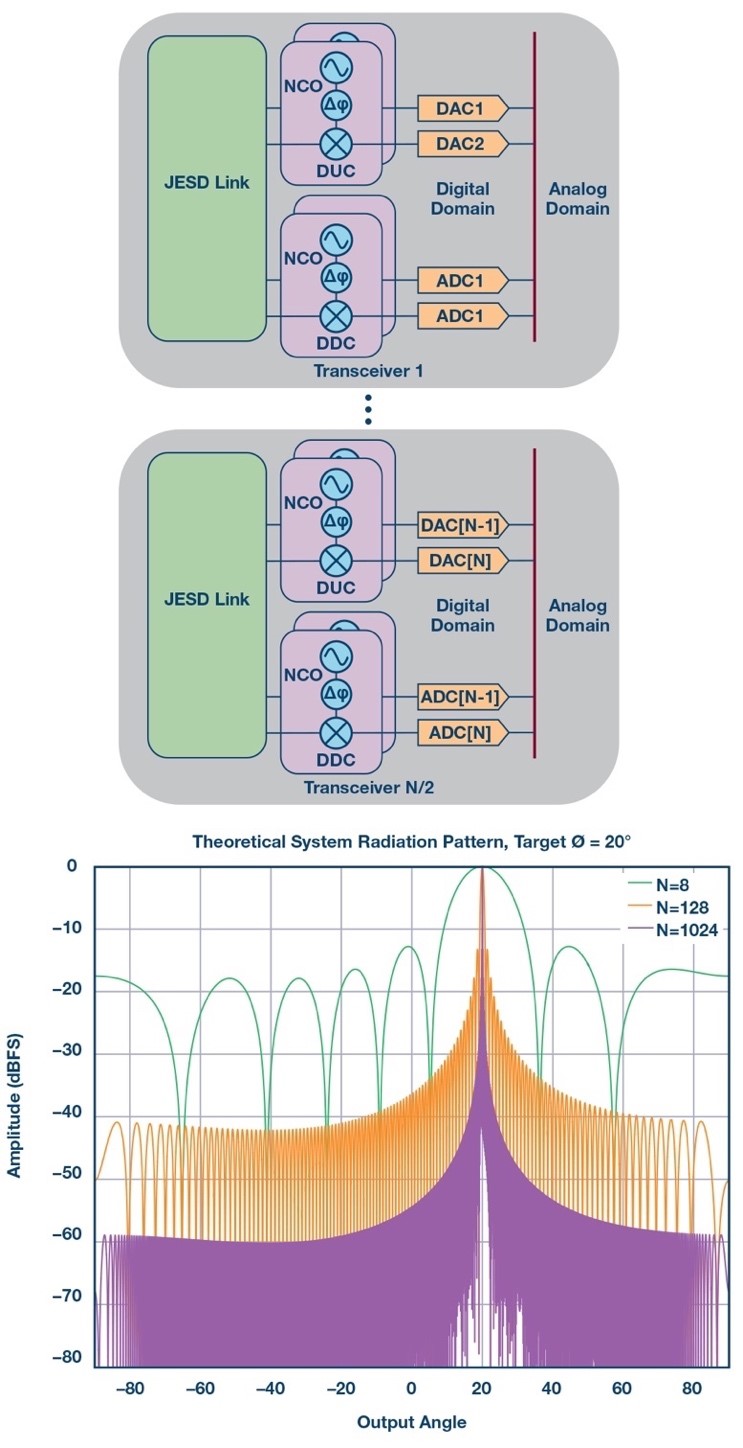

使用多個集成收發器

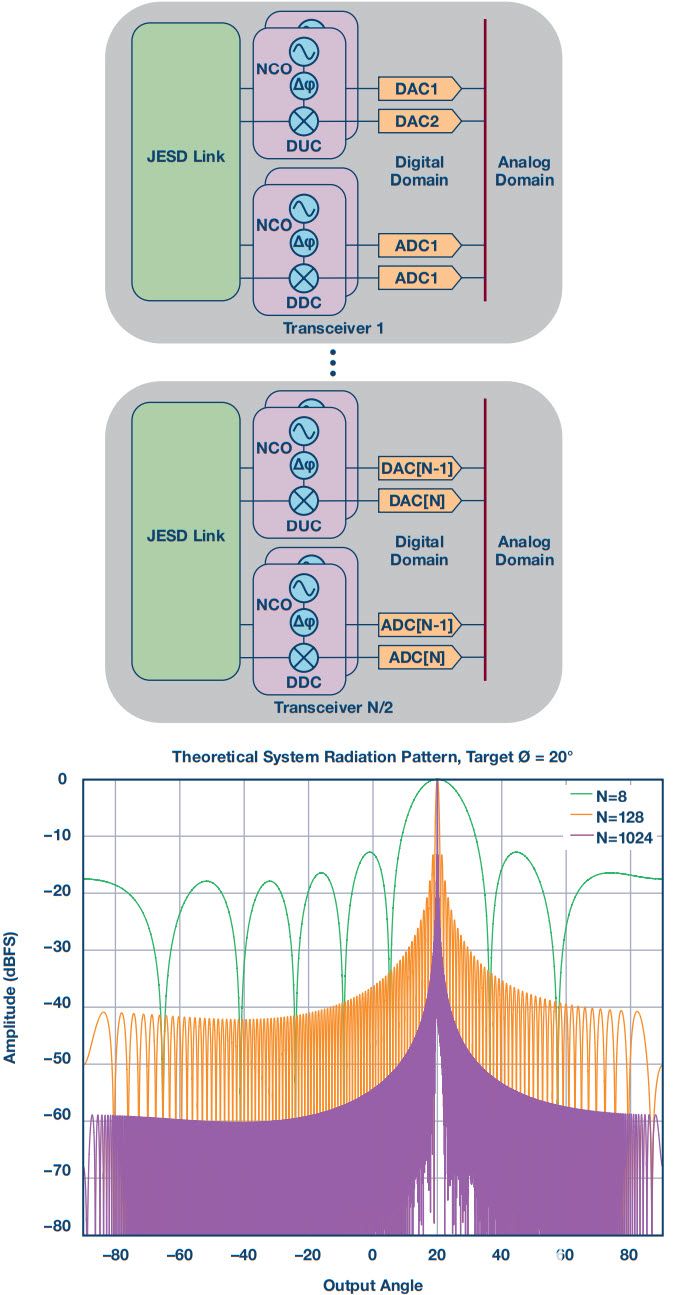

如果一個系統需要兩個以上的接收器和兩個發射器,用戶仍然可以通過使用多個集成收發器,從單片Rx和Tx通道實現的小尺寸中受益。此技術的示例如圖 3 所示。利用并發SYS_REF脈沖同時觸發所有IC的內部分壓器,可以同步多個集成收發器。這些SYS_REF脈沖可以由時鐘芯片或基帶處理器發出,具有可編程延遲,以解決到各種IC的路由之間的任何長度不匹配。數據路徑和跨多個芯片的多個LO都具有確定性。

圖3.可以使用多個集成收發器來增加系統的通道數。

集成收發器作為相控陣雷達平臺的骨干

通過使用同步集成收發器增加通道數,這些器件就可以作為相控陣雷達平臺的骨干。當組合相位和幅度對齊的Tx和Rx通道時,使用多個集成收發器已經顯示出系統級動態范圍、雜散和相位噪聲的改善。

片上DSP特性,如數控振蕩器(NCO)和數字上變頻器(DUC)或數字下變頻器(DDC),現在可以在單個IC中實現系統級雜散去相關方法。2

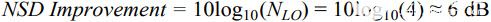

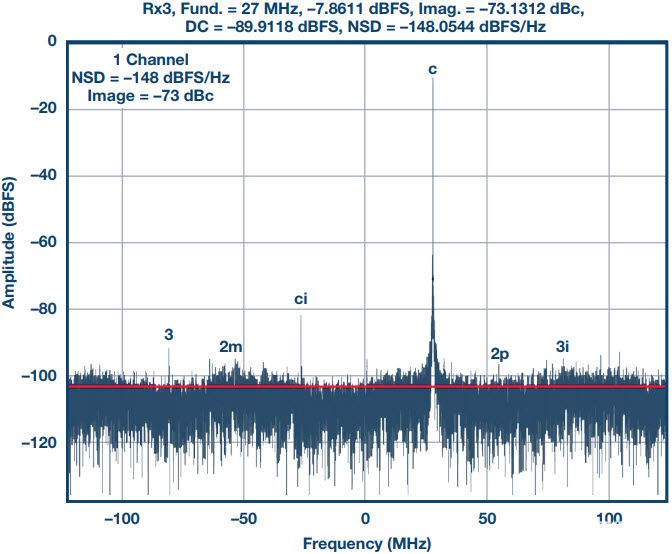

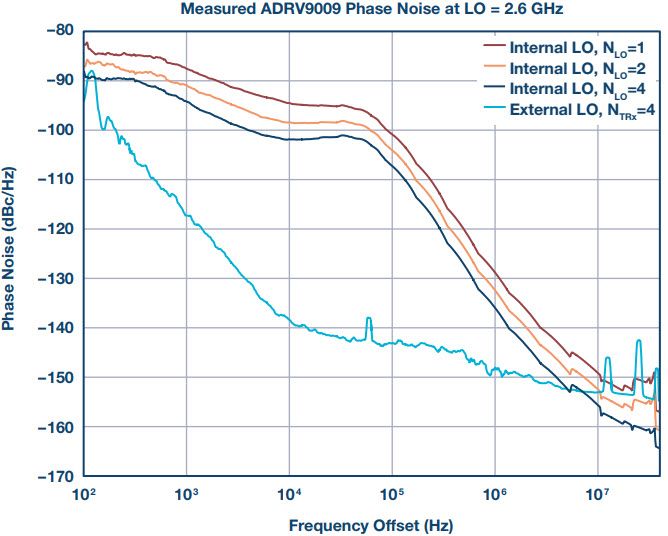

使用多個集成收發器組合接收器通道,既改善了系統級噪聲頻譜密度(NSD),又改善了雜散性能。這通過降低系統的有效本底噪聲,同時保持通道滿量程功率,改善了相控陣雷達系統的動態范圍。圖4顯示了組合多達8個集成收發器Rx通道以有效增加相控陣系統中實現的位數時所測得的系統級結果。請注意,當從一個通道變為八個通道時,NSD和每個圖中紅線所示的計算本底噪聲提高了~6 dB。這是因為,盡管總共有八個通道,但只有四個不同的、不相關的LO(即N瞧=4) 在用于創建這八個通道的四個集成收發器中。這導致改進

這接近集成收發器提供的實驗結果。此外,不需要的鏡像頻率以不相關的方式相加,以實現系統級雜散性能改進。隨著通道數量的增加,這種改進可以進一步增強,從而實現可擴展的系統。

圖4.使用ADRV9009集成收發器組合Rx通道可降低噪聲頻譜密度并改善動態范圍。

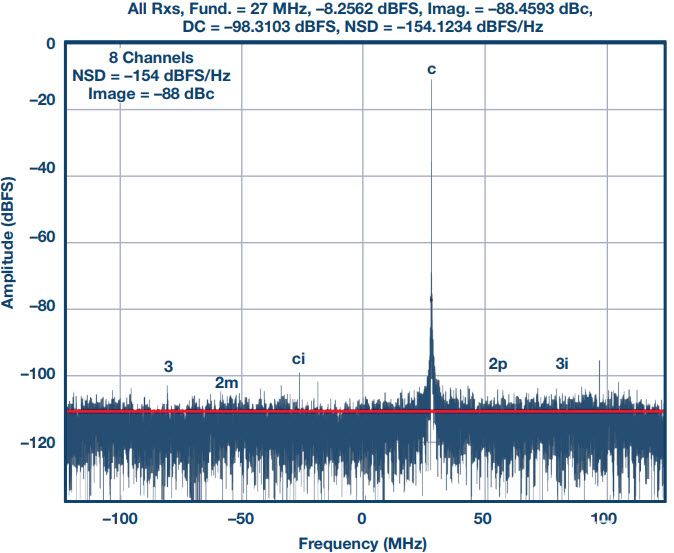

此外,在相位對齊和組合多個集成收發器通道后,相控陣系統的相位噪聲可以得到改善。圖5的前三條跡線顯示的測量結果表明,當使用四個集成收發器IC的內部LO組合八個發射通道時,相位噪聲性能有所改善。同樣,在有四個不同且不相關的聯絡處(即N瞧= 4),當從一個Tx通道變為八個Tx通道時,相位噪聲改善了~6 dB。增加通道數可以進一步改善相控陣雷達系統的相位噪聲。或者,可以向由 N 組成的每個子陣列注入一個外部 LOTRx集成收發器并改善子陣列級的起始相位噪聲,如圖5中的藍色跡線所示。但是,這是以該子陣列中的每個元素相關聯為代價的,因為它們都共享相同的LO源,因此它們無法在子陣列本身內提供通道求和改進。對于圖5所示的外部LO相位噪聲數據,外部LO源使用羅德與施瓦茨SMA100B信號發生器。

圖5.使用內部LO時,組合多個ADRV9009的Tx通道可改善系統級相位噪聲性能。外部LO注入為子陣列提供了改進的起始相位噪聲。

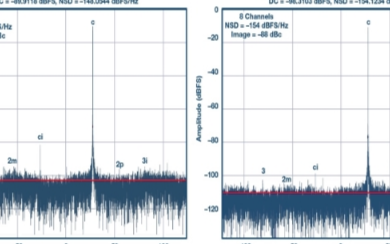

集成的DSP功能,如NCO、數字移相器和DUC/DDC,允許在數字域中進行基帶相位和頻率轉換,從而在基于集成收發器的多通道相控陣雷達系統中實現數字波束成形。由于將功能捆綁在單個IC上,系統現在能夠在許多相關的相控陣應用中使用集成收發器實現天線晶格間距。使用更多收發器增加通道數通常會導致波束更窄,但代價是增加系統占用空間。然而,由于現在在單個單片IC中具有多種功能,因此這種占位面積的增加現在比過去要小。使用 MATLAB 仿真輻射圖后,圖 6 顯示了從 N = 2?3到 N = 210通道導致波束變窄和理論瓣振幅變深。實際中的功率零點將由天線設計決定。

圖6.DSP 特性現在支持使用片上 NCO 和 DDC/DUC 進行數字相移。增加通道數和最佳相移會導致集成收發器形成的波束變窄。

結論

在單個IC中集成多個數字和模擬功能,可實現更小尺寸的相控陣雷達系統。這些系統可以同時實現數字波束成形和混合波束成形,具體取決于系統規格。已經證明了使用ADI公司的ADRV9009的系統級性能改進。這些集成器件支持各種新的系統,這些系統使用相同的硬件為多個應用提供服務。

審核編輯:郭婷

-

收發器

+關注

關注

10文章

3424瀏覽量

105960 -

微處理器

+關注

關注

11文章

2258瀏覽量

82403 -

混頻器

+關注

關注

10文章

679瀏覽量

45668

發布評論請先 登錄

相關推薦

集成式收發器支持實現小型相控陣雷達平臺

分析DCDC4644電源芯片在F-35戰機相控陣雷達的應用

RadioVerse生態系統中的寬帶收發器

數字波束形成相控陣中射頻電子的物理尺寸分配

如何使用集成式收發器實現更“Mini”的相控陣雷達平臺?

RadioVerse生態系統中的寬帶收發器分享!

集成式RF采樣收發器如何支持快速跳頻、多頻帶和多模式操作?

ADRV9009集成式收發器簡化數字波束成形

ADRV9009集成式收發器的性能及應用解決方案

天線到位功能可進行開發相控陣雷達

通過集成式收發器來實現小型相控陣雷達平臺

集成收發器支持小尺寸相控陣雷達平臺

集成收發器支持小尺寸相控陣雷達平臺

評論