本文將介紹系統(tǒng)低功耗模擬組件的設(shè)計技術(shù)

嘗試降低系統(tǒng)功耗時,一種方法是尋找要優(yōu)化或移除的設(shè)備。另一種方法是在組件級別進(jìn)行評估之前,將系統(tǒng)作為一個整體進(jìn)行評估并針對系統(tǒng)功能進(jìn)行優(yōu)化。

添加外部 ADC 以降低整體系統(tǒng)功耗

在低功耗數(shù)據(jù)采集系統(tǒng)中,將模數(shù)轉(zhuǎn)換器 (ADC) 集成到控制器中可減少整體組件數(shù)量、成本和理想的功耗。但這種做法實(shí)際上可能會增加整體功耗。

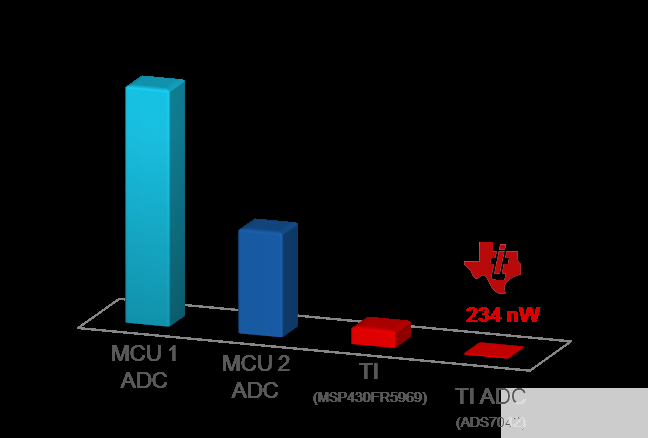

當(dāng)以 1kSPS 采樣時,幾個低功耗微控制器 (MCU) 中集成 ADC 的典型功耗通常大于分立 ADC 的功耗(圖 1)。因此,您實(shí)際上可以通過放置一個低功耗 ADC,如微控制器外部的 ADS7042,并關(guān)閉微控制器的集成 ADC。事實(shí)上,TI 的ADS7042超低功耗 12 位 ADC 在以 1kSPS 采樣時僅消耗 234nW 的功率。

圖 1:集成 ADC 與 ADS7042 在 1kSPS 時的功耗

使用分立式 ADC 而不是集成式 ADC 的另一個好處是,您可以將轉(zhuǎn)換器保持在傳感器信號附近,以最大限度地減少噪聲拾取。分立式 ADC 還可以幫助擴(kuò)展微控制器可以支持的模擬輸入通道的數(shù)量。

添加設(shè)備以節(jié)省功率的一個問題是分立設(shè)備所需的電路板面積。ADS7042 的 1.5mm x 1.5mm 8 引腳四方扁平無引線 (QFN) 封裝比標(biāo)準(zhǔn) 0805 表面貼裝組件更小,從而最大限度地減少了對整體系統(tǒng)設(shè)計尺寸的影響。此外,低引腳數(shù)有助于在布局過程中最大限度地減少布線。

檢查低功耗數(shù)據(jù)采集系統(tǒng)電路

無論您最終為低功耗數(shù)據(jù)采集系統(tǒng)選擇哪種類型的 ADC,重要的是要了解如何優(yōu)化 ADC 周圍的電路以降低整體功耗。數(shù)據(jù)采集??系統(tǒng)中的主要組件是傳感器輸入、將傳感器信號驅(qū)動到 ADC 的緩沖器、ADC 和 ADC 的電源。

ADS7042 BoosterPack展示了一個低功耗數(shù)據(jù)采集系統(tǒng)的示例,它是一款與TI LaunchPad? 開發(fā)套件生態(tài)系統(tǒng)兼容的開發(fā)板。ADS7042 BoosterPack 上的電路旨在轉(zhuǎn)換來自板載環(huán)境光傳感器或超小型 A 型 (SMA) 連接器的模擬數(shù)據(jù)(圖 2)。

圖 2:ADS7042 BoosterPack 上模擬輸入信號的電路圖

當(dāng)從連接到由 OPA316 緩沖的 SMA 連接器的模擬傳感器源轉(zhuǎn)換外部傳感器輸入時,驅(qū)動器在 3.3V 時消耗 400μA 的電流,從而導(dǎo)致 1.32mW 的功耗。這大約占系統(tǒng)總功率的 65%——其中包括 REFE3330 電壓基準(zhǔn)的功率 (12.87μW) 和 ADS7042 ADC 的功率 (690μW)。如果傳感器在沒有額外驅(qū)動器的情況下直接連接到 ADC,就像板載環(huán)境光傳感器一樣,傳感器電路僅消耗 99μW 的功率。這是 OPA316 在電路的第一個實(shí)現(xiàn)中消耗的功率的 7.5%,甚至沒有考慮驅(qū)動模擬輸入信號源所需的功率(表 1)。

表 1:ADS7042 BoosterPack 的電路功耗

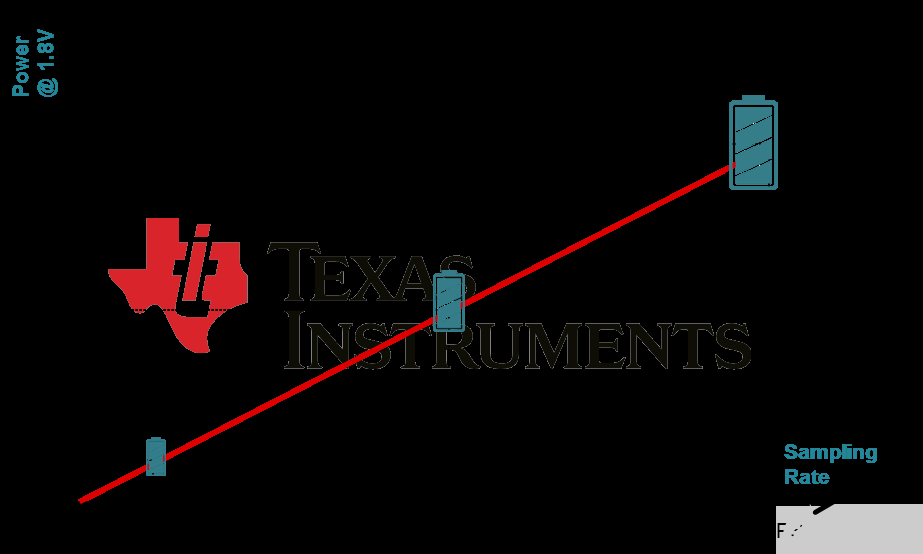

減少對驅(qū)動器的需求有助于降低整體功耗。但是,使用此解決方案有明顯的權(quán)衡取舍。您必須降低 ADC 的采樣率,以最大限度地延長輸入采樣電容器 (C SH ) 的建立時間。但這還具有降低采樣率和 ADC 功耗的優(yōu)勢,因?yàn)檗D(zhuǎn)換器的功耗與采樣率呈線性關(guān)系(圖 3)。

圖 3:ADS7042 的功耗與采樣率

在此示例中,使用外部分立式 ADC 有助于降低整體系統(tǒng)功耗。

審核編輯:湯梓紅

-

adc

+關(guān)注

關(guān)注

98文章

6497瀏覽量

544533 -

低功耗

+關(guān)注

關(guān)注

10文章

2399瀏覽量

103684 -

模擬組件

+關(guān)注

關(guān)注

0文章

3瀏覽量

5083

發(fā)布評論請先 登錄

相關(guān)推薦

低電壓、低功耗模擬電路設(shè)計方案

系統(tǒng)低功耗模擬組件的設(shè)計技術(shù)

系統(tǒng)低功耗模擬組件的設(shè)計技術(shù)

評論