在物聯網、大數據和云在行業媒體上風靡一時的時候,值得關注實現模擬世界數字化的技術進步。饋送云需要已經數字化的數據?模數轉換器(ADC)是跨越這些領域的設備,是定義大數據質量和準確性的關鍵。ADC設計方法的進步不斷突破界限,為我們周圍的世界提供精確的數字表示。速度和分辨率可以以一種燒毀歷史計量基準的方式推動。

高性能精密ADC在許多應用領域都很普遍。過程控制、可編程控制器、電機控制和電能分配是不同的例子。增加了不太日常的儀器領域,在這些領域中,所有類型技術的測試、研究、開發和鑒定都依賴于高精度數字轉換。目前,幾種ADC架構在精度方面存在競爭,根據其需求,選擇符合模數轉換原理,例如逐次逼近寄存器(SAR)與Σ-Δ,它們分別能夠在幾個MSPS下實現高達24位或更高的分辨率,在幾百kSPS下能夠達到32位。

當面對這些級別的分辨率和精度時,這些轉換器提供的有用動態很容易超過100 dBFS(滿量程)的神奇屏障,用戶在設計用于數字化信號的模擬調理電路以及相關的抗混疊濾波器時面臨著真正的挑戰。在過去的二十年中,采樣率和濾波技術發生了顯著變化,現在可以結合使用模擬和數字濾波器,在性能和復雜性之間實現更好的折衷。

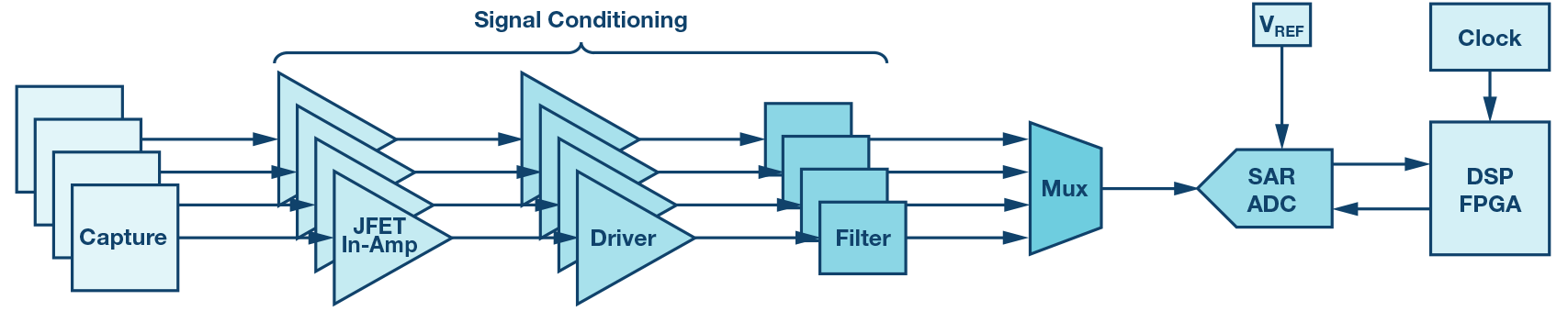

圖1.典型測量信號鏈。

圖1顯示了數據采集系統這種分區的典型示例。在對差分或非差分信號(放大、縮放、電平的適應和轉換等)進行調理后,后者在數字化之前被濾波以滿足奈奎斯特準則。根據ADC的過采樣速率,使用額外的數字濾波來符合采集系統的規格。

由于對非常寬輸入動態的需求增加,上述許多應用都采用最先進的高分辨率ADC。隨著動態性的提高,人們可以期待系統性能的提高,以及模擬調節鏈的壓縮,擁堵和能源消耗的減少,甚至材料成本的降低。

過采樣及其優點

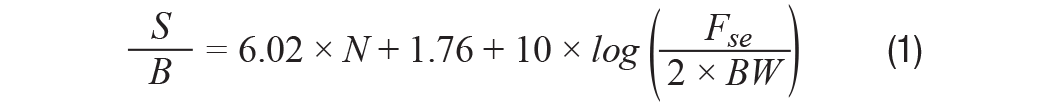

在出現非常快速、高分辨率的模數轉換器之前,動態問題通過使用快速可編程增益放大器、更快的比較器和/或多個ADC的并聯來解決,再加上適當的數字處理,以實現強信號的數字化并區分噪聲電平附近的小幅度。在這些過時且現已過時的架構中,這轉化為難以開發的復雜電路,并且在線性度、帶寬和采樣頻率方面受到限制。目前的替代方案是通過利用現代更經濟的ADC提供的高采樣速率來應用過采樣技術。以高于奈奎斯特定理規定的最小值的FSE速率對信號進行采樣的操作可以通過處理和增加編碼器的信噪比來執行增益操作,從而增加有效位的數量。事實上,量化噪聲和熱噪聲被同化為白噪聲,在整個奈奎斯特波段及以后均勻傳播。過采樣后,通過濾波并嚴格以所需的最小采樣速率(2 × BW)工作來限制有用頻段,每降低一個倍頻程,噪聲能量就會降低3 dB,如圖2所示。換言之,理想情況下,過采樣因子4可使信噪比理論上增加6 dB;也就是說,一個額外的位,如公式1所示:

總之,過采樣有兩個優點:即信噪比的提高,以及放寬對ADC之前的抗混疊模擬濾波器的要求。

圖2.通過添加數字抽取濾波器來比較頻譜噪聲密度。

抗混疊濾波器:分區困境

理想情況下,與ADC相關的濾波器,特別是那些負責頻譜混疊問題的濾波器,必須具有幅度響應,其可能帶寬與其精度相比最平坦,并且具有足以適應其動態的帶外衰減。過渡帶通常應盡可能陡峭。因此,這些抗混疊低通濾波器必須具有能夠消除寄生鏡像、噪聲和其他雜散音的特性。根據應用的不同,還應特別注意相位響應,并應補償任何過大的相移。許多建議被認為是基本的,但當它們必須與指定的24位或32位轉換器的要求相結合時,這些轉換器的積分非線性誤差僅為幾個LSB和其他類似的靜態和動態參數,則很難實現。

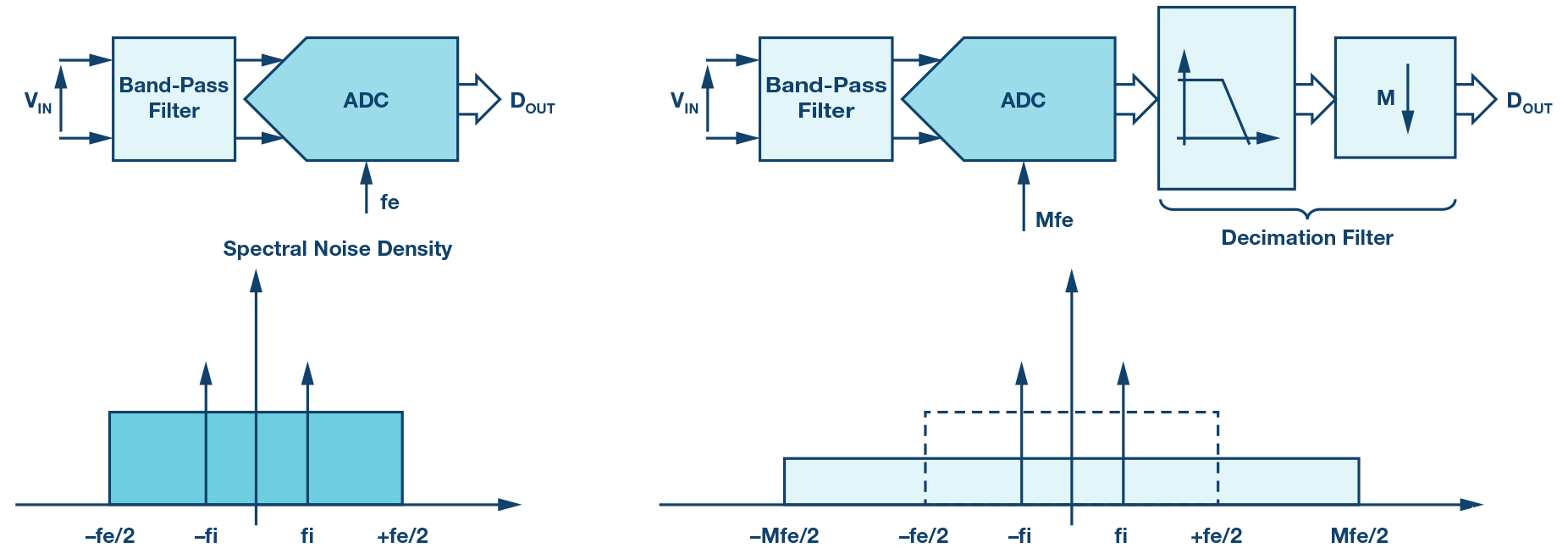

如前所述,對過采樣的興趣在這里變得非常重要,因為它不僅對信噪比有益,而且對模擬抗混疊濾波器規格及其截止頻率的放寬也有好處。如圖3c所示,過采樣將轉換帶擴展至–3 dB截止頻率和阻帶起點之間。模擬抗混疊濾波器的階數與過采樣率成反比。表1中的數據說明了給定抑制目標的過采樣率與模擬抗混疊濾波器階數之間的關系。

圖3.過采樣、數字濾波和抽取降低了所需的模擬反化濾波器階數。

目前的技術提供了高精度的SAR ADC轉換速率,近年來大幅提高,目前18位分辨率從超過1 MSPS到15 MSPS。相比之下,寬帶Σ-Δ型ADC以較低的吞吐速率提供更高的分辨率,具有非常高的過采樣比。在數百kHz的等效(18位分辨率)輸入帶寬下查看Σ-Δ轉換器是可能的,但內置了數字濾波的附加功能。

具有同等分辨率的Σ-Δ型ADC的帶寬可達數百kHz,并具有內置數字濾波器的額外優勢。這些ADC的基本特征是其整體計量精度,這與靜態(直流)和動態(交流)參數有關,因此這些系統中的轉換器和隨附的模擬調理電路必須具有頂級規格。

相反,除過采樣SAR(如LTC2512和LTC2500-32)外,大多數SAR ADC不包括數字濾波器,因此其工作不會受到一些不可避免的數字低通濾波的阻礙或限制,這會導致計算精度、帶通紋波、衰減帶抑制、傳播時間和功耗之間的折衷。同時,AD7768-1等一些新型寬帶Σ-Δ型ADC更加靈活,允許用戶對其數字濾波器系數進行一定程度的可編程性。

LTC2378-20:市場上首款 20 位 SAR ADC

在性能競賽中,2014年,凌力爾特(現為ADI公司的一部分)提供了首款具有20位分辨率和線性度的SAR ADC。LTC?2378-20 是一款出色的轉換器,在接近 MSPS 的所有其他競爭產品中,它仍然獨樹一幟。

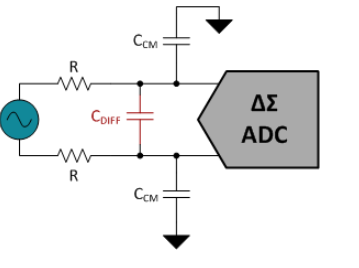

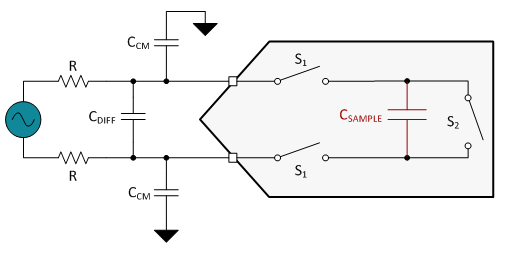

ADI公司的首款20位SAR ADCAD4020采用了略有不同的路徑。AD4020兼具低噪聲和低功耗特性,力求使信號鏈更易于客戶使用。1.8 MSPS的低噪聲和低能量是傳統的矢量。但是,有一些關鍵的附加功能有助于硬件設計人員更輕松地實現必要的性能。模擬前端采樣安靜的能力就是一個例子。轉換器轉換回采集時,輸入端的充電/放電一直是一個難題。典型的連鎖反應是需要更高速的驅動器放大器。AD4020現在可以采用相當于目標實際信號帶寬的高阻態模式低功耗精密放大器,從而提高測量精度。將轉換時間限制在350 ns可以延長采集時間,這也使得選擇放大器更容易,并且在數字端,在串行接口上讀取數據時允許使用較慢的串行數據時鐘。在隔離應用中,較慢的串行時鐘可降低隔離器的EMI效應和電流消耗。采用AD7980系列和AD40xx系列其他16至18位成員共用的10引腳MSOP或10引腳QFN外殼,意味著硬件設計人員可以輕松升級平臺設計選擇。該器件采用1.8 V供電,在1.8 MSPS時功耗僅為15 mW。這種低元件功耗與降低信號鏈中支撐模塊電流消耗的特性相結合,意味著能夠以盡可能低的散熱實現卓越的性能。

LTC2378-20 和 AD4020 的采樣速率分別為 1 MSPS 和 1.8 MSPS,為過采樣提供了極大的可能性,尤其是在音頻頻段或更遠頻段方面。為此,必須在外部FPGA或DSP中實現定制的抽取濾波器。如前所述,如有必要,可以繞過后者以將延遲降至最低。使用這些初級采樣速率值,并考慮0 kHz至25 kHz頻段,各自的過采樣因子約為16或32,處理增益為12 dB至18 dB,同時抗混疊低通濾波器在嚴格按照奈奎斯特定理進行常規操作方面進行了簡化。

ADC 至 DSP 鏈路:一切都是串行的

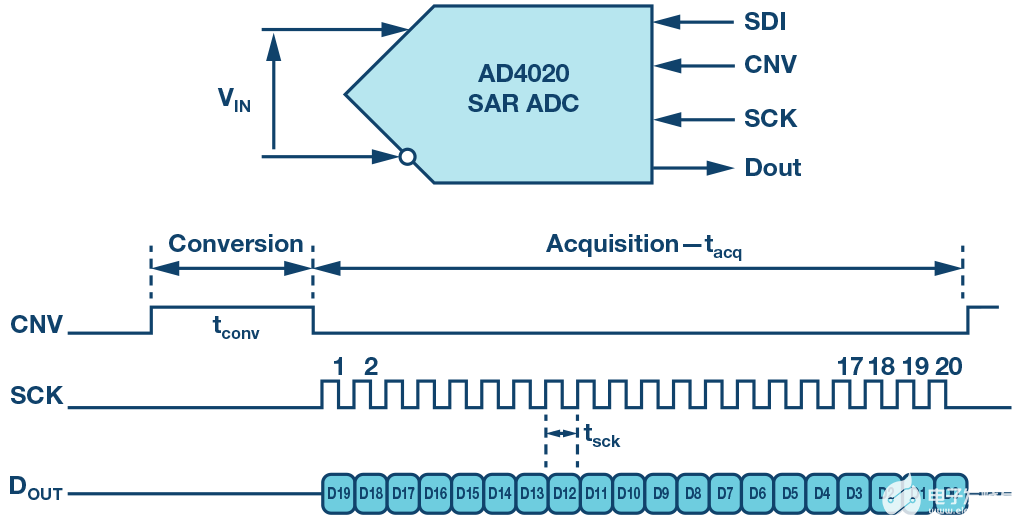

近年來,半導體行業及其設計師小圈子明顯傾向于減小元件尺寸,導致外殼引腳真正放氣,并以串行形式調節幾乎所有數字輸入或輸出,這些輸入或輸出需要與SPI總線、同步串行端口等接口。這里所討論的轉換器沒有留下用于提取樣本和控制ADC各種功能選項的串行接口。這些串行接口符合與SPI或DSP串行端口兼容的條件,但實際上并非如此。充其量,它們隱藏了設置時鐘信號節奏的移位寄存器,以便從設備中提取數據或在配置期間注入數據。與所有這些SAR ADC一樣,LTC2378-20和AD4020對串行時鐘(SCK)提出了頻率要求,以標稱采樣速率恢復20位數據。由于數據讀取的階段嚴格限制在采集時間的持續時間(大約300 ns)內,因此在轉換期間,外部訪問上的數字活動必須減少到完全靜音,并且時鐘頻率必須超過60 MHz才能在分配的時間內從采樣中恢復所有位,同時遵守1 MSPS的采樣速率。這是對負責從ADC收集數據的控制器接口的嚴格限制,既用于生成此類時鐘頻率,也涉及接收器端要實現的時間規格。LTC2378-20要求的最小SCK信號頻率為64 MHz,這意味著它不能僅與任何通用微控制器或大多數具有同步串行端口(SPORT)的DSP接口,這些同步串行端口(SPORT)超過僅50 MHz的最大頻率,但Blackfin系列的某些成員除外,例如ADSP-BF533或ADSP-BF561,它們可以達到90 Mbps。因此,人們擔心使用與低抖動時鐘生成電路相關的大型CPLD或FPGA至關重要。串行輸出SAR ADC的大多數數字接口或多或少具有相同的時序和邏輯信號模式,如圖4所示。至于SDI配置輸入,除了級聯模式外,它還以低得多的頻率尋求。ADC采樣周期的等效完整周期時間為?

從而定義最大采樣頻率,包括:

其本身受輸出數據的讀取速率的限制

圖4.AD4020的時序圖

幸運的是,AD4020的轉換時間非常短,為325 ns,采樣速率為1 MSPS,采集時間為675 ns,因此串行數據讀取頻率低于33 MHz;與DSP同步串行端口(如SHARC ADSP-21479)的頻率相匹配的頻率;能耗極低。?

LTC2512 和 LTC2500-32 過采樣 SAR 允許用戶在多個轉換期間讀出濾波輸出寄存器的內容,從而降低了串行數據讀取頻率要求。寬帶Σ-Δ型ADC在ADC轉換期間不需要接口靜默時間,從而進一步放寬了串行接口時鐘時序。

超低功耗多通道采集系統

出于能耗、精度和工作模式選擇靈活性的原因,以及出于商業原因,在這些領域不能考慮基于 FPGA 的解決方案。僅保留DSP浮點處理器來處理這些20位ADC的串行輸出并實現優化的抽取濾波器。

如今,有許多數據采集系統能夠在大量通道上同時采樣。這意味著許多ADC并行運行,同時由同一控制器控制,該控制器還具有收集數據并將其存儲在存儲器中以供后續分析的任務。

圍繞SAR ADC構建的系統與SHARC ADSP-21479的功能相關,或者其快速ADSP-21469或ADSP-21489版本之一,時鐘頻率為450 MHz,不僅可以想象,而且在性能、開發時間、能耗和緊湊性方面是最相關的。這些處理器具有支持 8 個模數數字化通道所需的所有功能和外設,從同步串行接口到生成不同的時鐘信號和觸發轉換。在所有SHARC處理器中,ADSP-21479是唯一采用低漏電、65 nm CMOS工藝制造的32位/40位浮點DSP,其優點是大大降低了泄漏或靜態電流,結溫的演變幾乎呈指數級增長。動態電流是處理器及其外設的頻率和活動的函數,也低于標準或快速CMOS制造工藝的動態電流。另一方面,與傳統版本相比,最大CPU頻率降低了約30%至40%,但在很大程度上足以滿足此類應用程序的需求。

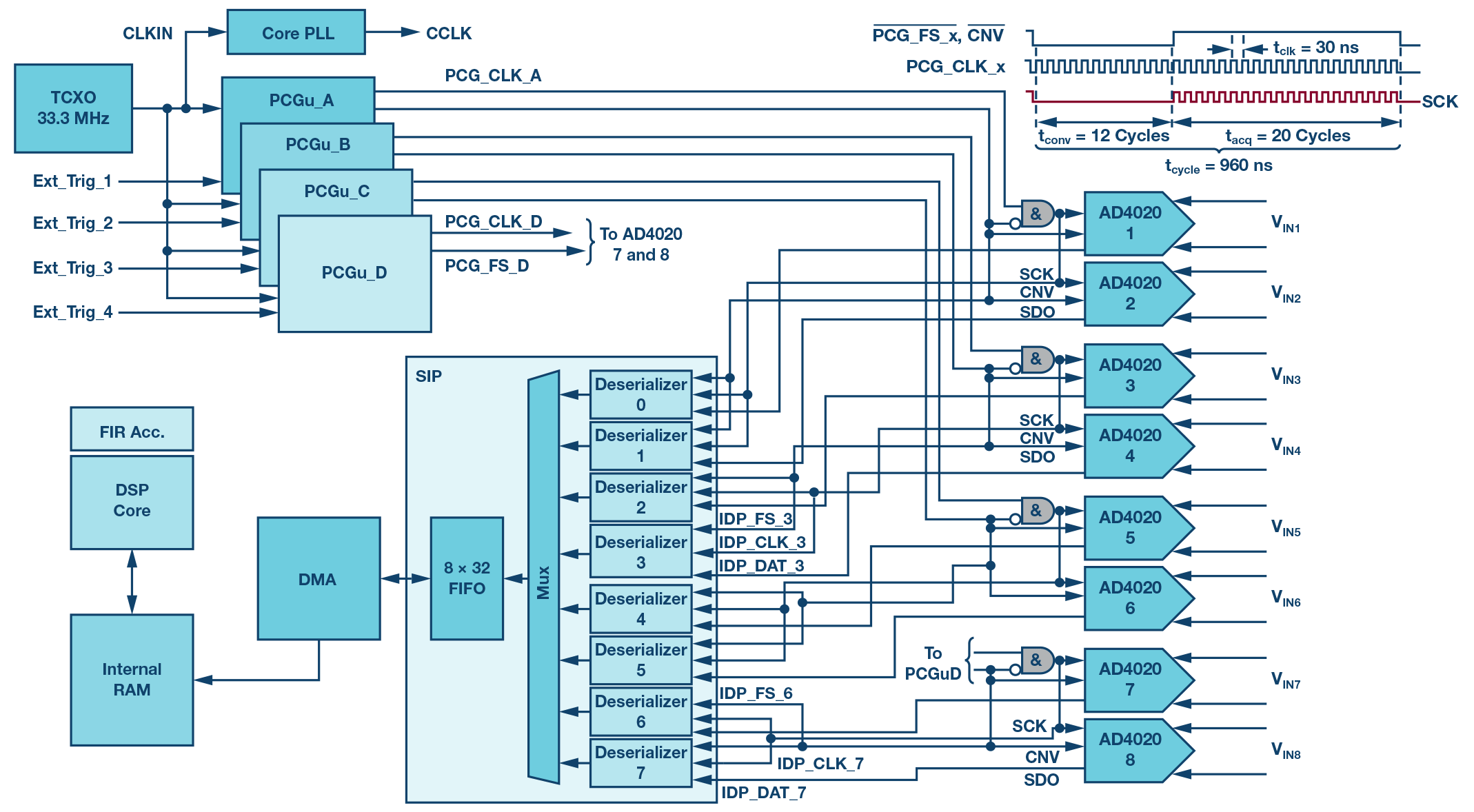

ADSP-21479具有許多外設,包括一個稱為串行輸入端口(SIP)的特殊模塊,該模塊能夠同時接收來自8個外部串行端口發送器的流,與時鐘和同步信號同步工作。事實上,可以將8個類似于AD4020的ADC直接連接到此接口,從而連接到處理器。如圖5所示,8個通道有自己的IDP_SCK時鐘,IDP_FS同步,IDP_DAT輸入信號,其數據一旦解串,就會自動多路復用到32位、8字FIFO存儲器中,然后通過64位DMA數據包或CPU執行的讀取傳輸到SHARC內部RAM。在 DMA 傳輸操作中,SIP 由在自動乒乓模式下運行的雙索引 DMA 通道提供服務。此外,ADSP-21479還具有四個精密時鐘發生器(低抖動)或PCG,能夠從內部或外部源(TCXO)生成獨立的時鐘和同步信號對。這些激勵的頻率、周期、脈沖寬度和相位通過編程20位內分頻器獲得。每個PCGx發生單元提供一對由AD4020轉換器共享的CLK/FS信號,但在轉換階段時鐘必須保持靜音,這說明存在一個邏輯門,該邏輯門將IDP_FS和IDP_SCK信號組合在一起以創建SCK時鐘。圖5中的時間圖顯示,一旦轉換時間tconv過去,必須盡快讀取當前樣本的20位,即以33.3 MHz的速率讀取,以保持采樣頻率中的1 MSPS神奇屏障。大約600 ns后,數據被傳輸到其中一個SIP緩沖器,可以使用IDP_FS或CNV信號啟動新的轉換周期,以觸發AD4020的新轉換。后者的最大轉換時間為325 ns,對應于CNV信號的脈沖寬度,即12 IDP_SCK時鐘周期或360 ns。總之,如圖5的時序圖所示,一個完整的掃描周期需要32個IDP_SCK信號周期,即總共960 ns,最大采樣速率為1.040 MSPS。

圖 5.使用反序列化和 DMA 傳輸到 DSP 內部 RAM,將 8 個 20 位 1 MSPS SAR ADC 連接到 SHARC DSP。

同樣,ADC LTC2378-20也可以與ADSP-21489相關聯,因為它能夠在高達50 MHz的更高外設時鐘頻率的時鐘下工作,在這種情況下,采樣速率為900 kSPS,如表1所示。不幸的是,靜態電源電流(I丁特),或后者的泄漏遠高于動態電流,這使得這種配置的總功耗超過可用瓦數,高得令人無法接受。

抽取濾波

假設這些轉換器在過采樣模式下使用,則有必要提供針對目標頻段量身定制的抽取濾波器,滿足上述性能要求,從而最大限度地減少對DSP在所需計算能力和能耗方面的影響。目前,改變采樣率的過程已成為標準的數字信號處理操作,這些操作使用插值器和數字抽取器執行。出于相位響應線性的原因,低通抽取濾波器使用有限脈沖響應(FIR)拓撲,并且可以根據所尋求的效率程度使用不同的拓撲:

用于抽取的直接或優化的FIR濾波器

級聯多速率FIR濾波器(半波段)

多相遠紅外濾波器

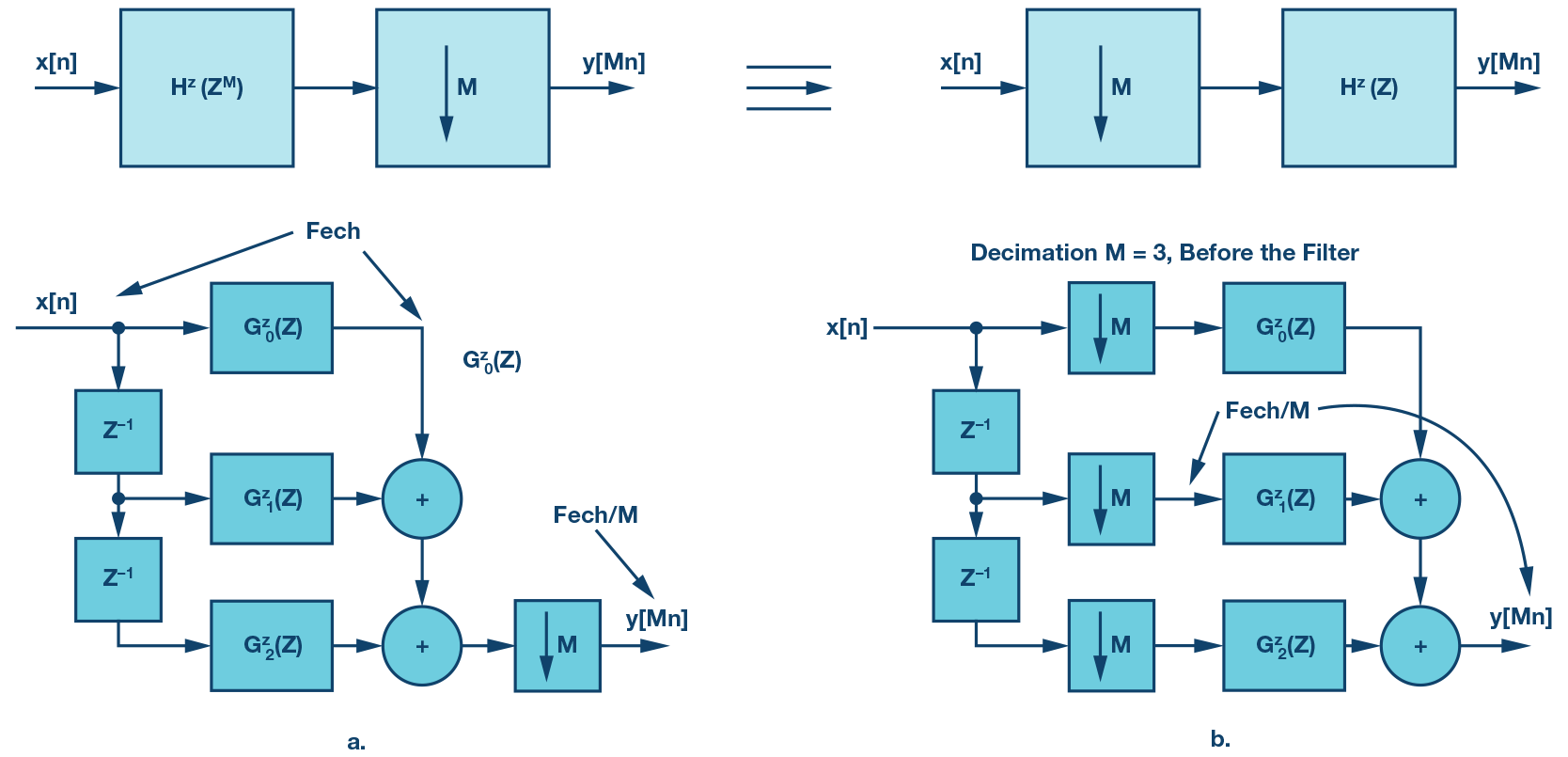

無論是FIR還是IIR類型的多相濾波器,都是抽取或插值濾波器最有效的實現之一。然而,數字處理的正統觀念要求在抽取之前進行濾波。根據這一假設,1/M抽取濾波器由一個低通濾波器和一個采樣頻率降低級組成(圖6a)。事先對信號進行濾波以避免頻譜混疊,然后以M – 1的速率周期性地消除樣本。然而,直接實現這些傳統FIR或其他結構的抽取濾波器是浪費資源,因為因為拒絕的樣本是由幾十甚至數百個乘法累積(MAC)產生的。使用分解為幾組濾波器或針對抽取優化的濾波器的多相濾波器,可以基于某些特性(如圖6b所示)生產高效濾波器。

圖6.傳統的抽取濾波器和抽取濾波器采用多相方法。

SHARC ADSP-21479采用專用于FIR濾波的SIMD架構和硬件加速器,以及針對數字信號處理優化的指令集,特別適合實現這些類型的濾波器。每個SHARC處理元件都有一個32/40位乘法器累加器,能夠以266 MHz的CPU頻率每秒提供533個定點或浮點MAC。但是,對于某些具有明顯延遲(房間均衡或聲音效果)的應用,需要提高計算能力才能將內核從密集和持續的乘法運算中解放出來,例如 FIR、IIR 或 FFT 濾波,這些任務由專用硬件加速器執行。因此,用戶將完全自由地利用CPU來計算更復雜的算法,這些算法需要完全復雜的指令集。專用于FIR濾波的加速器具有自己的本地存儲器,用于存儲數據和系數,并具有以下特征:

它支持 IEEE-754 定點或浮點 32 位算術格式

它有四個并行運行的乘法累加單元

它可以在單速率或多速率處理模式(抽取或插值)下運行

它可以在簡單的迭代中處理多達 32 個 FIR 濾波器,總共 1024 個系數

ADSP-21479的加速器以系統時鐘或PCLK外設的速率計時,是CPUCCLK時鐘頻率的一半;即 133 MHz。這導致總計算能力為每秒 533 個 MAC。加速器不要求執行指令;其操作由特定寄存器的配置決定,并且完全依賴于DMA傳輸在內部和/或外部存儲器之間移動數據。

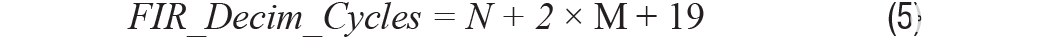

顯然,該加速器將以優化的方式執行多速率濾波器(插值或抽取)的實現。由于簡單的抽取濾波器僅為M輸入信號提供一個輸出結果,因此輸出速率比輸入速率低1/M倍。由于需要內存指針的數量,多相濾波器組的實施起來很復雜,無需訴諸復雜的多相濾波器組,這種優化的FIR濾波器組的實現只是利用了M-1個樣本的輸出來避免進行這些計算,并且只計算產生有用樣本的數據。這消除了浪費,因此,操作數量以 M – 1 的比率(即本例中的 15 次)減少,從而大大節省了 CPU 周期。然而,對于這樣的抽取比和較短的計算窗口,加速器不如具有兩個計算單元的內核有效,并且會受到從一個濾波器到另一個濾波器的通道期間其DMA通道被重新編程的不利影響。在SISD模式下由單個計算單元實現時,這種濾波器在CCLK周期數方面的成本表示為:

N 是濾波器的系數數,M 是抽取比。

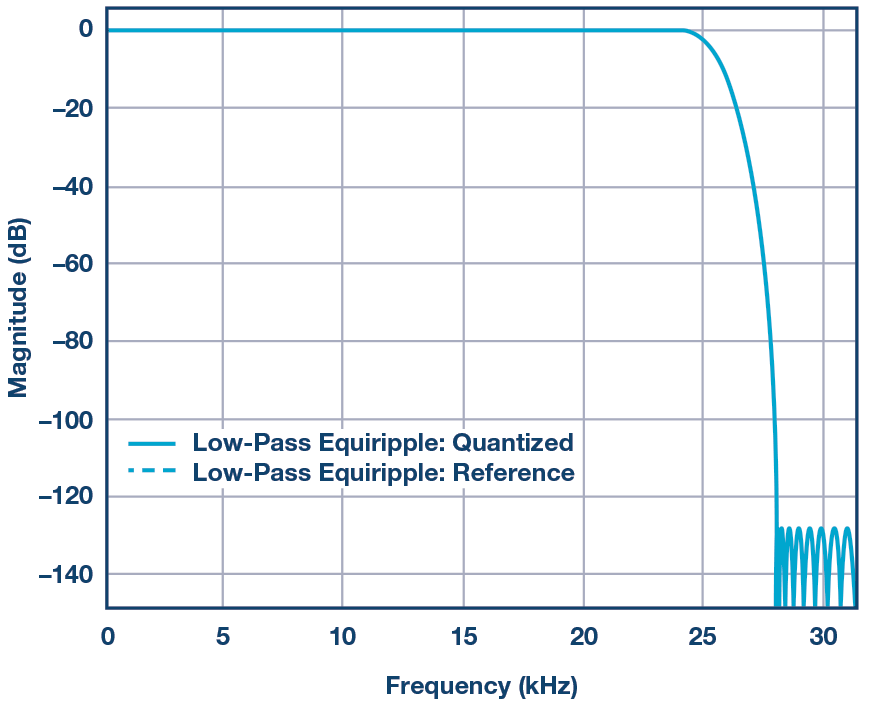

對于FIR濾波器(源到匯編器21k),對于FIR濾波器(源到匯編器21k)的實現相當于大約150個周期,對應于頻帶(0 kHz至24 kHz)中±0.00001 dB的紋波規格,對于62,500 SPS的采樣率,帶外衰減為–130 dB。該濾波器具有 97 個系數(以 32 位 FP IEEE-754 格式量化),其響應如圖 7 所示,使用 MATLAB? 濾波器設計器。對于連接的SIP或ADC的每個活動通道,在DMA中斷發生時,以此采樣頻率的速率重復此操作。

圖7.抽取濾波器的濾波器響應。

對于實時和DSP負載,濾波操作以62.5 kSPS的頻率重復,代表9,375,053個CCLK周期,而8個ADC轉換通道的濾波操作略多于8倍,因為每個濾波器的存儲器指針值都保存和恢復,存儲在SHARC數據地址生成器中。這意味著每秒 8000 萬個執行周期,或在 SISD 模式下 SHARC DSP 的執行周期為 80 MIPS,在 SIMD 模式下為一半,兩個處理元素并行運行。根據上述模式,這八個抽取器FIR濾波器的執行占用了時鐘頻率為266 MHz的ADSP-21479,速率分別為30%和15%。

最后,能源消耗

雖然轉換器的能耗可以根據其規格輕松準確地進行評估,但處理器的能耗更加困難,因為輸入該消耗方程的參數數量以及根據實時約束和操作模式的巨大可變性。無需詳細介紹,讀者可以在與估算ADSP-214xx和ADSP-21479處理器各種組件的能耗相關的技術筆記中輕松找到,其中考慮了功能模塊的活動、靜態電流的結溫、電源電壓值、使用的輸入輸出引腳數量, 各種外部頻率和容性負載。根據圖5的功能描述,給出了DSP和ADC的幾種組合,對應于此類抽取濾波應用的DSP活動的能量消耗。這些具有四個或八個ADC的相關DSP變體是根據功能容量、足夠輸入/輸出的數量、處理器的計算能力以及ADC的整體性能建立的。由于靜態電流非常低,圍繞ADSP-21479及其8個SAR ADC集群構建的解決方案能耗最低,同時在濾波算法和其他數字功能選擇方面提供了完全的自由度,整體性能充其量是出色的。

這個多通道數據采集系統(DAQ)示例還表明,使用FPGA并不是處理數字信號處理任務所必需的,浮點DSP更適合高精度SAR ADC,特別是當功耗是一個熱點問題時。

| 參數 | AD4020和ADSP-21479 | LTC2378 和 ADSP-21489 | AD4020和ADSP-BF532 | LTC2378 和 ADSP-BF532 | LTC2512 -24 | LTC2500 -32 | AD7768 -1 中等模式 | AD7768 -1 快速模式 |

| 轉換 A/N | 特區 | 特區 | 特區 | 特區 | 特區 | 特區 | WB-Σ-δ | WB-Σ-δ |

| 分辨率 | 20 | 20 | 20 | 20 | 24 | 32 | 24 | 24 |

| 過采樣 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 |

| 帶內紋波 (dB) | ±0.00001 | ±0.00001 | ±0.00001 | ±0.00001 | ±0.001 | ±0.001 | ±0.003可編程 | ±0.003可編程 |

| 阻帶 (dB) | <–130 | <–130 | <–120 | <–120 | <–65 | <–65 | –110 可編程 | –110 可編程 |

| 抽取濾波器 | 選擇遠紅外 | 選擇遠紅外 | 選擇遠紅外 | 選擇遠紅外 | 冷杉 | 冷杉 | 冷杉 | 冷杉 |

| 采樣頻率 | 1 | 0.91 | 1.8 | 1 | 1.0 | 1 | 4 | 8 |

| 有效過采樣率 | 16 | 16 | 32 | 16 | 16 | 16 | 128 | 256 |

| 第一個混疊區域 (MHz) | 1 | 1 | 2 | 1 | 1 | 1 | 8 | 16 |

| 抽取后頻率 (kSPS) | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 | 62.5 |

| 實現 –110 dB 混疊抑制所需的 AAF 階數 | 5 | 5 | 4 | 5 | 5 | 5 | 3 | 3 |

| 濾波器階數高于 (dB) 時的混疊抑制 | –123.4 | –123.4 | –123.4 | –123.4 | –123.4 | 62.5 | –130 | –147.5 |

| 3 kHz 時的信噪比,采用 5 V 基準電壓源 (dBFS) | 112 | 116 | 115 | 116 | 114 | 116 | 113.7 | 116.9 |

| 2 kHz 時的 SFDR (dBc) | 122 | 128 | 122 | 128 | 120 | 128 | 128 | 128 |

| 20 kHz 時的 THD (dBfs) | 122 | 128 | 122 | 128 | 120 | 128 | –120 | –120 |

| 數字濾波器旁路 | 是的 | 是的 | 是的 | 是的 | 是的 | 是的 | 不 | 不 |

| 頻率 SCK/SDO (MHz) | 33.3 | 50 | 61.5 | 64.1 | 1.5 | 1.5 | 1.5 | 1.5 |

| 模數轉換器功耗(毫瓦) | 10.8 | 24.8 | 15 | 24.8 | 32 | 30 | 19.7 | 36.8 |

| 數字輸出脈沖功耗(毫瓦) | 185 | 832 | 70 | 75 | ||||

| 通道數 | 8 | 8 | 4 | 4 | 1 | 1 | 1 | 1 |

|

總能耗(通常在 Tj = 55°C 時)( mW) |

272 | 1030 | 130 | 175 | ||||

| 每通道能耗 (mW) | 34 | 129 | 33 | 43 | 32 | 30 | 19.7 | 36.8 |

| 模數轉換器工作溫度范圍(°C) | –40 至 +125 | –40 至 +85 | –40 至 +125 | –40 至 +85 | –40 至 +85 | –40 至 +85 | –40 至 +125 | –40 至 +125 |

-

轉換器

+關注

關注

27文章

8694瀏覽量

147085 -

控制器

+關注

關注

112文章

16332瀏覽量

177808 -

SAR

+關注

關注

3文章

416瀏覽量

45949

發布評論請先 登錄

相關推薦

抗混疊濾波器設計的3條指導原則

ADI 全新中文資料(2018 年 10 月)

AD9276BSVZ模數轉換器

SAR模數轉換器AD7989-1和AD7989-5

多角度講解高精度SAR ADC的抗混疊濾波考慮因素

高精度SAR模數轉換器的抗混疊濾波考慮因素

多角度講解高精度 SAR ADC的抗混疊濾波考慮因素

高精度SAR模數轉換器的抗混疊濾波考慮因素

高精度SAR模數轉換器的抗混疊濾波考慮因素

評論