高壓 (HV) 電源模擬集成電路 (IC) 幾乎用于每個電子系統,包括電池電源轉換、音頻、汽車、工業、醫療和 LED 驅動器。與使用數字低壓IC設計相比,確保此類IC的設計符合閂鎖資格要求涉及一種概念上不同的方法。此應用提供有關模擬 IC 設計閂鎖合規性的指導。本應用筆記的類似版本最初于2018年4月18日出現在EDN上。

介紹

與設計數字低壓(LV)IC的方法相比,確保高壓(HV)功率模擬IC符合閂鎖資格要求的設計考慮因素大不相同。LV IC的靜電放電(ESD)和閂鎖設計挑戰通常在I/O庫單元級別解決,無需定制即可在各種產品中重復使用。

高壓IC通常結合了與p基板隔離的多個電壓域。從成本角度來看,液絡部隔離工藝技術占主導地位。它們支持所謂的隔離 N 型槽,以封閉器件和電路塊。在擴展CMOS(ECMOS)工藝中,口袋由一組深Nwell(DNW)植入物形成。由于深度植入的限制,這種方法可實現40V范圍內的口袋電壓額定值。使用雙極性 CMOS DMOS (BCD) 工藝技術可以實現高達 120V 的電壓范圍,其中 N 型口袋由埋入層、可選沉降片和相對較厚的生長 N 外延層組合形成。該技術集成了功率優化的互補橫向DMOS器件,具有漏極擴展以及用于源和體區域的非自對準或雙擴散方案1.腔隔離的最小工藝布局設計規則不足以進行閂鎖注射測試。相反,需要針對復雜布局的應用程序特定閂鎖設計規則。

總體而言,閂鎖設計規則、標準和檢查器描述很少結合實際設計解釋其方法步驟背后的原因。這種理解往往有助于組織有效的實踐經驗。在本應用筆記中,我們從閂鎖式角度探討了對高壓模擬IC設計這一多樣化、新穎和復雜主題的理解差距。我們按邏輯順序連接半導體結構層面的解釋,然后引入用于閂鎖收集特征和預防間隔規則的注入器受害者形式主義。然后,我們將一組定義應用于閂鎖間距規則參數和模塊級驗證原則的實驗方法,以實現IC閂鎖協同設計的實用概念。本應用筆記沒有從歷史或多樣性的角度對高壓閂鎖主題進行廣泛的回顧,而是提出了一種通過實踐成功驗證的方法。

閂鎖是由集成有源器件區域形成的寄生結構的副作用。在某些區域的附近,注入的載流子可以在襯底中漫射和漂移長距離,并且在一定的電流水平下,由于沖擊電離、熱載流子產生和寄生雙極性增益之間的正反饋,啟動非線性電導率調制。因此,暫時的電氣狀態偏差會導致非專用的強電流路徑。它可能導致不可逆轉的損壞或導電狀態的形成,只要原始電源狀態保持不變(即閂鎖),這種狀態就無法自耗散。閂鎖狀態通常通過比較激勵前后的電源電流來檢測。

閂鎖狀態可以通過連接到I/O引腳的正向偏置結注入電流或測試脈沖期間電源引腳的過壓來誘導。在實際環境中,這種影響可能是由電涌、電磁干擾 (EMI) 事件、與感性負載的間歇性連接、熱插拔和電離輻射引起的。閂鎖魯棒性本質上是一種IC質量度量,它代表了承受一定程度的短期電氣狀態偏差并恢復到原始功能狀態而不會發生不可逆轉變化的能力。分別按標準進行資格測試2仿真兩個事件:I/O引腳中的電流注入和電源引腳的過壓。典型標準是所有電源電流的變化小于10%,并通過全功能測試程序。

因此,閂鎖測試基本上檢查特定IC設計的穩定性,以應對與環境接口的引腳工作條件的相對短期偏差。ESD條件類似用途測試的類比是上電模式系統級ESD測試[3,4].由于傳統電路仿真模型缺乏覆蓋率,如果沒有專用方法,很難預測閂鎖測試的通過水平。

了解高壓閂鎖

高壓 IC 閂鎖適用于過壓和注入閂鎖測試模式。最大工作電壓 (MOV) 和絕對最大額定電壓 (AMR) 是與高電壓電平相關的兩個主要額定值。在 MOV 范圍內運行可確保長期可靠性,而將電壓提高到 AMR 以上可能會導致立即發生不可逆轉的故障。分別,對于MOV和AMR之間的范圍,預期具有生存能力,即在這種狀態下,完成閂鎖測試。不確定性與正式數據手冊IC引腳AMR電壓(可設置為MOV低至10%)、連接到引腳的集成器件的實際物理AMR與具有特定布局設計的IC引腳的實際物理AMR之間的相關性有關。

從低壓數字IC傳播,電源引腳的標準過壓測試定義為1.5 x MOV的水平2.如果未達到電流限制,則相同的電平會限制注入電流測試的電壓順從性。雖然在LV CMOS電路中可以輕松滿足此電壓電平,但具有功率優化LDMOS的高壓電路并不總是可以承受它。解決此問題的一種方法是最大應力電壓(MSV)方法,它限制了測試電壓2.注入測試會在高壓引腳之間感應檢測電流,這可能導致高焦耳熱。

然而,高壓閂鎖的主要實例與寄生結構本身有關。解釋這一點的最簡單方法是與更熟悉的 LV 閂鎖進行比較。低壓閂鎖通常涉及通過I/O單元內部或內核電路中形成的寄生可控硅整流器(SCR)的電流路徑。

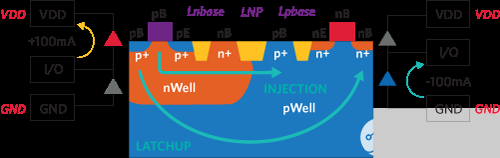

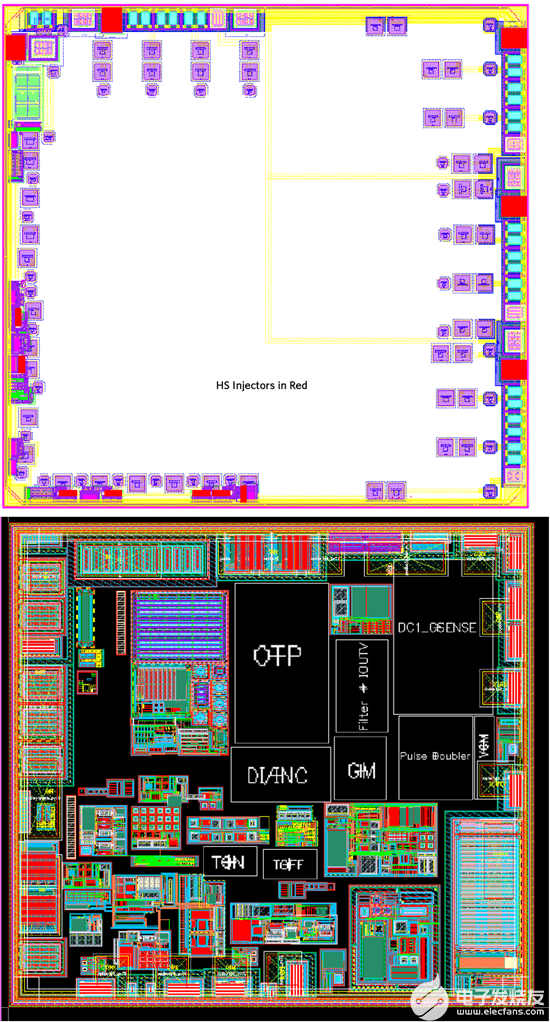

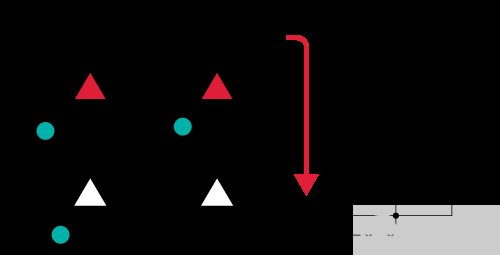

例如,在圖1所示的推挽式I/O緩沖器中,當輸出被上拉到電源電平以上時,來自PMOS體二極管的高端(HS)空穴注入受到激勵。在負注入電流測試中,輸出被拉到地電平以下,低側(LS)電子注入通過NMOS體二極管實現。高電流路徑在器件源表示的p+發射極和n+發射極之間形成。根據物理效應,防閂鎖規則要求在NMOS和PMOS器件的放置上,通過主體拉環完全隔離,以減少n-p-n和p-n-p結構的增益。由于載體直接注入SCR結構基座內,因此間距規則必須控制保護環的長度L新堿基和 L普巴斯.增益降低導致SCR保持電壓增加至高于電源電平,從而消除了形成閂鎖狀態的物理可能性。

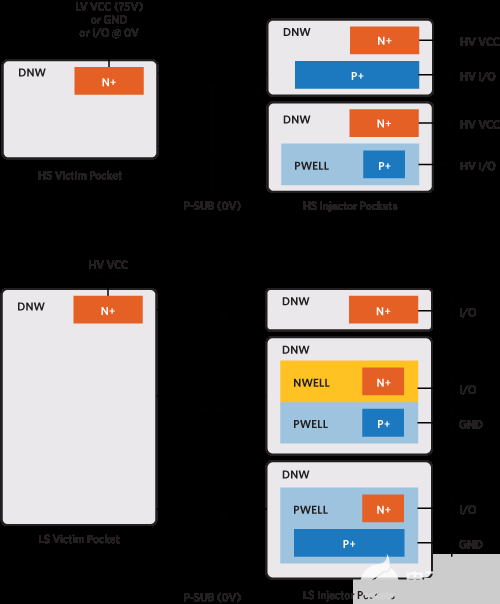

圖1.等效結構橫截面,用于解釋 I/O 閂鎖場景,并附有 HS 和 LS 注入閂鎖測試的電路圖,CMOS 器件由體二極管表示。

然而,只要將NMOS和PMOS器件放置在單獨的N型口袋中,這種IC I/O緩沖器閂鎖方案和預防規則就與高壓技術無關。這種方法是一種通常的設計實踐,可確保LV I/O閂鎖的通過水平,同時滿足口袋隔離的最低設計規則。

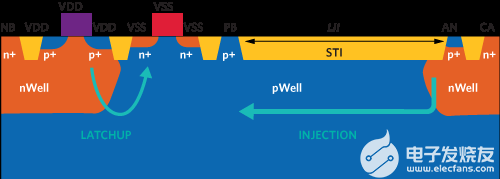

在低壓磁芯閂鎖的情況下,注入結位于I/O單元區域,而受害者由核心電路表示。在高電位差下,從I/O注入的ESD二極管載流子可能會漂向核心電路(如圖2左側的NMOS-PMOS逆變器所示),并引起寄生內核SCR導通。核心電路的較高靈敏度是使用最大體源間距規則的結果。分別,預防規則旨在將核心電路與 I/O 注入源分開(長度 L第二).

圖2.解釋核心閂鎖方案的等效結構橫截面。

與I/O電路一致,高壓工藝技術中的磁芯閂鎖問題通過將磁芯電路與基板隔離在一個單獨的N型口袋中來解決,該N型腔的外圍有一個適當的N溝道停止(NCS)環。因此,主要的低壓閂鎖實踐對于帶來不同閂鎖的高壓電路幾乎沒有用處。高壓閂鎖主要是由不同的寄生結構引起的,例如在注射條件下,當口袋對口袋的高壓n-p-n打開時。

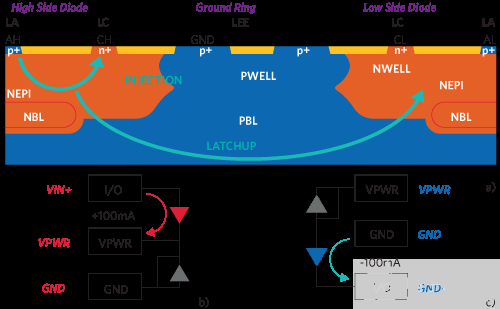

例如,考慮一對連接到I/O引腳的高壓ESD二極管,如圖3所示,N-epi口袋的電位與n-p-n結構不同,其中高側口袋用作集電極,低側口袋用作發射極,p基板環用作基極。在閂鎖測試中實現的注射條件需要更寬的隔離間距和額外的收集環。

圖3.高壓閂鎖分析的結構以及HS空穴和LS電子注入的電路圖。

在下一個細節層次中,高施加電壓下的橫向口袋到基板結在BCD和ECMOS技術中的作用不同。隨著BCD過程中口袋電壓的增加,空間電荷區域在輕度摻雜的N-epi區域內膨脹,為注入口袋內的載流子產生相應的提取電場。在ECMOS過程中,耗盡區主要沿輕摻雜P襯底區的方向傳播。ECMOS工藝中沒有PBL會降低P-sub環收集HS注入孔的效率。

在低壓電路閂鎖中,寄生SCR結構可以保持導通狀態,因為與1.8V至3.3V的電源電平相比,保持電壓約為1.5V。寄生n-p-n器件由于相對較高的約4V至7V的本機保持電壓而不存在漏洞。在高壓閂鎖的情況下,最小隔離間隔下的口袋到口袋n-p-n保持電壓范圍約為10V至20V。因此,對于高壓閂鎖隔離,附加規則必須針對寄生n-p-n結構電導率調制效應的臨界狀態的轉變,通過降低結構增益和注入水平以及增加收集。在這些條件下,電熱特性n-p-n主要決定了閂鎖魯棒性。

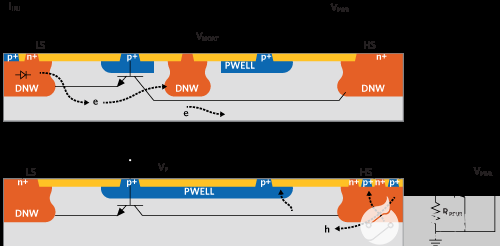

在最常見的情況下,LS注入閂鎖是由拉到基板電位下方的口袋啟動的。不太常見的情況是,當注入來自LS口袋內的正向偏置連接時,如圖4所示。基底(n-p-n基)區域中注入的電子向HS口袋漂移并改變電場分布,從而增加雪崩倍增。為了減少必要的袋到口袋分離,除了p基板環外,還使用了兩種有效的收集功能。在LS注入時,N護城河環可以連接到低壓電源,以將至少部分注入的電子從HS口袋重新路由。

類似地,通過在HS注入液絡部的口袋內引入p假收集器來部分收集口袋內的孔來抑制HS孔注入條件,如圖4所示。

圖4.橫截面用于解釋高壓閂鎖場景,包括額外收集帶有偏置 N 護城河環的低側電子注入(上圖)和帶有假 p 收集器的高側孔(下圖)。

總體而言,口袋到口袋間距規則是施加電壓、注入電流水平和測試溫度以及器件設計和尺寸的函數。與低壓閂鎖不同,高壓閂鎖通常是不可逆的,并導致IC燒毀,除非對檢測電流進行準確分析。口袋n-p-n結構的燒毀是電或電熱電流不穩定的結果,然后是負差分電阻,電流燈絲形成和局部燒毀。

高壓閂鎖規則:噴油器-受害者形式主義

顯然,在IC閂鎖測試期間,并非每個口袋都被迫注射。也不是每個N口袋都補充當前充當“受害者”的路徑。因此,協同設計方法的第一步是檢測對閂鎖事件至關重要的口袋。這需要與未來的自動檢查識別和驗證程序完美兼容的定義和規則。

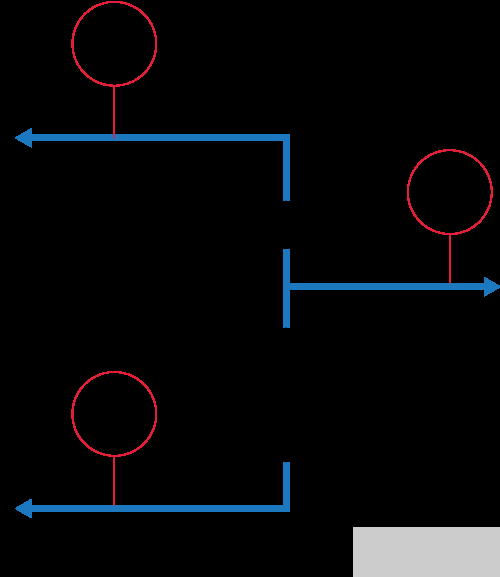

盡管有幾種替代方法,但最實用的一種是所謂的注射者-受害者形式主義。將電路數據手冊引腳規格與閂鎖測試標準相結合,閂鎖規則矩陣只能在四種口袋內設置:HS 注入器、LS 注入器、HS 受害者和 LS 受害者(圖 5)。

如果 HS 注入器包含可在正向電流傳導中強制的 p-n 結,則可以將其定義為 HS 電位處的口袋(圖 5a)。任何附近的LS潛在口袋都代表一個互補的HS受害者口袋。在注入條件下,一部分孔可以從HS注入袋逸出并漂向HS受害者口袋,導致電流密度,電壓,溫度和口袋間距的某些關鍵組合閂鎖。例如,與10V偏置相比,80V偏置供電器和受害者之間的相對距離需要15倍的距離。

同樣,LS噴油器被定義為一個口袋,該口袋要么包含內部結,要么在閂鎖測試條件下可以正向偏置。LS受害者的角色可以使用與HS電源電連接的口袋來完成。

圖5.高邊孔注入器和受害者(上圖)。低邊電子注入器和受害者(下圖)。

受害者和注入器基本上形成高壓寄生n-p-n的集電極或發射極區域。當可視化口袋到口袋間距的燒毀時,物理類比仍然非常明顯,如圖6所示。

圖6.負模式電流注入閂鎖失敗。

最佳功率IC設計不可避免地需要根據額外的間距要求計算HS和LS饋電器和受害者的位置。它涉及將它們組合在一起并使用通用收集環。如果僅僅基于直觀的方法,這些程序幾乎不會有效。

規則獲取:晶圓級鎖存測試

當采用注射器-受害者形式時,閂鎖驗證必須克服其他幾個挑戰。必須識別芯片布局中的注入器和受害者口袋,以應用所需的收集功能和間距。必須檢查收集環的低電阻電氣連接。例如,如果將收集 N 護城河環連接到內部電源,而閂鎖注入的電流不足,則效果會降低。因此,檢查器的規則涉及拓撲和原理圖級處理。由于電壓域多樣、高壓閂鎖的不可逆性、模擬電路模塊的變化以及口袋之間的空間利用率不同,實驗間距規則采集挑戰需要一些簡化。

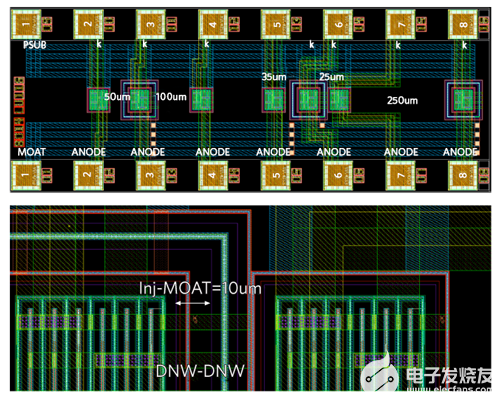

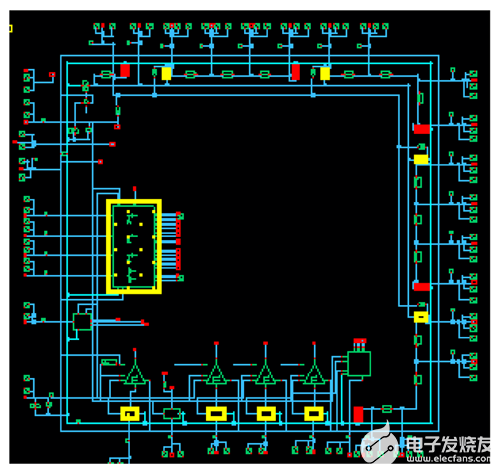

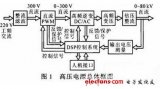

主要的簡化是,間距規則測量數據的實驗測試結構是針對ESD二極管的,ESD二極管最常作為I/O焊盤的注入器和受害者。考慮到閂鎖是由注入電流密度觸發的,與大尺寸LDMOS陣列相比,小尺寸ESD二極管代表了最壞的情況。測試結構必須覆蓋注入器-受害ESD二極管對,以及各種口袋到口袋間距以及收集環的放置場景,如圖7所示。熱耦合混合模式仿真方法和大型物理閂鎖結構的參數化有限元模型也有助于填補實驗數據空白,如圖1至圖4所示。

圖7.ECMOS工藝中低側閂鎖測試結構的模塊和單元級布局視圖。

這些測試限制了實驗數據收集。由于高功率應力通常會損壞整個芯片,因此在晶圓級收集數據提供了一種有效的方法。圖8顯示了在標準范圍內對工業測試儀進行IC一致性測試的典型注入脈沖2.典型的注入脈沖使用雙 SMU 再現,以與標準探針臺結合同時生成電壓或電流同步脈沖。

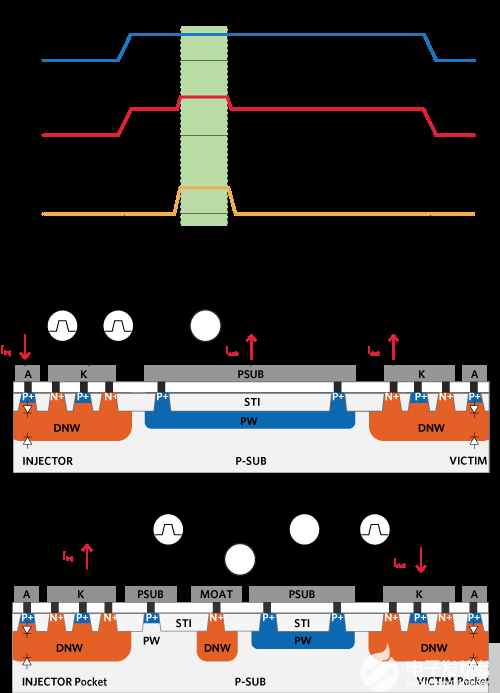

在HS閂鎖測試設置(圖8b)中,當結在DNW內部以高電位正向偏置時,會產生HS注入條件。在HS注入過程中,可以使用與陰極短路的可選P+環來增強陰極的空穴收集。LS注入晶圓閂鎖測試是在注入器口袋的DNW到基板結被驅動到基板電位以下時進行的,將電子電流注入基板并打開由附近的HV偏置DNW口袋(受害者)形成的寄生結構。偏置于某些電源電位的N護城河環可用于收集一些電子電流并降低閂鎖敏感性(圖8c)。

圖8.晶圓級設置中的HS注入閂鎖測試波形,用于口袋到口袋電壓VPK-PK,噴油器電壓 VINJ和當前 IINJHS孔注入器(b)和LS電子注入(c)的閂鎖測試結構和測試裝置組件的橫截面。

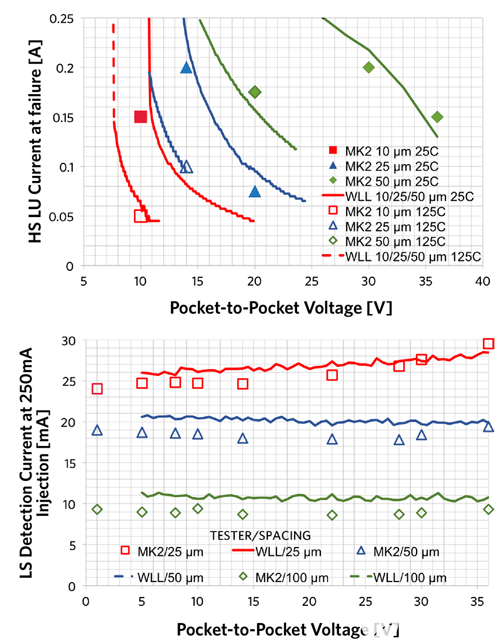

該實驗方法可測量閂鎖臨界注入電流與施加的注入器受害者口袋到口袋電壓的閂鎖依賴關系的臨界條件,如圖9所示。該數據與工業測試儀(Cadence Virtuoso參數化單元參考)獲得的打包液位結果相關,并與各種工藝選項相當。??

圖9.晶圓級和MK2關鍵HS和LS在25°C和125°C時在注入器-受害者間距上閂鎖電流。

模塊級高壓閂鎖自動驗證和協同設計

最終協同設計方法的一個基本要素是在模塊上而不是在頂層單元級別進行自動驗證。基于時間表和資源限制,驗證完成的IC布局幾乎不能容忍任何重大變化。在原理圖設計層面甚至引腳規格規劃中正確規劃和排列芯片布局塊非常重要。

要啟用模塊級驗證,必須在工藝設計套件 (PDK) 中添加幾個必要的功能。其中一項功能引入了焊盤網絡,用于在網表中傳播有關焊盤類型和電壓電平的信息。它使用工具[7]支持拓撲和電氣驗證組件,其中代碼為提取的設備分配了注入器或受害者角色。例如,檢查連接到引腳的NMOS是否連接到特定焊盤類型,如從焊盤網絡轉換而來的。如果排水管連接到 IO 焊盤類型并且主體連接到 GND 焊盤網絡類型,則將其分配給 LS 注入器的角色。該二極管成為負電流注入時的注入結,通過將I/O引腳拉低到地電位以下來實現。

這種先進的方法可以在不完整的頂部單元布局階段進行驗證,因為它不需要完整的層次結構和外部焊盤。由于閂鎖規則間距相對較大,在頂層重新設計復雜的高壓功率IC驗證可能會有所不同,因此成為一項不切實際的任務。另一方面,通過迭代實時驗證不完整的模塊進行適當的規劃有助于實現最節省空間的組件放置。

自動布局布線的趨勢涉及在早期步驟中使用結合布局和原理圖屬性的墊網單元進行主動閂鎖協同設計。焊盤類型表示將來連接到網絡的外部焊盤類型:IO信號引腳,電源引腳(V抄送),以及接地參考 (GND) 或特殊功能,例如內部生成的電源。引腳的工作電壓在焊盤網絡中定義,并與袖珍MOV的PDK范圍相匹配。

圖 10.墊網單元放置示意圖示例。

當焊盤網絡參數化單元在原理圖和布局視圖中被識別為器件時,驗證工具可以提取和分析注入器或受害對象。噴油器和受害對象可以在原理圖和布局中突出顯示,以便共同設計決策,如圖11所示。焊盤網絡信息按照驗證工具中的連接語句的規定在整個布局視圖中傳播。這些陳述定義了金屬、聚乙烯和硅的連接方式。布局中的每個網絡也有一個關聯的墊網。來自墊網電池的電壓與受害者或注入器相關聯。可以立即運行此類驗證,以識別需要根據閂鎖指南在布局中考慮放置的設備。

圖 11.原理圖中標記的高邊噴油器(黃色)和受害者(紅色)。

即使原理圖級別不存在拓撲布局輸入信息,在原理圖中突出顯示這些器件已經可以作為協同設計輔助程序,在布局中對這些器件的布局放置進行適當的未來投影。可以通過相應的交互式結果可視化(例如,在注入器件和外部焊盤之間插入串聯電阻)對原理圖本身進行更改,以減少閂鎖漏洞。將設備從噴油器的角色中移除消除了大間距要求。

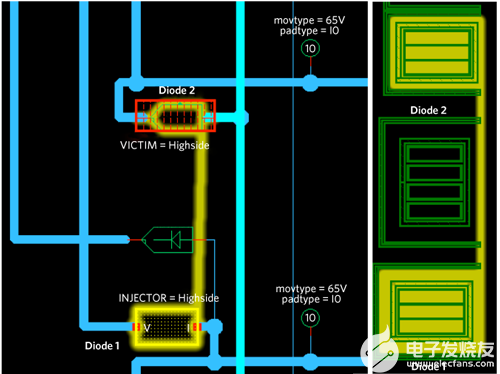

如果節奏大師布局套件XL5,可以在原理圖中啟用約束,以幫助在布局中放置器件。例如,在原理圖中,兩個耐高壓二極管被標識為HS注入器-受害者對(圖12)。可以在原理圖中添加二極管1和二極管2之間的物理約束,并在它們之間設置最小距離。約束將轉換為布局,并且自動放置不允許二極管 1 更接近二極管 2 的物理約束值。例如,當原理圖閂鎖工具識別注入器或受害設備時,可以在該設備上設置一個屬性,以在饋電器周圍放置正確的保護環作為設備單元的一部分。

圖 12.突出顯示添加到原理圖的實例約束(左)和在受約束的設備布局中可視化的距離約束(右)。

當模塊級布局完成且與原理圖正確匹配時,隨后使用布局數據庫中的實例化墊網評估所有閂鎖檢查,包括間距規則。原理圖所有者和布局工程師可以使用在兩個數據庫視圖之間開發的常見閂鎖術語來解決任何錯誤。可以輕松顯示已識別的噴油器、受害者和蚊帳。噴油器和受害者的位置可以在物理數據庫中的塊級別突出顯示,如圖 13 所示。

圖 13.顯示HS注入二極管(紅色)和最終頂層電池的塊布局。

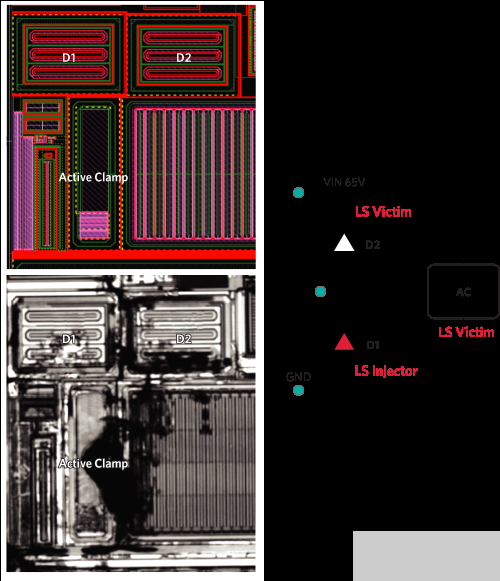

圖14顯示了另一個協同設計案例示例,該示例具有簡化的高壓電路,具有兩個I/O引腳和一個帶有內核有源箝位和浮動ESDP電源軌的浮動ESDP軌。由于ESDP未連接到電源,因此自動消除了I/O二極管D1和D2的HS注入場景。由于ESD箝位驅動器的RC時間常數比閂鎖測試域屬于更短的時域,因此該電路可以通過高壓注入器(上二極管)和受害者的閂鎖。但是,如果I/O引腳具有快速瞬態規格,這種節省空間的方法可能會導致瞬態閂鎖風險。在這種情況下,通過有源箝位的浪涌電流導致二極管注入,并遵循間隔規則以避免閂鎖,而ESDP軌必須使用V更新抄送墊網。

圖 14.浮動電源主動鉗位注入的協同設計示例。

總結

對于高壓功率模擬IC,閂鎖協同設計方法已從傳統的LV CMOS I/O和內核閂鎖基礎顯著演變而來。經濟高效的高壓功率IC設計需要基于迭代塊級驗證的先進方法,高壓閂鎖規則涉及新原理,將間距規則和有效收集環的拓撲和電氣驗證相結合。考慮到 ESD 和閂鎖功能消耗的高壓模擬功率芯片上通常占面積的 20% 至 25%,新的閂鎖協同設計方法是一種必要的設計范式轉變,可在質量和成本效益方面提供最佳 IC 產品。

從引腳規格和模塊級原理圖草圖開始,可以使用布局策略進行最佳布局規劃,該布局策略結合了迭代模塊級驗證,以分析準實時布局選項和權衡,包括電路重新設計選項。與傳統的閂鎖相比,該方法為共同設計具有系統級、上電模式ESD和高注入電流水平和不同時域下的浪涌的引腳規格的IC帶來了新的機會。該方法的進一步發展可以集中在考慮大型分布式噴油器對象的縱橫比的規則上(例如,功率陣列和工藝技術優化)。

審核編輯:郭婷

-

電源

+關注

關注

185文章

17992瀏覽量

252954 -

集成電路

+關注

關注

5403文章

11715瀏覽量

364729 -

ESD

+關注

關注

49文章

2179瀏覽量

173923

發布評論請先 登錄

相關推薦

高壓電源的典型應用

淺析高壓電源的開發流程

對高壓電源的輸出電流的要求

LHCD高壓電源診斷

基于DSP的高壓電源設計

如何選擇高壓電源的產品

高壓電源的安全與使用

符合高壓電源模擬IC的閂鎖認證要求

符合高壓電源模擬IC的閂鎖認證要求

評論