一、RS觸發器

首先,我們需要了解一下最基本的觸發器RS觸發器。

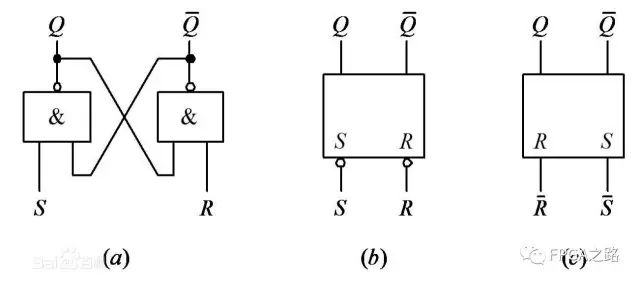

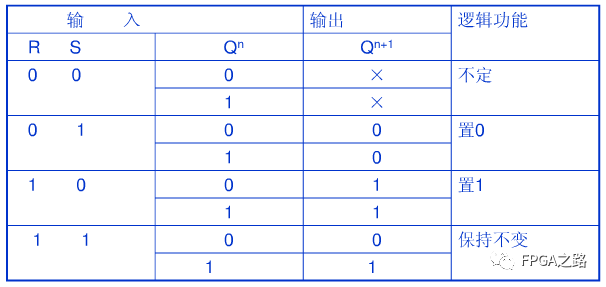

其中S和R是兩個輸入端,Q和Q反是兩個輸出端,中間是兩個與非門,結構很簡單。其真值表如下:

當R=S=0時,輸出狀態不定(避免出現此狀態)

當R=0,S=1時,輸出狀態置0

當R=1,S=0時,輸出狀態置1

當R=S=1時,保持不變

R和S不能同時為0!!!!!

R和S不能同時為0!!!!!

R和S不能同時為0!!!!!

二、同步RS觸發器

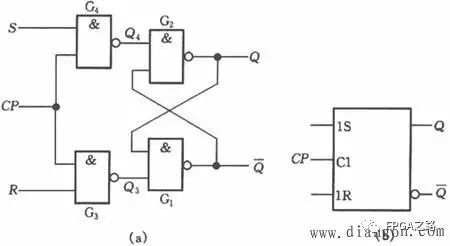

在數字電路中,為協調各部分動作一致,常要求某些觸發器于同一時刻工作,所以要引入同步信號。電路結構如下:

可以看出,相比于RS觸發器,只是在前面加上了兩個與非門和一個同步信號。當CP=0時,G3和G4被鎖住,意思就是只能輸出高電平,這就意味著Q保持不變。

當CP=1時,G3和G4打開,構成基本的RS觸發器,原理如RS觸發器。

R和S不能同時為1!!!!!

R和S不能同時為1!!!!!

R和S不能同時為1!!!!!

三、主從觸發器

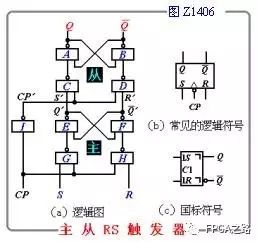

在觸發器工作時候,如果輸入端R或者S在CP=1時多次變化,那么輸出狀態可能就發生改變,不能保持狀態唯一。所以我們需要一種新的結構讓結果只能在一個高電平期間發生一次改變,于是就有了主從觸發器(好巧妙的結構啊!!!).結構如下:

從左圖中可以看出,下面的為主觸發器,有一個同步信號CP。上面的為從觸發器,同步信號為CP的反相。當CP=1時,主觸發器工作,從觸發器被鎖住,從觸發器的狀態保持不變。主觸發器就可以拆分為一個RS觸發器來分析,這里就不再贅述了(啊呸!真懶)

當CP=0時,主觸發器被鎖住,它的輸出狀態保持不變,從觸發器開始工作。這里當主觸發器的輸入再怎么變化也影響不到后面從觸發器的輸出狀態。(哇!好厲害啊)這時從觸發器的工作狀態又是一個簡單的RS觸發器,我也就不分析了。真值表如下:

R和S不能同時為1!!!!!

R和S不能同時為1!!!!!

R和S不能同時為1!!!!!

四、

JK觸發器

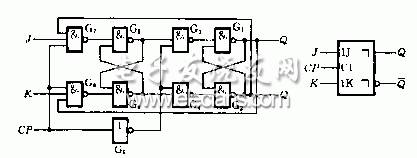

上面三種觸發器都有一種狀態不能存在,導致電路不小心處于這種狀態時候會出現不可預測的后果,為了避免這種情況發生,大佬們又發明出了一個新的結構。JK觸發器(大佬就是屌沒電還能跑!!!)。結構圖如下:

看著有點復雜····

我們先把它和主從觸發器比較下,發現就是多了兩個從輸出端Q接到輸入端的負反饋連線,其實也沒那么復雜啦。

現在分析下它的工作狀態。

若J=K=0.結果保持不變啊。

若J=1,K=0。恩······就是一個主從觸發器呀~~結果置1。不明白的往回看。

若J=0,K=1。恩······還就是一個主從觸發器呀~~結果置0。不明白的往回看。

敲黑板,重點來了!!!

若J=K=1時,需要考慮兩種情況:

1.當前輸出Q=0.這時左下的與非門被鎖死,只能輸出高電平1。當CP=1時,左上角與非門輸出低電平0,此時變成了主從觸發器的S=1,R=0,結果置1

2.當前輸出Q=1.這時左上的與非門被鎖死,只能輸出高電平1。當CP=1時,左下角與非門輸出低電平0,此時變成了主從觸發器的S=0,R=1,結果置0

綜上,當J=K=1時,觸發器的結果將發生反轉。

編輯:黃飛

-

RS觸發器

+關注

關注

3文章

101瀏覽量

18186 -

觸發器

+關注

關注

14文章

2027瀏覽量

61639

原文標題:觸發器基本知識

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論