介紹:

max via stack就是design rule對(duì)可以上下堆疊的via(多層via的cut有overlap)的數(shù)量有限制,不能超過(guò)要求,否則就會(huì)報(bào)MaxViaStack的DRC。

簡(jiǎn)單舉個(gè)例子:比如Tech LEF/tf文件要求是4,那么v1-v2-v3-v4-v5在同一位置overlap就會(huì)報(bào)DRC。

下面以tech LEF為例詳細(xì)講解一下。

LEF里面的約束:

PROPERTYDEFINITIONS

LIBRARY LEF58_MAXVIASTACK STRING

"MAXVIASTACK maxStack [NOSINGLE] [RANGE bottomLayer topLayer] ;" ;

END PROPERTYDEFINITIONS

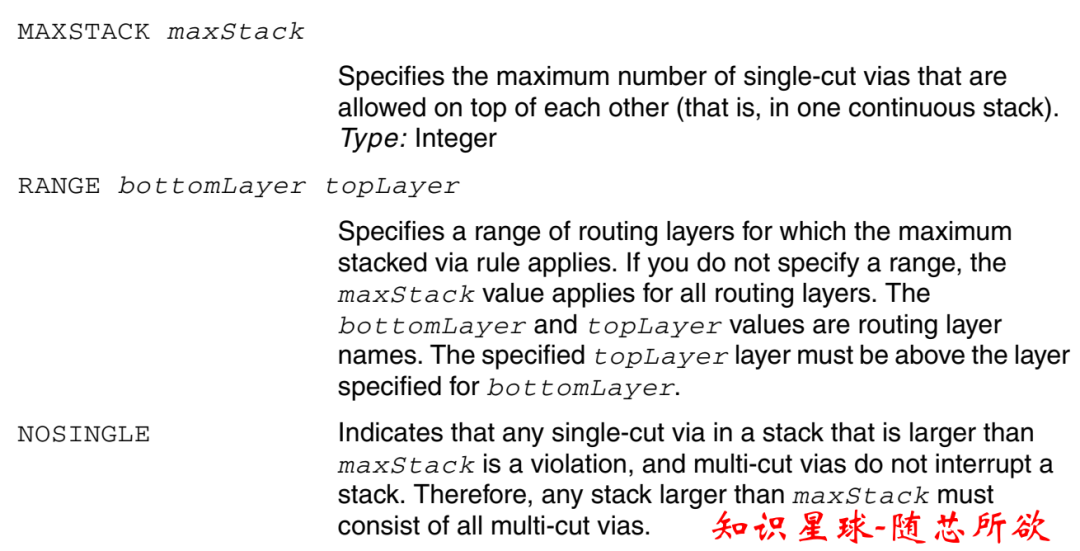

詳細(xì)解釋?zhuān)?/strong>

MAXSTACK指定的是single cut via允許連續(xù)堆疊的最大數(shù)目,如果超過(guò)它就是DRC違反(不考慮multi cut via);

RANGE指定的是檢查的最低和最高層,如果不做約束的話默認(rèn)檢查的所有繞線層;

NOSINGLE(可選項(xiàng)),前面的MAXSTACK指定的是single cut via允許連續(xù)堆疊的最大數(shù)目,是不考慮multi cut的,因此遇到multi cut via的話會(huì)認(rèn)為中間是斷開(kāi)的,而如果指定NOSINGLE的話則認(rèn)為multi cut via沒(méi)有打斷堆疊,還會(huì)算在內(nèi)。

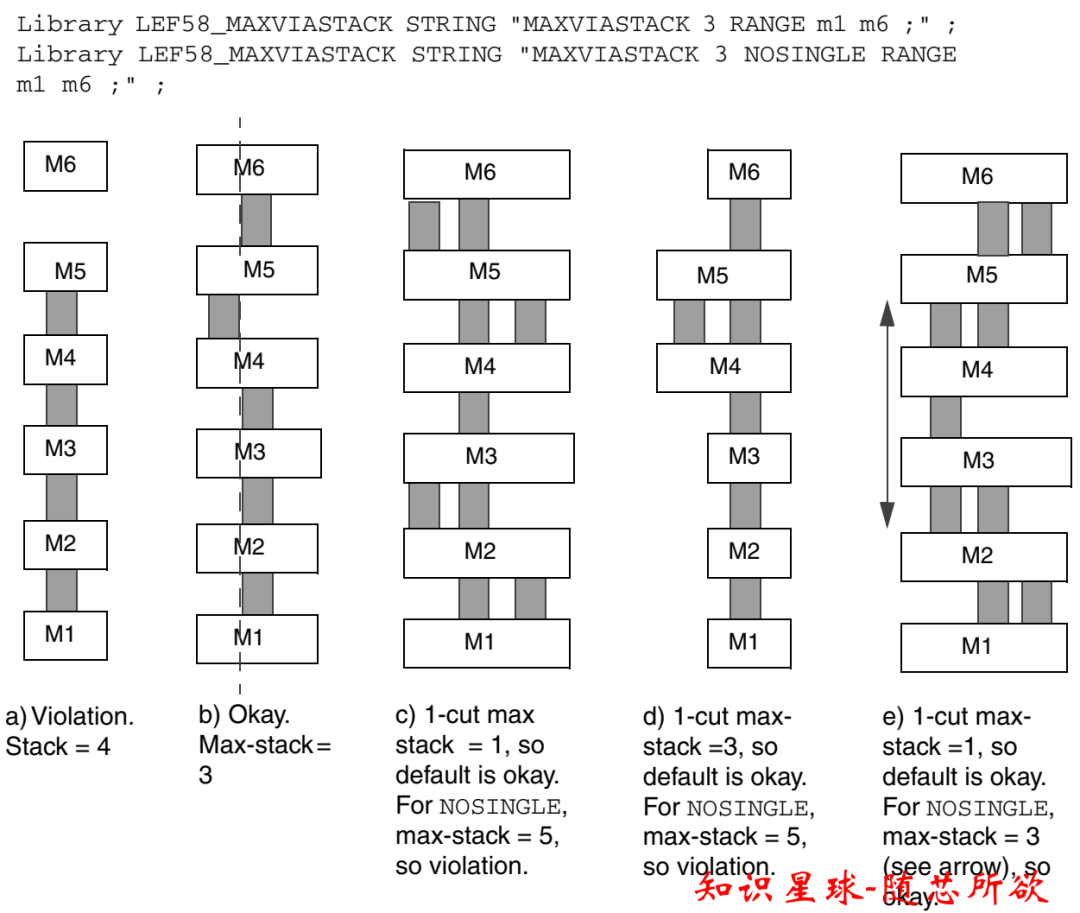

舉例:

如上圖所示,a和b都是只有single via堆疊,a從m1-m5堆疊了4層via,超過(guò)了第一行MAXSTACK 3 RANGE m1 m6的約束,b的話只有m1-m3,堆疊了3層via,沒(méi)有超過(guò)要求,所以沒(méi)有DRC違反。

c, d, e都是有multi cut via的情況,c的話如果只看signle via的話沒(méi)有超過(guò)下面tech LEF第一行的要求,如果同時(shí)考慮multi cut via的話,那么M1-M6的via都是有堆疊的,堆疊了5層via,所以違反了第二行MAXSTACK NOSINGLE 3 RANGE m1 m6的要求,會(huì)報(bào)DRC違反。

后邊的d e也是類(lèi)似。

問(wèn)題的修復(fù):

知道上面的規(guī)則之后,要想解這類(lèi)問(wèn)題就非常簡(jiǎn)單了,只要隨便把中間或者某層via錯(cuò)開(kāi)一段距離,讓它們之間沒(méi)有overlap就可以了。注意檢查錯(cuò)開(kāi)之后堆疊的via的數(shù)量是否滿(mǎn)足要求。不要出現(xiàn)這種情況:比如DRC要求只允許堆疊3層,現(xiàn)在堆疊了v1-v5,你想修這個(gè)問(wèn)題結(jié)果你挪動(dòng)了v5,那么還是解不了這個(gè)DRC的。

審核編輯:劉清

-

DRC

+關(guān)注

關(guān)注

2文章

149瀏覽量

36209

原文標(biāo)題:MaxViaStack DRC規(guī)則詳解

文章出處:【微信號(hào):集成電路設(shè)計(jì)及EDA教程,微信公眾號(hào):集成電路設(shè)計(jì)及EDA教程】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

有沒(méi)有哪位大神給詳細(xì)講解一下5509A的USB固件編程,一直找...

求大神講解一下labview程序

電氣設(shè)計(jì)規(guī)則檢查工具HyperLynx DRC

【直流電機(jī)驅(qū)動(dòng)器項(xiàng)目】板框的設(shè)置及電氣規(guī)則的設(shè)置詳細(xì)講解(第八集)

詳細(xì)的講解一下I/O模式下的程序與MM模式下的程序調(diào)試

AltiumDesigner的DRC規(guī)則參考

Altium顯示DRC錯(cuò)誤的檢查方法

PCB設(shè)計(jì)電氣規(guī)則檢查器解決DRC問(wèn)題

詳細(xì)講解一下農(nóng)業(yè)氣象儀器的組成部分

DRC規(guī)則是指什么?怎樣使用DRC規(guī)則減少PCB改版次數(shù)呢?

芯片后端設(shè)計(jì)的DRC是什么?

和Dr Peter一起學(xué)KiCad 4.8:設(shè)計(jì)規(guī)則檢查(DRC)

詳細(xì)講解一下MaxViaStack DRC的規(guī)則

詳細(xì)講解一下MaxViaStack DRC的規(guī)則

評(píng)論