1 前言

數模混合電路的設計,一直是困擾硬件電路設計師提高性能的瓶頸。眾所周知,現實的世界都是模擬的,只有將模擬的信號轉變成數字信號,才能方便做進一步處理。模擬信號和數字信號的轉變是否實時、精確,是電路設計的重要指標。除了器件工藝,算法的進步會影響系統數模變換的精度外,現實世界中眾多干擾,噪聲也是困擾數模電路性能的主要因素。 本文通過Ansoft公司的“AD-Mix Signal Noise Design Suites” 數模混合噪聲仿真設計軟件對數模混合設計PCB進行仿真,探索分析數模混合電路的噪聲干擾和優化設計的途徑,以達到改善系統性能目的。

2 數模混合設計難點

在數模混合設計中,有效分辨干擾源、干擾對象以及干擾途徑,是分析數模混合設計干擾的基礎。

2.1 干擾源、干擾對象

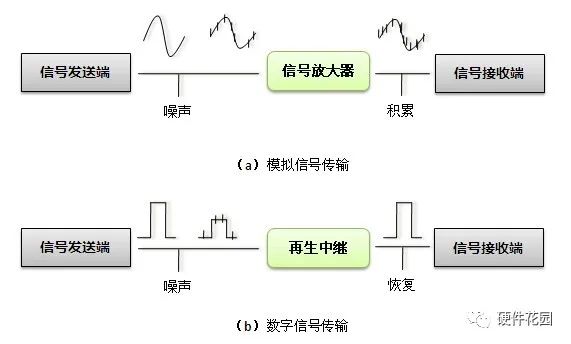

通常電路中的模擬信號,由于電壓和電流隨時間變化而連續變化,在設計和調試中,需要同時控制這兩個變量的話,是比較困難的。他們對外部的干擾比較敏感,所以通常作為被干擾對象做分析。 數字信號相對于模擬信號而言,只有隨時間變化的量化后電壓成分,抗干擾能力較強。但是這類信號變化快,特別是邊沿變化速度極快,高頻諧波成分豐富,對外釋放能量,所以通常作為干擾源來分析。

作為干擾源的數字電路部分多采用CMOS工藝,從而導致數字信號輸入端極高的輸入電阻,通常在幾十千歐到上兆歐姆。這樣高的內阻導致數字信號上的電流非常微弱,因而只有電壓有效信號在起作用,在數模混合干擾分析中,這類信號可以作為電壓型干擾源,如CLK信號,Reset等信號。除了快速交變的數字信號,數字信號的電源管腳上,由于引腳電感和互感引起的同步開關噪聲(SSN),也是數模混合電路中存在的重要一類電壓型干擾源。此外,電路中還存在一些電流信號,特別是直流電源到器件負載之間的電源信號上有較大的電流,根據右手螺旋定理,電流信號周圍會感應出磁場,進而引起變化的電場,在分析時,直流電源作為電流型干擾源。

2.2 干擾路徑問題

無論電壓型還是電流型的干擾源,在耦合到被干擾對象時,既可能通過電路傳導耦合,也可能通過空間電磁場耦合,或者二者兼有。 然而一般的仿真分析工具,往往由于功能所限,只能分析其中一種。例如在傳統的SPICE電路仿真工具中,只考慮電路傳導型的干擾,并不考慮空間電磁場的耦合;而一般的PCB信號完整性(SI)分析工具,只考察空間電磁場耦合,將所有的電源、地都看作理想 DC 直流,不予分析考慮。耦合路徑提取的不完整,也是困擾數模混合噪聲分析的重要原因。

2.3 電源、地的分割問題

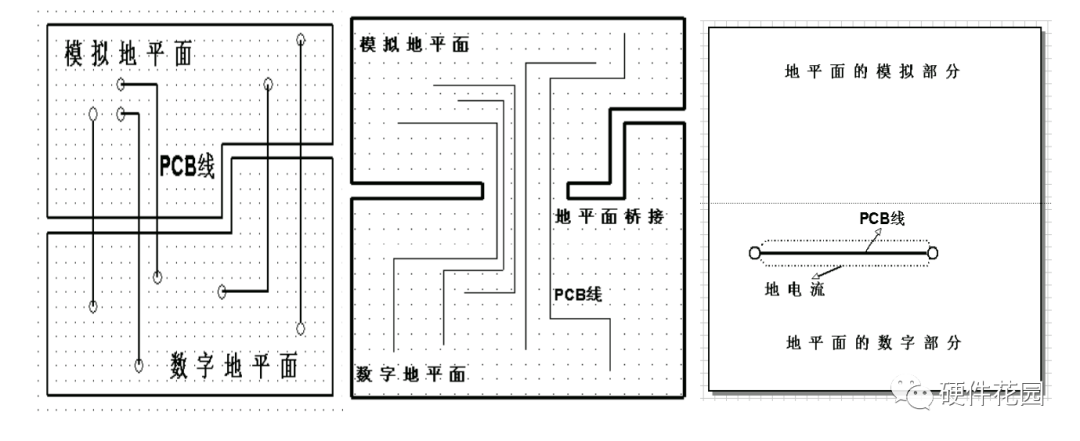

數模混合設計中,電源和地的劃分,是業內爭論的焦點。

傳統的設計中,數字和模擬部分被嚴格分開。然而隨著系統越來越復雜,數模電路集成度不斷提高。分割又會造成數字信號跨分割,信號回流不完整,進而影響信號完整性。

另外,電源的分割還造成電源分配系統的阻抗過高;有人提出“單點連接”:還是做分割,但是在跨分割的信號下方單點連接以避免跨分割問題;但是如果數模之間信號很多,難于分開,這種“單點連接”也存在困難,因而又有人提出不分割,只是保持數字和模擬部分不要交叉;還有一些資料介紹,在跨分割的信號旁邊包地線或者并聯電容,用來提供完整回流路徑。

電源、地平面分割

無論哪種方法,似乎都有一定道理,而且都有成功的先例,然而所有這些分割方案的有效性以及可能存在的問題,一直沒有檢驗的標準。

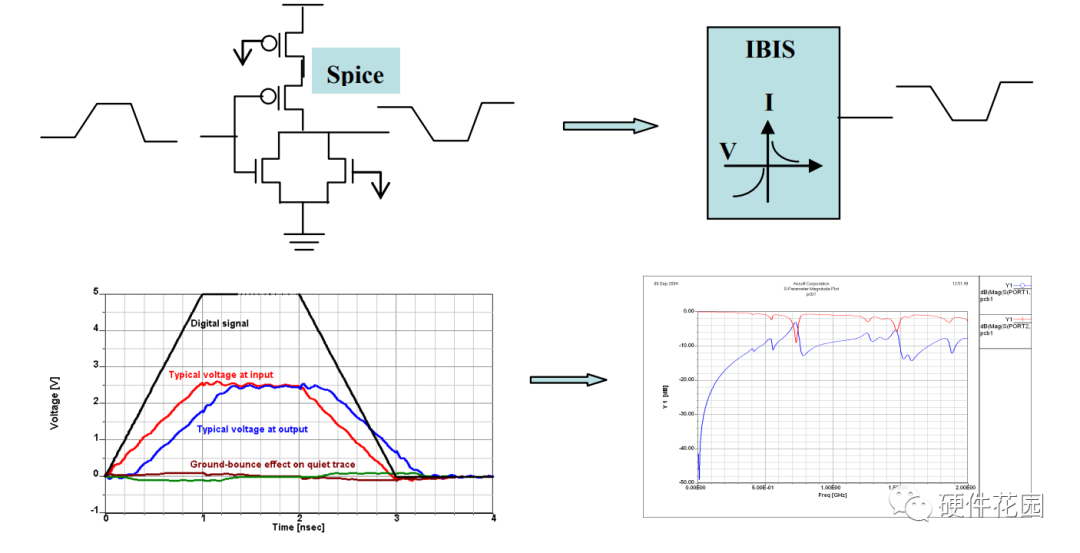

2.4 模型問題

數模混合電路的仿真,還存在模型的問題。業界普遍接受的模擬電路仿真模型還是 SPICE 模型,數字電路信號完整性分析使用IBIS模型。多家EDA公司的仿真軟件已經推出 支持多種模型的混合模型仿真器,然而擺在設計師案頭的主要困難是器件模型,特別是模擬器件模型很難得到。對于數字設計而言,時域的瞬態分析,即某一時間點上確定的電壓值,是仿真的主要手段,就像調試中的示波器那樣直觀。沒有精確的模型,瞬態分析就無法實現。然而對模擬設計,特別是噪聲分析,激勵源在時間軸上難于描述或很難預測,只知道他的頻率帶寬范圍和大致幅度,這時候我們通常會引入頻域掃頻分析,考察掃頻信號在關注點的變 化,如同頻譜分析儀的作用。或者干脆如網絡分析儀(NA)那樣考察信號或噪聲通過的通道的頻域SYZ參數,進而預測干擾發生的頻率和幅度。可見,數模混合噪聲分析,既需要支持混合模型的仿真器,也需要仿真器同時支持時域分析和頻域分析。

仿真模型

3 提高模數電路性能的關鍵

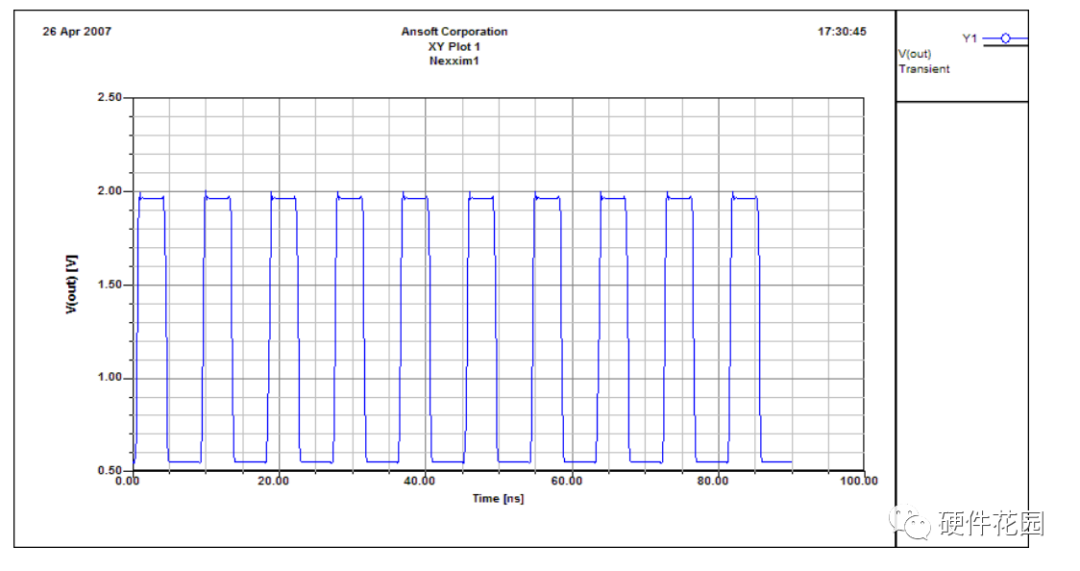

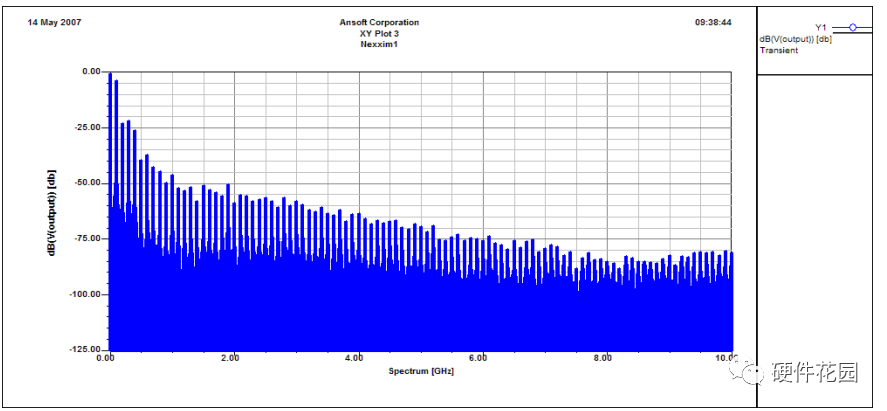

在解釋了數模混合電路仿真存在的主要困難后,下來我們來討論如何解決這些困難,從而仿真預測數模干擾進而解決數模干擾的問題。 3.1 干擾源的創建 首先是干擾源的創建和設置。干擾源分為電壓型和電流型的干擾源,電壓型干擾源通常是數字信號本身以及數字電源管腳;電流型干擾源通常是 DC 電源。數字信號通常表現為周期性的方波脈沖信號,在信號與系統教程中我們知道,這類周期信號經傅立葉變換后的頻譜,表現為高幅度的離散譜,這些頻譜會隨著頻率的提高而幅度降低,頻譜幅度與信號變化沿Tr, Tf以及占空比都有關系。

脈沖信號頻率

脈沖信號頻譜

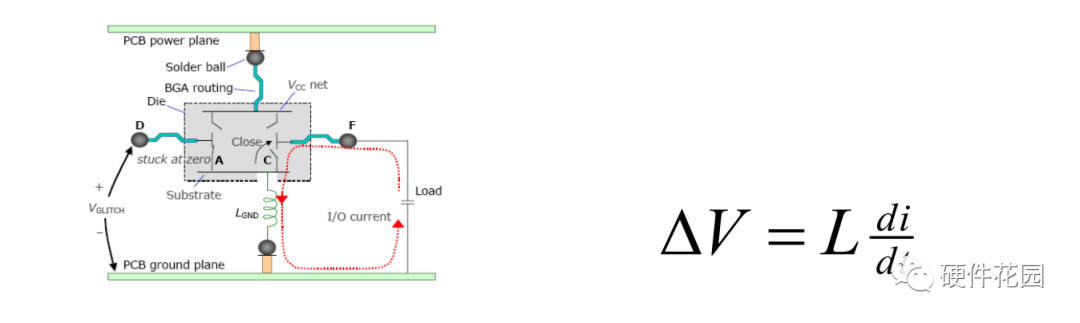

數字電源管腳上的噪聲,通常由于同步開關噪聲(Simultaneous Switch Noise)引起,而同步開關噪聲又是由于晶元上 IO 到的電源和地管腳之間的引線電感造成的,這個電壓波動會與電感大小和信號開關速度成正比,如下圖。現在的大規模 IC 中,管腳更多,封裝更大,信號開關速度更快,因而 SSN 會更嚴重,對模擬信號的干擾也就越大。

對地干擾等效成電感模型

同步開關噪聲在時域上表現為幅度較小的隨機脈沖,頻譜為連續頻譜,頻譜的幅度不隨頻率改變而變化,只與噪聲大小有關。可見,要精確分析電壓型的干擾源的影響,必須精確描述出來他們的時域和頻域的特性,才能準確分析。電源(VRM)作為電流型的干擾源,從直流來講,由于濾波電路和銅箔的電阻率,在 PCB上存在電流分布密度和直流壓降,整個壓降會影響模擬信號參考電位進而影響模擬電路性能。從交流來講,整個電路上有源和無源器件作為電源負載,工作頻率不一樣,電流大小會隨頻率而變化,而即使負載不隨頻率變化,電源電流輸出也是隨頻率變化而變化的參數。

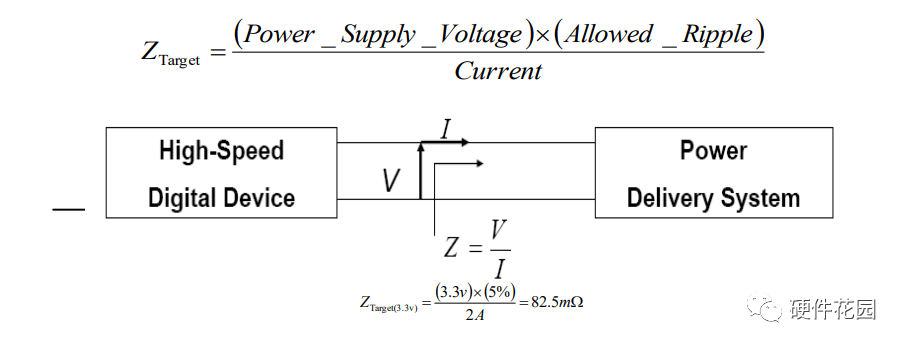

對這樣一種激勵和負載都變化且難以描述的傳輸系統,我們轉入考察電源通道的頻域SYZ 參數,特別是電源阻抗Z參數。我們估算出電源系統在工作頻率范圍內的最大電流,只要確保電源阻抗足夠小,就能保證電源電壓波動滿足指標要求。例如下圖,系統最大負荷電流2A,電壓3.3V,要求電壓噪聲控制在 5%即 0.165V,那么從電源到負載處的阻抗只要低于82.5ohm,就能滿足系統要求。

電源到負載的阻抗

3.2耦合路徑提取

干擾源討論后,我們再看耦合途徑的提取。數模混合噪聲,是通過電路傳導和電磁場耦合兩種方式對電路起作用的。

眾所周知,麥克思維方程和基爾霍夫電壓電流定律(KCL和KVL),構成了解決傳統電學問題的基礎。20 世紀60年代伯克利SPICE 推出后,解決了利用計算機工程計算求解電路KCL和KVL方程的問題,因而如今的電路設計仿真可以利用計算機輔助做到前所未有的規模,在SPICE中,就可以分析噪聲通過電路傳導的影響。在電磁場計算領域,20世紀80年代出現的有限元法(FEM),特別是Ansoft公司推出的三維結構分析工具HFSS(俗稱海飛絲),以其算法的先進和精確,被作為電磁場計算的標準而聞名。然而三維有限元算法,由于工程計算量巨大,一直作為RF微波設計的工具。為了應對 PCB上成百上千條網絡的電磁場計算,一些EDA公司開始簡化PCB電磁場求解的難度使用解析法,而數字電路對于求解精度要求并不高,這樣就出現了專門針對高速數字PCB仿真的信號完整性分析(SI)工具。然而由于解析法固有的局限性,無法考慮諸如跨分割、不完整電源地平面、非理想直流信號的影響,因此無法分析數模混合干擾這樣對精度要求更高的電磁場計算。

近年來,Ansoft 推出了專門針對PCB的電磁場分析工具SIwave,考慮到 PCB縱向長度與信號波長之間相差懸殊,它使用2維有限元算法,既保證了精度,又大大降低求解難度。結合了Ansoft的SPICE 仿真器和 2 維有限元電磁場計算的優勢,使得對數模混合噪聲完整耦合路徑提取和分析成為可能。

3.3分割問題

分割問題,一直是數模混合電路設計師的一個關注焦點。分割的目的,是為了提高數模之間的隔離度,使得數字部分干擾源的能量盡量少地傳遞到模擬信號端。然而分割又可能造成信號完整性,或者電源阻抗變化等問題。

關于這一點,單純的說分割或者不分割,單點連接還是提供回流路徑,都是不全面的。一方面,分割的目的是提高隔離度,只要不出現跨分割情況,可以做分割,然而不合理的層疊或濾波,反而會降低隔離度,分割沒有達到效果;另一方面,只要干擾源的噪聲幅度控制的足夠低,去耦濾波等策略合適,提高數模之間的隔離度達到一定要求,沒有必要做分割;

再有,跨分割不是絕對不能出現的,合理的層疊和去耦策略可以有效避免跨分割的影響。

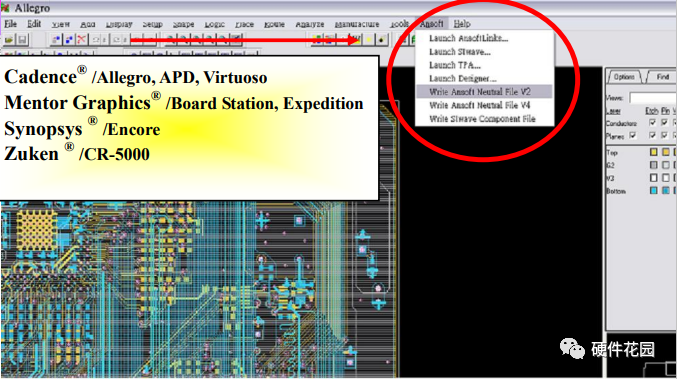

4 仿真工具在數模混合設計中的應用

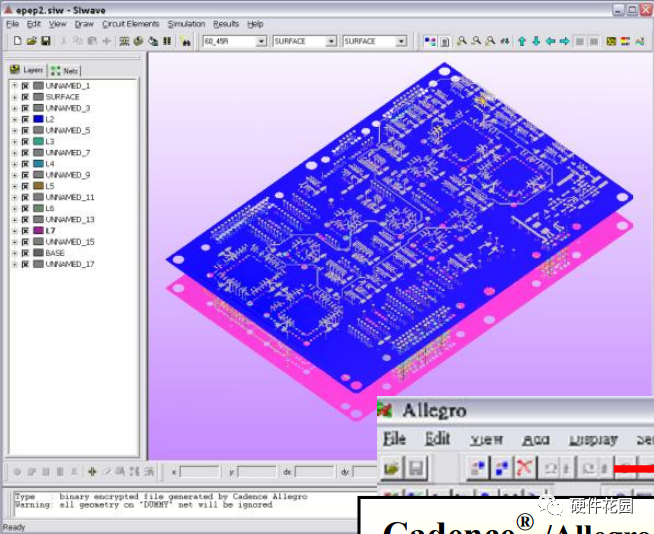

Ansoft 公司的“AD-Mix Signal Noise Design Suites”數模混合噪聲仿真設計軟件包括:PCB全波整板級信號完整性/電源完整性及電磁兼容/電磁干擾仿真設計和參數抽取工具SIwave;Ansoft工具和其他CAD、EDA設計工具的接口AnsoftLinks;電路、系統和多層平面電磁場設計仿真工具Ansoft DesignerSI/Nexxim;此外,還可以選配三維結構電磁場仿真和 EMC分析工具 Eminence。Ansoft 所有的工具都基于Windows 設計風格,菜單和快捷鍵方式操作方便,可以直接從現有的電路設計軟件中導入Ansoft 的仿真軟件, 如Protel,PowerPCB,CR5000,Allegro,Boardstation和 Expedition。而且各個模塊數據通用,可以相互間直接調用。 4.1導入數據

仿真第一步,通過 Ansoft Links 導入 PCB數據到 SIwave,設置層疊材料特性和厚度信息。當然層厚和材料可以在PCB工具中設定好,直接導入SIwave。

4.2設置數字信號電壓型干擾源

第二步,設置數字信號電壓干擾源。在Ansoft DesignerSI/Nexxim 中,我們把電路中快速變化的數字信號輸出模型調入,通常是IBIS模型。利用IBIS模型輸出端口中給出的Vref,Rref 和Cref參數,搭建激勵和負載電路做瞬態時域分析。把時域分析的結果輸出成頻譜參數并以表格方式輸出成文本文件,這個隨頻率變化幅度的掃頻源就作為數字信號端的干擾源進行分析了。

4.3同步開關噪聲仿真

第三步、仿真同步開關噪聲。同步開關噪聲作為數字電源腳的電壓型干擾源,需要通過時域仿真確定噪聲的幅度。首先我們在SIwave中提取包括同步信號的輸出輸入端口,VRM電源輸出到IC 的VCC管腳上的端口的多端口 S 參數模型,并將該模型輸出到 Ansoft DesignerSI/Nexxim 中。有時候,器件VCC管腳可能不止一個,SIwave 提供了創建Pin Group的功能,可以將多個相同電平的管腳合成一個Pin Group,然后添加端口。在Ansoft DesignerSI/Nexxim 中,我們給所有的輸入輸出端口加上仿真模型,通常也是 IBIS 模型,在VRM電源輸出添加理想直流源,然后探測VCC管腳上的電壓波動,這個波動電壓就是SSN。需要指出的是,通常SSN包括PCB和封裝上耦合電感引起的電壓波動,在這里仿真的只是由于PCB布線引起的部分,如果有IC封裝的S參數模型,我們可以仿真完整的SSN。

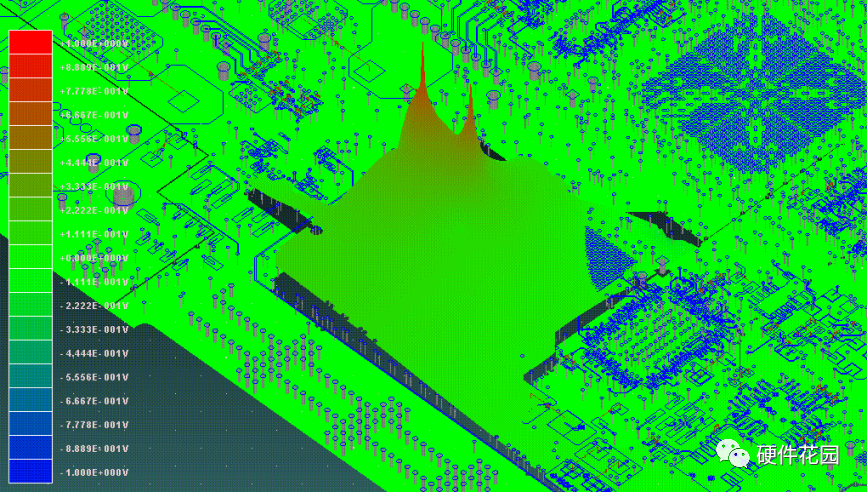

得到 SSN 的電壓后,就可以在SIwave中的VCC管腳上添加獨立的掃頻源做干擾分析了。所有干擾源確定后,我們就可以在SIwave中做掃頻分析,用戶可以在自己關心的位置,添加電壓探頭,輸出實際干擾大小波形,也可以將整個PCB的電壓波動以動畫方式反映。

4.4分析電流型干擾源

第四步,分析電流型干擾源。在 SIwave 中允許用戶添加電流型的干擾源,與電壓型干擾源類似,這個干擾源的幅度可以是不隨頻率變化的獨立源,也可以是隨頻率變化的,只要能夠給出變化特性。一般來講,我們可以對已知DC電流大小的電源處添加獨立電流源,分析他的電流分布密度和 DC 直流壓降。對于頻變的電流源,我們只能依靠在電源負載端添加端口,分析隨頻率變化的電源阻抗Z參數,來評估噪聲的大小。

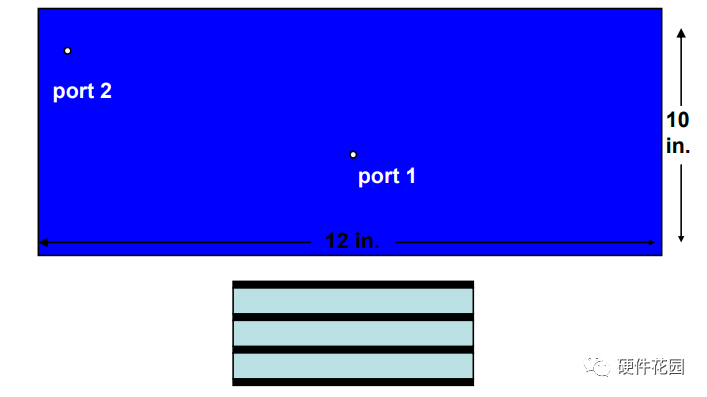

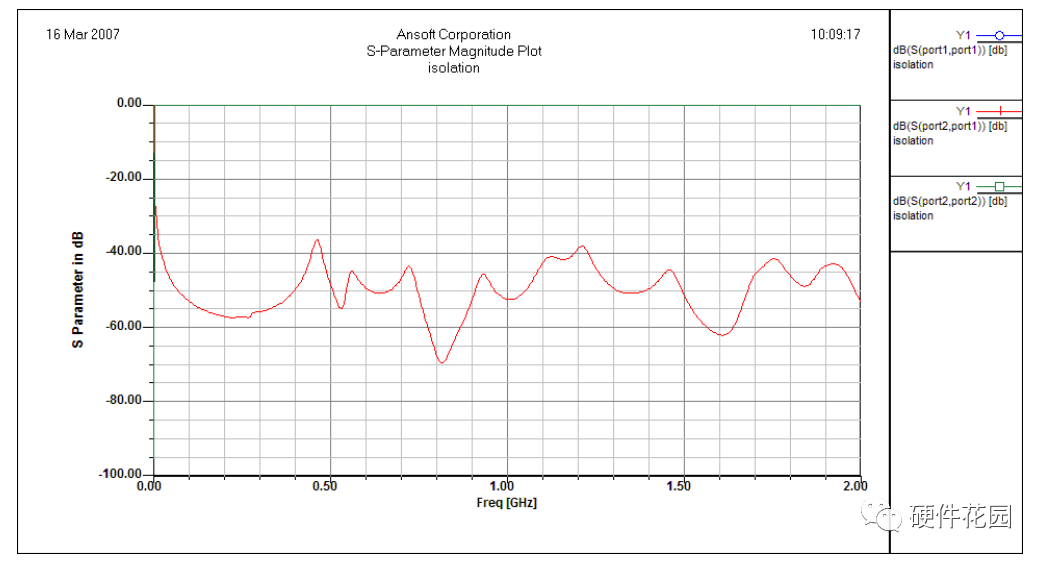

4.5分析隔離度

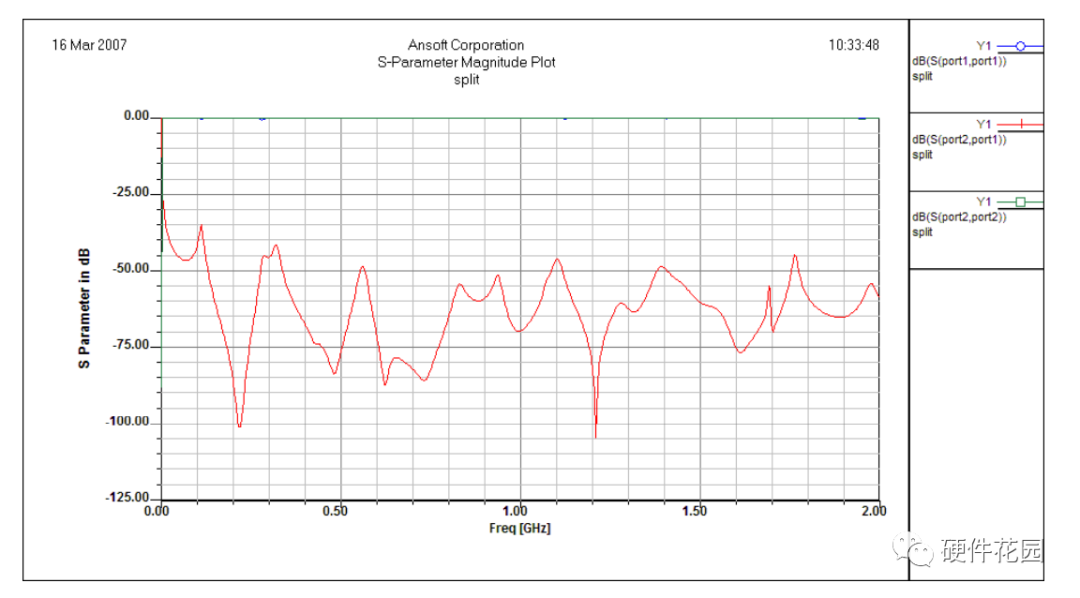

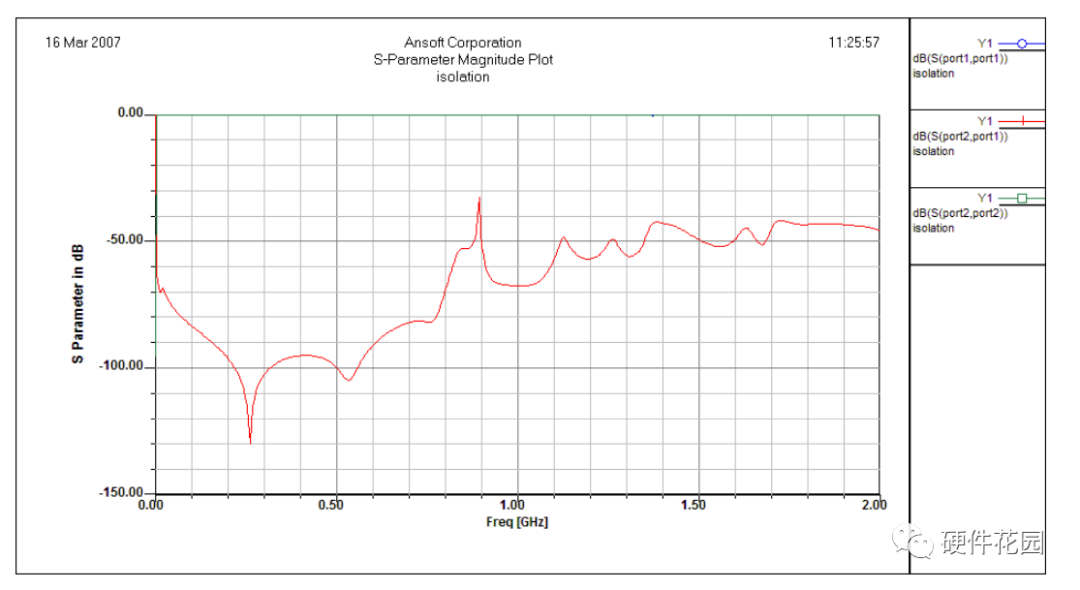

第五步,分析隔離度。除了以上干擾分析外,SIwave 另外一個主要功能就是考察電源地的分割。在沒有有源器件模型,無法給出干擾源幅度的情況下,考察數模之間的隔離度,也是解決問題的一個好方法。在 SIwave 中,在干擾源和受干擾對象點分別添加端口,分析S參數,看看隔離情況是否良好。我們在 SIwave 中,做出一個12x10inch 的四層 PCB 例子,分別是頂層信號層,第二層電源,第三層 GND 和底層信號層,再分別模擬兩個點作為干擾源和被干擾對象,分析各種情況下的隔離度。

不分割時的隔離度

分割后的隔離度

單點連接時的隔離度

不分割,添加20個電容(10個47uF, 10個0.1uF)后的隔離度

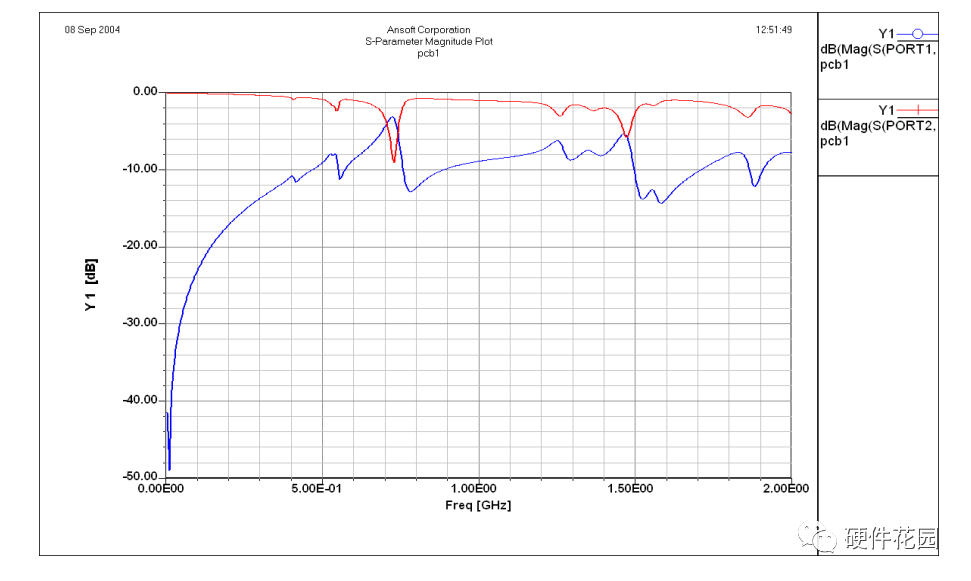

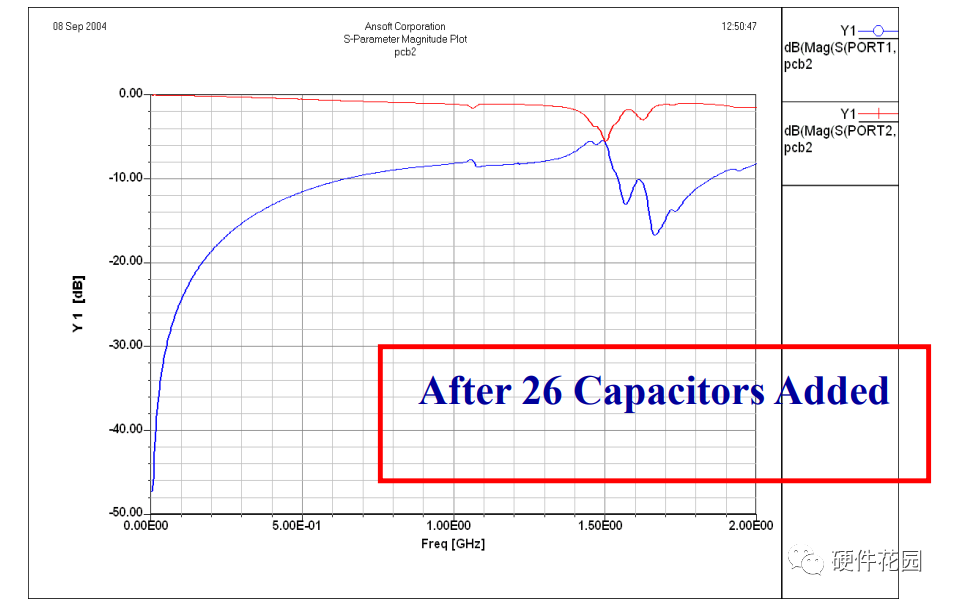

對于跨分割對數字信號的影響,由于傳統的SI工具并不能分析,所以常常用設計規則來約束,致使很多情況布局布線困難,或者增加層厚和成本。SIwave 可以精確分析跨分割信號的傳輸和反射特性,確定分割到底對那個頻率的諧波有多大的作用。由于數字信號的頻譜離散特性,只要這個波動頻點不在諧波處,就不會對信號有太大的影響。此外,我們在跨分割的兩個電源上PCB上添加去耦電容,也可以改變波動頻點的位置,只要它落在數字信號的轉折頻率之外,也不會對信號有太大的影響。下圖是一個跨分割信號的 S11 和 S21 參數,添加去耦電容后的S11和S21參數比較。

添加電容前S11 和 S21 參數

添加電容后S11 和 S21 參數

5 小結

數模混合噪聲的分析,是一個復雜的問題,牽扯到電路求解和電磁場計算的問題,需要時域仿真和頻域仿真的協同分析。這里僅提出一點實踐中的經驗和體會,供大家討論以求共同進步。電路的設計中沒有絕對一成不變的規則,必須針對問題,找到針對性的分析手段和解決方案,方能事半功倍。

審核編輯:湯梓紅

-

pcb

+關注

關注

4333文章

23223瀏覽量

401854 -

電路設計

+關注

關注

6679文章

2474瀏覽量

206205 -

仿真

+關注

關注

50文章

4151瀏覽量

134407 -

數模混合電路

+關注

關注

0文章

9瀏覽量

10484

原文標題:通過仿真有效提高數模混合設計性能——硬件工程師必讀攻略

文章出處:【微信號:硬件技術后花園,微信公眾號:硬件技術后花園】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通過仿真有效提高數模混合設計性能——硬件工程師必讀攻略

通過仿真有效提高數模混合設計性能——硬件工程師必讀攻略

評論