作者:Yi Zhang and Michelle Viani

隨著消費者對增強數據服務和更多帶寬使用的需求不斷增加,無線通信網絡正在迅速發展。新一代無線通信系統需要更高的數據吞吐量、更低的功耗和更高的可靠性。這些要求經常相互沖突。滿足這些需求需要高采樣率、高信號帶寬和高能效數模轉換器(DAC)解決方案。新一代高速DAC產品具有GSPS采樣率和輸入數據速率,為多頻段、多標準無線電基站提供多載波GSM兼容性能,同時降低系統總功耗和散熱密度。本文討論高速轉換器如何通過提供更高的采樣速率、更大的數據帶寬和更低的功耗來幫助系統設計人員推進無線通信系統設計的創新前沿。

高帶寬下的系統挑戰

現代移動基站的傳輸帶寬超過300 MHz的情況并不少見。支持更寬的日期帶寬和數字預失真技術的要求提高了高速DAC產品可用信號帶寬和動態性能的標準。實現更高系統帶寬的挑戰有三個方面。

首先,更高的信號帶寬需要更快的DAC采樣速率。奈奎斯特-香農采樣定理要求轉換器采樣速率至少是要合成信號的兩倍。因此,在不考慮其他設計約束的情況下,DAC采樣速率需要以信號帶寬速率的2倍增加。模擬重建濾波是系統設計中推動更快DAC采樣速率的另一個主要因素。在無線發射器中內置磚墻模擬濾波器既不可行也不高效。實際上,系統要求DAC采樣速率在合成信號帶寬上具有一定的過采樣比,以便在所需信號和需要抑制的高頻DAC采樣鏡像之間建立濾波器過渡帶。例如,如果要合成的信號在150 MHz的中心頻率周圍傳播±50 MHz,則DAC輸出信號的高端為200 MHz,而當信號以300 MHz為中心,帶寬為±150 MHz時,則為450 MHz。可以看出,第二種情況需要具有更高采樣率的DAC。

其次,更高的信號帶寬需要更快、更可靠的轉換器日期接口。所需的信號帶寬與傳輸日期吞吐量成比例增加。為了使用I/Q調制實現300 MHz系統帶寬,雙通道DAC(I和Q)的組合輸入數據速率為750 MSPS,考慮0.2的濾波器滾降因子。這意味著輸入日期周期為1.33 ns,這給系統設計人員帶來了很大的壓力,要求他們最大限度地減少數據總線上的位間時序失調,以滿足建立和保持時序要求。對于傳統的并行數據接口方案,如LVDS和CMOS,這是非常具有挑戰性的。新型JESD204B高速串行接口為遷移到更高的數據速率提供了可靠且可擴展的解決方案。

第三,集成電路(IC)器件不是理想的元件。DAC也不例外。較高的輸出帶寬要求DAC器件具有更好的動態性能,原因有兩個。動態范圍通常隨著DAC輸出頻率的增加而減小。此外,當帶寬較大時,更多的雜散內容往往會落在帶內。但是,系統雜散要求不會隨信號帶寬而擴展或放松。無論支持的信號帶寬如何,移動基站仍然需要滿足受監管的發射模板要求。具有卓越動態性能的DAC簡化了系統的頻率規劃和濾波。

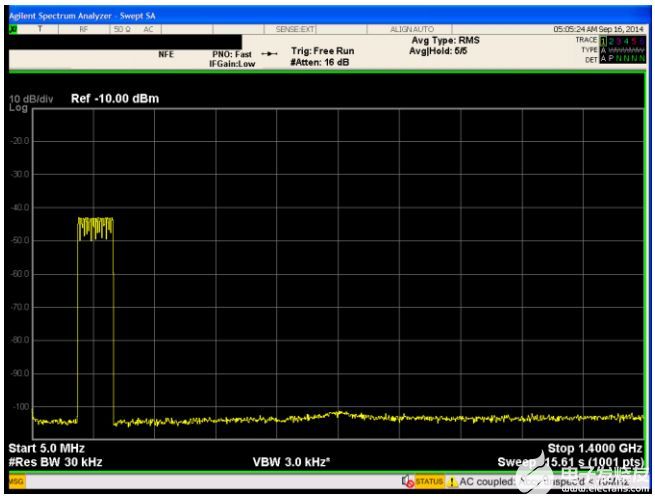

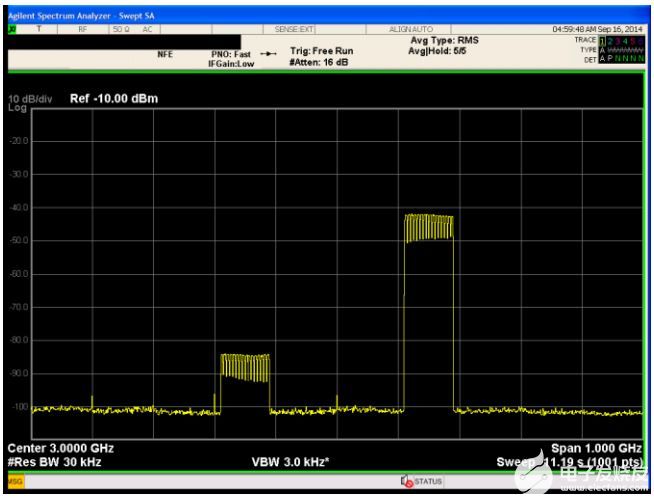

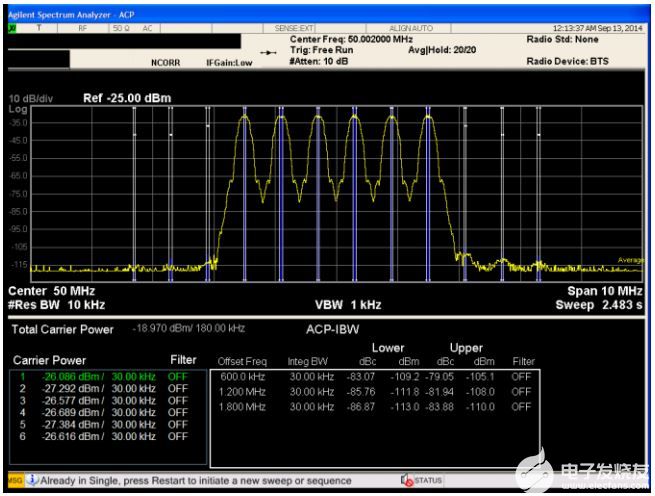

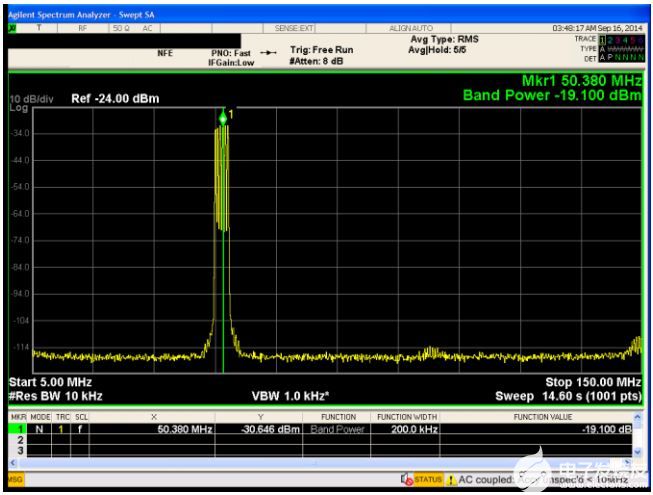

圖1和圖2顯示了AD9144 DAC以2800 MSPS的DAC采樣速率合成80 MHz信號(16載波W-CDMA)的實測頻譜性能。

圖1.測量的AD9144 DAC的寬帶性能(高達奈奎斯特頻率) 合成16載波W-CDMA信號,f代數轉換器= 2800 MSPS。

圖2.在ADRF6720下測得的寬帶性能1QMOD輸出為3 GHz RF頻率,AD9144 DAC輸出(如圖1所示)驅動QMOD。

低功耗和高可靠性的系統挑戰

系統設計人員在增加傳輸帶寬和數據容量方面還面臨著其他挑戰。這些挑戰包括功耗、散熱和系統可靠性。這些維度通常與更高系統帶寬的目標正交,有時甚至沖突。因此,系統設計人員需要一種新的DAC產品,該產品能夠在同一封裝中提供更高水平的功能集成、更低的功耗、更低的工作熱密度和更寬的帶寬。

近年來,高速DAC產品發展迅速,DAC產品中集成了更多的數字和模擬功能。兩個明顯的例子是DAC片上時鐘乘法器PLL和通信專用信號處理功能。這些功能過去在系統的其他位置實現,例如高速時鐘合成器和基帶ASIC/FPGA。具有這些功能的DAC不僅可以降低整體BOM成本,還可以為更簡單、更可靠的設計提供途徑。利用DAC中的時鐘倍頻器,系統只需為器件提供一個低頻參考時鐘。時鐘乘法器鎖定至外部參考時鐘,并在內部為DAC生成高速采樣時鐘。這意味著無需擔心PCB上的高速時鐘耦合和走線阻抗匹配。功率檢測和保護等新的數字功能為射頻鏈提供了額外的保護層,防止超量程信號或異常系統行為損壞。盡管功能集成度更高,但與上一代產品相比,DAC器件的功耗基本保持不變,甚至有所下降。高速DAC技術在更精細的硅工藝節點上的進步在應對系統挑戰方面發揮著重要作用。

除了消耗更少的功率和更小的碳排放足跡外,降低組件功耗的另一個重要好處是更低的熱密度。無線通信系統通常被限制在防水金屬機箱內。尺寸和重量限制通常不允許主動冷卻。IC元件產生的熱量通過機箱散發。機箱內部的型腔和PCB溫度可能非常高,以至于開始影響系統的長期可靠性。積聚的熱量可能會影響PCB的機械特性、元件和電路板之間的焊點,并加速IC元件電氣規格的長期老化變化。系統中的熱量分布/散發不均勻。貢獻主要來自信號處理豐富的幾個來源。高速DAC就是其中之一。因此,功能豐富且功耗低的DAC對系統設計人員非常有吸引力。

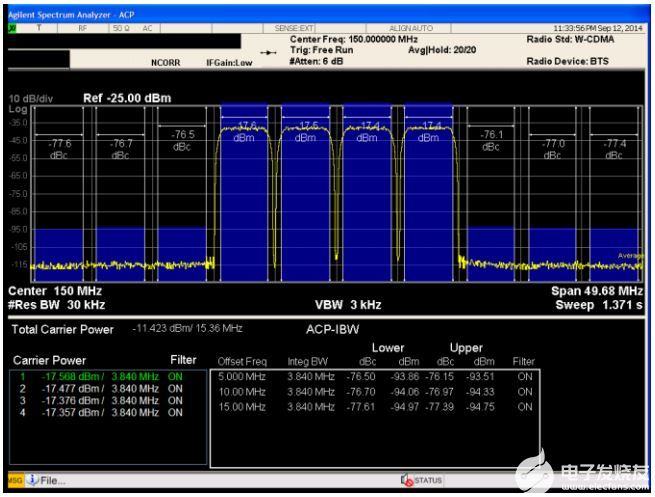

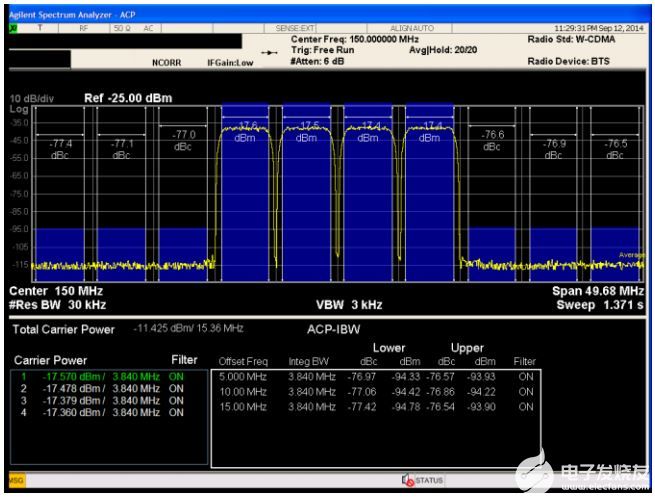

圖3和圖4顯示了AD9144在DAC采樣速率為1966 MSPS時合成4載波W-CDMA信號的實測性能,片內DAC時鐘乘法器分別打開和關閉。

圖3.在啟用片內時鐘乘法器的情況下,在150 MHz輸出頻率下測得的AD9144的4載波W-CDMA ACLR性能,f裁判= 245.76兆赫,f代數轉換器= 1966 MSPS。

圖4.在禁用片內時鐘乘法器的情況下,在150 MHz輸出頻率下測得的4載波W-CDMA ACLR性能AD9144,f代數轉換器= 1966 MSPS。

通用平臺設計中的系統挑戰

在要求覆蓋范圍更廣、帶寬更高的同時,消費者對日期服務需求的快速擴張也要求多標準無線電 (MSR) 基站。不同的無線電技術和不斷增加的頻率分配使控制網絡和降低成本變得更加復雜。滿足這些需求需要一種高效且相對便宜的解決方案來解決構建MSR基站的問題,這是一種通用的平臺設計。DAC技術的進步支持基站設計的這種演變。多載波GSM(MC-GSM)通常被認為是具有最嚴格動態范圍要求的空氣標準。MC-GSM測試通常用于判斷DAC產品是否支持通用平臺設計。

圖5和圖6顯示了AD9144以1966 MSPS的DAC采樣速率合成6 C-GSM信號的實測性能。

圖5.在50 MHz DAC輸出頻率下測得AD9144的6C-GSM IMD性能,f代數轉換器= 1966 MSPS。

圖6.在50 MHz DAC輸出頻率下測得AD9144的6 C-GSM寬帶性能,f代數轉換器= 1966 MSPS。

總結

現代無線通信網絡正在不斷發展,以提供更多的日期服務和更多的帶寬使用。為了支持這一趨勢,新一代無線通信系統需要具有更高的數據吞吐量、更低的功耗和更高的可靠性。高速DAC技術的進步,如ADI公司的AD9144,實現了下一代多標準無線電設計,并幫助系統設計人員在多個關鍵技術維度上實現了突破性創新。

審核編輯:郭婷

-

控制器

+關注

關注

112文章

16332瀏覽量

177806 -

dac

+關注

關注

43文章

2291瀏覽量

190975 -

無線通信

+關注

關注

58文章

4564瀏覽量

143496

發布評論請先 登錄

相關推薦

高速轉換器技術的進步使下一代無線通信系統設計成為可能

高速轉換器技術的進步使下一代無線通信系統設計成為可能

評論