在某些應用中,原始模擬帶寬至關重要,隨著GSPS或RF ADC的出現,奈奎斯特區在短短幾年內增長了10倍,達到了多GHz的跨度。這有助于這些應用進一步超越地平線,但達到X波段。 (12 GHz 頻率),仍然需要更多的帶寬。在信號鏈中使用采樣保持放大器(THA)可以從根本上擴展帶寬,遠遠超出ADC采樣帶寬,并提供最需要帶寬的設計所需的要求。在本文中,我們將證明設計人員在我們最新的RF市場轉換器之一前使用THA時可以實現10 GHz帶寬。

介紹

GSPS轉換器在縮短RF信號鏈和在FPGA中創建更多資源結構方面具有優勢(例如,在消除前端的混音下降級和后端包含數字下變頻器(DDC)時),由于GSPS轉換器在縮短RF信號鏈方面具有諸多優勢,因此在某些應用中仍然需要高頻原始模擬帶寬(BW),這遠遠超出了這些RF轉換器所能達到的范圍。實現。在這些應用中,尤其是在國防和儀器儀表行業(無線基礎設施緊隨其后),人們仍然有興趣將帶寬完全擴展到甚至超過10 GHz - c超過C波段,并在可能的情況下完全涵蓋X波段。隨著高速ADC技術的改進,在GHz區域高速精確分辨非常高的中頻(IF)的需求也在增加,讓位于寬度超過1 GHz的基帶奈奎斯特區并迅速攀升。該聲明在發表時可能已經過時,因為該領域的發展非常快。

這帶來了兩個挑戰:轉換器設計本身和將信號內容耦合到轉換器的前端設計,例如放大器、巴倫和PCB設計。即使轉換器的性能非常出色,前端也必須能夠保持信號質量。這些應用需要使用分辨率為8位至14位的高速GSPS轉換器,但請記住,為了滿足特定應用的匹配,需要滿足許多參數。

根據本文的定義,寬帶是指使用大于 100 MHz 的信號帶寬,范圍從近直流到 5 GHz 到 10 GHz 頻率區域。在本文中,將討論寬帶THA或有源采樣網絡的使用,以實現無限遠和更高的帶寬(抱歉,目前沒有可用的玩具總動員表情符號),并強調其背景理論,該理論使RF ADC的帶寬擴展成為可能,而RFADC本身可能沒有該功能。最后,將揭示考慮因素和優化技術,以幫助設計人員在多GHz區域實現可行的寬帶解決方案。

奠定基礎

在雷達、儀器儀表和通信觀測等應用中,GSPS轉換器被吸引是很自然的,因為這提供了更寬的頻譜,從而擴展了系統的范圍。然而,更寬的頻譜對ADC本身的內部采樣保持提出了更大的挑戰,因為它通常沒有針對超寬帶工作進行優化,而且ADC在這些較高模擬帶寬區域中的帶寬通常有限,高頻線性度/SFDR也會下降。

因此,在ADC前面使用單獨的THA是一種可能的解決方案,可以在精確的時間時刻對非常高的模擬/RF輸入信號進行采樣。該過程通過一個低抖動采樣器進行信號采樣,并降低ADC在更寬帶寬范圍內的動態線性度要求,因為在RF模數轉換過程中采樣值保持不變。

其結果是模擬輸入帶寬的大幅擴展,與單獨的RF ADC性能相比,THA-ADC組件的高頻線性度和高頻SNR得到大幅改善。

THA的特點和概述

THA 在 18 GHz 帶寬范圍內提供精確的信號采樣,從直流到超過 10 GHz 輸入頻率具有 9 位至 10 位線性度、1.05 mV 噪聲和 <70 fs 隨機孔徑抖動。該器件的時鐘頻率可達4 GSPS,動態范圍損耗最小,例如HMC661和HMC1061。這些THA可用于擴展高速模數轉換和信號采集系統的帶寬和/或高頻線性度。

單列THA有一個THA(如HMC661),并產生由兩個段組成的輸出。在輸出波形的跟蹤模式間隔(正差分時鐘電壓)中,該器件表現為單位增益放大器,在輸出級復制輸入信號,受輸入帶寬和輸出放大器帶寬限制的影響。在器件的正負時鐘轉換處,它以非常窄的采樣時間孔徑對輸入信號進行采樣,并在負時鐘間隔期間將輸出保持相對恒定,其值代表采樣瞬間的信號。單列器件(與其兄弟雙列THA HMC1061相反)通常更適合使用ADC進行前端采樣,因為大多數高速ADC已經內部集成了THA,通常帶寬要小得多。因此,在ADC前面增加一個THA會形成一個復合的雙列組件(如果使用雙列HMC1061,則形成三列),而THA位于轉換器前面。對于相同的技術和設計,單列器件通常比雙列器件具有更好的線性度和噪聲,因為單列器件的級數較少。因此,單列器件通常是采用高速ADC進行前端采樣的最佳選擇。

圖1.采樣保持拓撲:(1a) 單列,(1b) 雙列。

延遲映射 THA 和 ADC

在開發采樣保持和ADC信號鏈時,最困難的任務之一是在THA捕獲采樣事件的時刻與應將其移動到ADC上以重新采樣事件之間設置適當的時序延遲。在兩個有效的采樣系統之間設置這個完美的時間增量的過程稱為延遲映射。

在電路板上完成這個過程可能很繁瑣,因為由于PCB板上的時鐘走線傳播間隔、內部器件組延遲、ADC孔徑延遲以及將時鐘分成兩個不同段所涉及的相關電路(一個時鐘跡線用于THA,一個時鐘跡線用于ADC),紙質分析可能不會考慮適當的延遲。設置THA和ADC之間延遲的一種方法是使用可變延遲塊。這些器件可以是有源的,也可以是無源的,以便對THA采樣過程進行適當的時間對齊,并將其交給ADC進行采樣。這保證了ADC對THA輸出波形的建立保持模式部分進行采樣,從而產生輸入信號的準確表示。

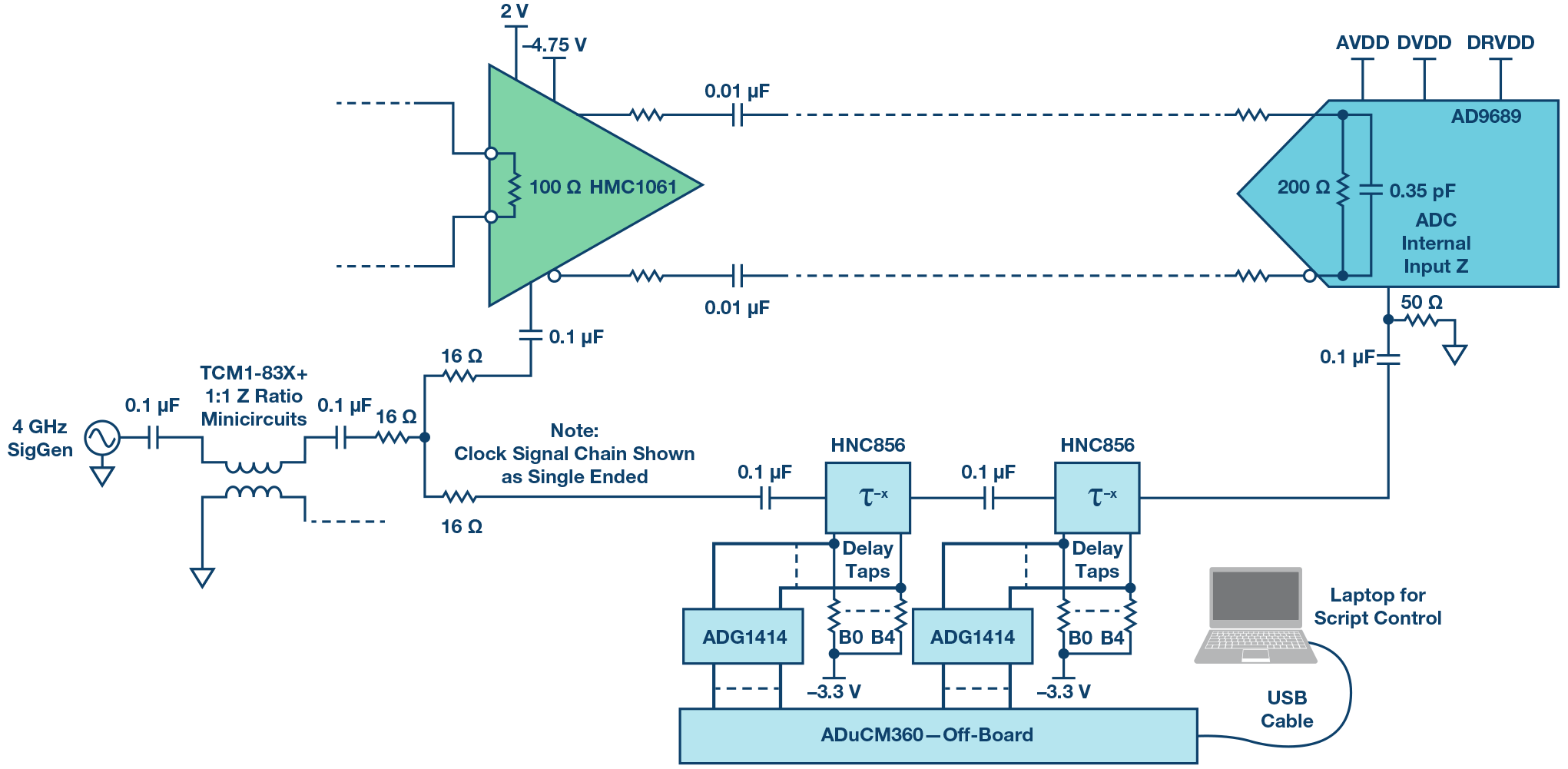

如圖2所示,HMC856可用于啟動延遲。這是一款 5 位/引腳可搭接器件,固有延遲為 90 ps,可變延遲步長為 3 ps 步長或 2 ps5,以及 32 種可能的階梯式延遲。引腳綁帶設備的缺點是設置/移動每個延遲設置。HMC856上的每個位引腳都需要被拉至負電壓,以啟用新的延遲設置。因此,在下拉電阻器中焊接32種組合以找到最佳延遲設置可能是一項繁瑣的任務,因此開發了自動化電路的使用,以幫助縮短延遲設置過程,使用串行控制的SPST開關和板外微處理器。

圖2.延遲映射電路。

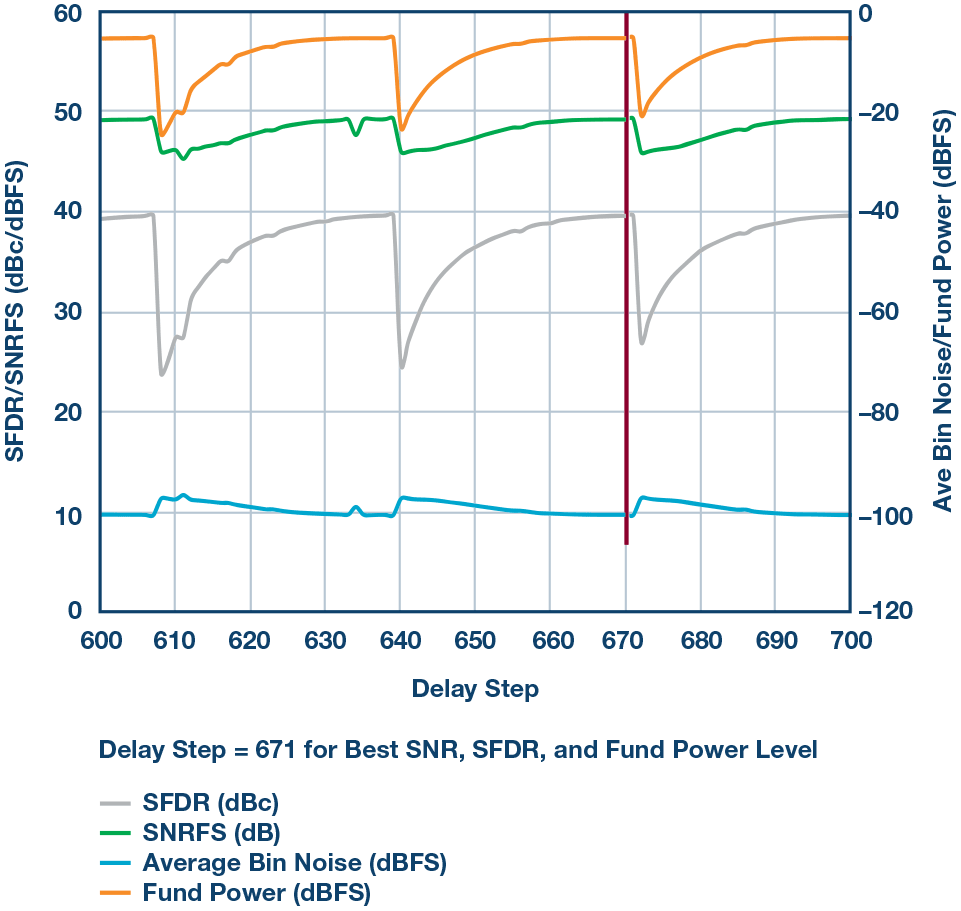

為了捕獲最佳延遲設置,將信號施加到THA和ADC組合,這應該超出ADC的帶寬范圍。在這種情況下,我們選擇了~10 GHz信號,并應用了在FFT顯示器上捕獲的–6 dBFS電平。延遲設置現在以二進制步進方式掃描,使信號保持在電平和頻率恒定。FFT現在在掃描過程中顯示和捕獲,在每個延遲設置下收集基波功率和無雜散動態范圍(SFDR)數字。

如圖3a所示,基波功率、SFDR和SNR會隨著應用每個設置而變化。如圖所示,當在THA將采樣拋出到ADC之間更優化地放置樣本位置時,基波功率將處于最高水平,而SFDR應處于最佳性能(即最低)。圖3b顯示了延遲映射掃描的放大視圖,概述了延遲設定點671,這是延遲應保持固定的窗口/位置。請記住,延遲映射過程僅對系統的相關采樣頻率有效,如果設計需要不同的采樣時鐘,則需要重新掃描。在這種情況下,采樣頻率為4 GHz,這是該信號鏈中使用的THA器件的最高采樣頻率。

圖 3a.映射每個延遲設置下的信號幅度和SFDR性能結果。

圖 3b.映射每個延遲設置(放大)的信號幅度和SFDR性能結果。

為大量原始模擬帶寬設計前端

首先,當您應用中的關鍵目標是吞噬10 GHz帶寬時,我們顯然開始從RF角度考慮。請注意,ADC仍然是電壓型器件,不考慮功率。因此,在這種情況下,匹配一詞是一個應該明智使用的術語。研究發現,幾乎不可能將每個頻率的轉換器前端與100 MSPS轉換器相匹配——多GHz RF ADC不會有太大區別,但挑戰仍然存在。術語匹配應定位為表示優化,從而為前端設計提供最佳結果。這將是一個包羅萬象的術語,其中輸入阻抗、交流性能(SNR/SFDR)、信號驅動強度或輸入驅動以及帶寬及其通帶平坦度為該特定應用提供最佳結果。

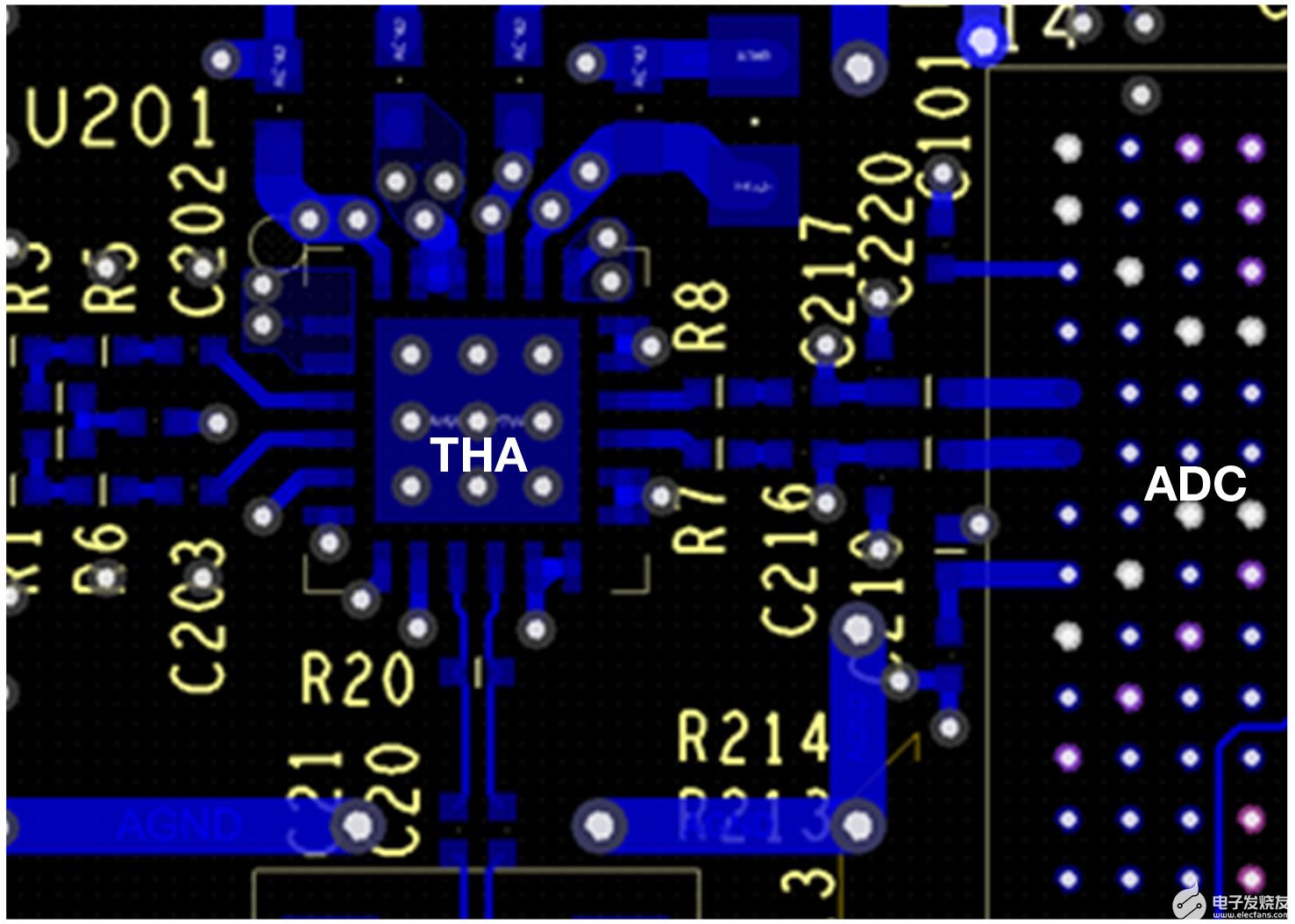

這些參數最終定義了系統應用程序的匹配項。在開始寬帶前端設計時,布局可能是關鍵,同時最大限度地減少必要的元件數量,以減少兩個相鄰IC之間的損耗。為了獲得最佳性能,兩者都至關重要。將模擬輸入網絡連接在一起時需要特別注意。走線長度和匹配走線長度以及最小化過孔數量是最重要的,如圖4所示。

圖4.THA 和 ADC 布局。

這兩個差分模擬輸入需要連接在一起并連接到THA輸出,以形成單個前端網絡。為了盡量減少過孔的數量和總長度,這里特別注意將過孔從兩個模擬輸入路徑中拉出,并幫助抵消走線連接中的任何存根。

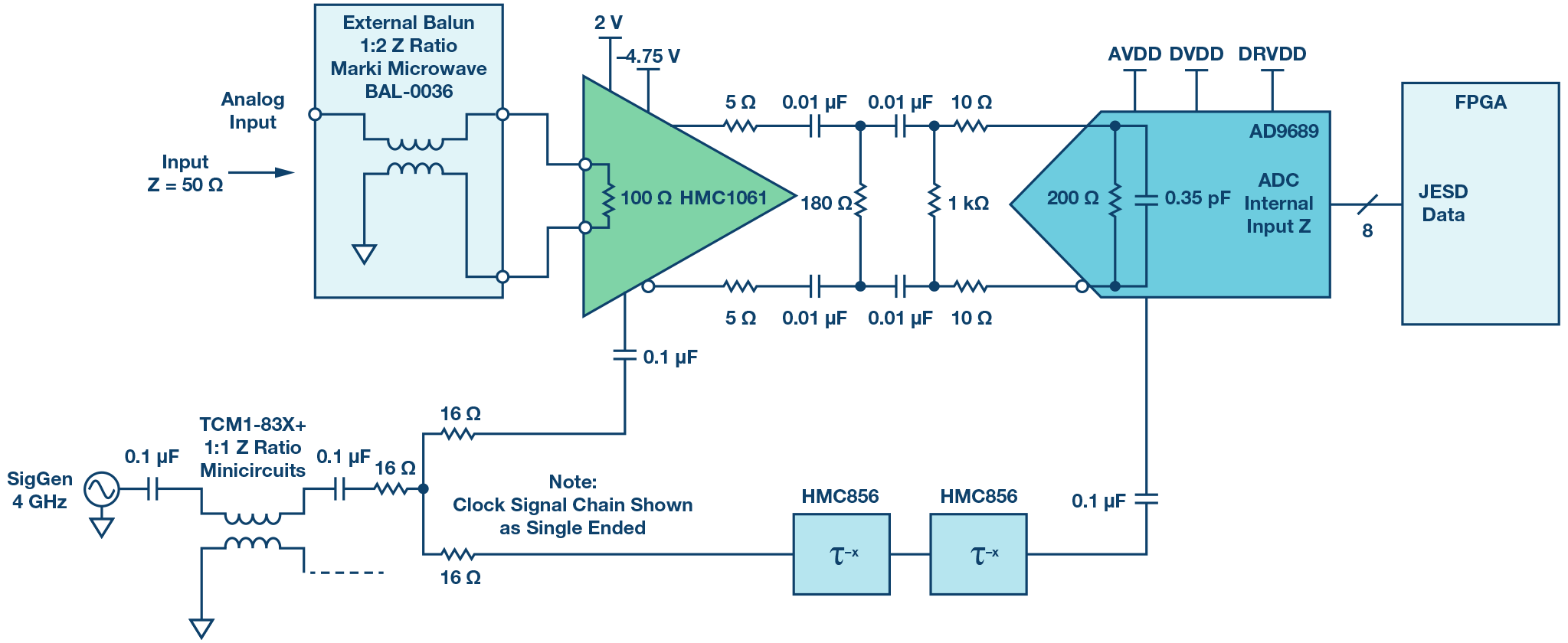

最后,最終設計相當簡單,只有幾點需要注意,如圖 5 所示。使用的0.01 μF電容為寬帶型電容,有助于在寬頻率范圍內保持阻抗平坦。典型的現成0.1 μF型電容無法提供平坦的阻抗響應,并且可能會在通帶平坦度響應中引起更多的紋波。THA 輸出端和 ADC 輸入端的 5 Ω 和 10 Ω 串聯電阻有助于降低 THA 輸出端的峰值,并最大限度地減少 ADC 自身內部采樣電容網絡的任何殘余電荷注入引起的失真。但是,需要明智地選擇這些值,否則會增加信號衰減并迫使THA更努力地驅動,或者設計可能無法利用ADC的整個滿量程。

最后,讓我們討論差分流端接。在將兩個或多個轉換器連接在一起時,這些至關重要。通常,輕型負載(在本例中為輸入端為1 kΩ)有助于實現線性度并保持混響頻率。分體處的 120 Ω并聯負載的作用相同,但會產生更真實的負載,在本例中為 50 Ω,這正是 THA 希望看到并優化的。

圖5.THA 和 ADC 前端網絡和信號鏈。

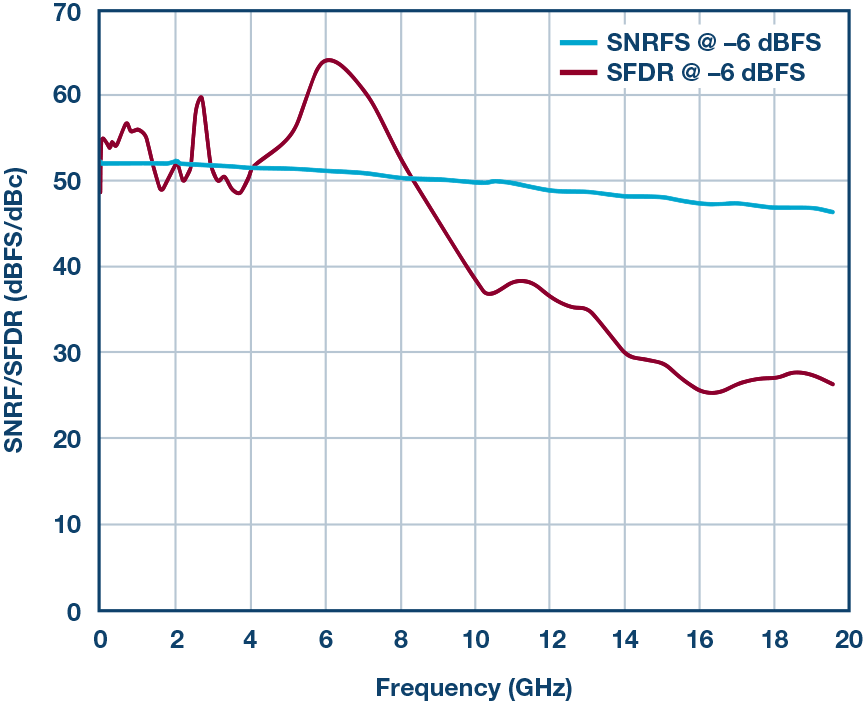

現在來看結果!查看圖6中的信噪比或SNR,可以看出,在15 GHz的范圍內可以實現8位ENOB(有效位數)。考慮到您可能已經為具有相同性能的 120 GHz 示波器支付了 13 美元,這非常好。集成帶寬(即噪聲)和抖動限制開始成為當頻率通過L、S、C和X波段時性能下降的一個重要因素。

還應該注意的是,為了保持THA和ADC之間的電平恒定,ADC的滿量程輸入通過SPI寄存器在內部更改為1.0 V p-p。這有助于將THA保持在線性區域內,因為它的最大輸出為1.0 V p-p差分。

圖6.SNRFS/SFDR 性能結果在 –6 dBFS 下。

還顯示了線性度結果或SFRD。在這里,線性度在8 GHz時高于50 dBc,在10 GHz時達到40 dB。此處的設計采用AD9689模擬輸入緩沖電流設置功能,通過SPI控制寄存器進行優化,以便在如此寬的頻率范圍內達到最佳線性度。

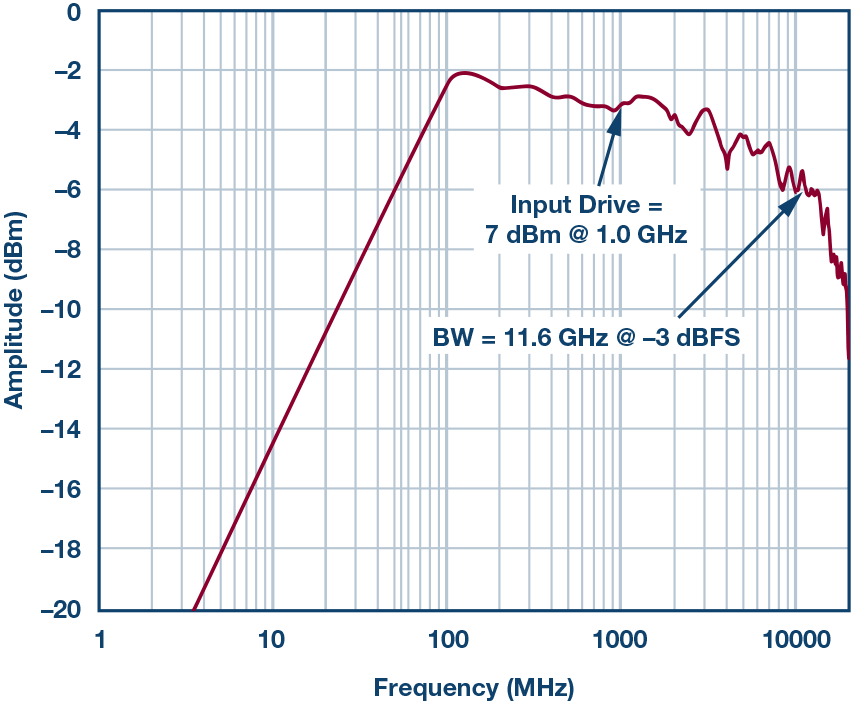

圖7顯示了通帶平坦度,證明通過在RF ADC前面增加一個THA可以實現10 GHz帶寬,從而完全擴展AD9689的模擬帶寬。

圖7.THA 和 ADC 網絡和信號鏈 — 帶寬結果。

總結

對于那些需要在多GHz模擬帶寬上獲得最佳性能的應用,使用THA幾乎是必要的,至少在今天是這樣!RF ADC正在迅速迎頭趕上。從理論上講,GSPS轉換器在采樣更寬的帶寬以覆蓋多個目標頻段時易于使用。這會在前端RF條上重溫一個混音下級或其多個。但是,在這些更高范圍內實現帶寬可能會帶來設計挑戰并保持性能。

在系統中使用 THA 時,請確保采樣點在 THA 和 ADC 之間的位置得到優化。使用本文中所述的延遲映射過程將產生總體上的最佳性能結果。了解該程序很乏味,但至關重要。最后,請記住,匹配前端實際上意味著在每個應用程序給定一組性能需求的情況下實現最佳性能。樂高效應——簡單地將50個Ω阻抗塊連接在一起——在X波段頻率采樣時可能不是最佳方法。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13583瀏覽量

213368 -

轉換器

+關注

關注

27文章

8694瀏覽量

147091 -

RF

+關注

關注

65文章

3050瀏覽量

166965

發布評論請先 登錄

相關推薦

利用采樣保持放大器和RF ADC從根本上擴展帶寬以突破X波段頻率

使用采樣保持放大器和RF ADC從根本上擴展帶寬以壓低X波段頻率

使用采樣保持放大器和RF ADC從根本上擴展帶寬以壓低X波段頻率

評論