移動、汽車和物聯網 (IoT) 電氣和電子系統的加速部署,加上上市時間窗口的縮短,導致需要對支持它們的 IC 進行更快速、更低成本的測試。

要實現這些目標,需要具有更大靈活性和模塊化的自動化IC測試平臺,以及減少元件數量,以節省成本和空間。

為了滿足這些要求,設計人員正在從經典的模擬控制器轉向易于編程的數字控制環路,以實現環路穩定性。雖然數字控制器去掉了電阻、電容和開關,但模數轉換器(ADC)和數模轉換器(DAC)的分辨率和精度會極大地影響數字控制環路架構的整體精度。

本文簡要討論數字控制環路的優點。然后討論實現過程中的挑戰,例如時序和轉換器噪聲誤差源,以及通過仔細關注ADC的吞吐速率和信噪比(SNR)以及DAC的建立時間和噪聲頻譜密度規格來管理這些挑戰。

然后介紹ADI公司的AD4630-24、24位逐次逼近寄存器(SAR)ADC和ADI公司的AD5791電壓輸出DAC。這兩種設備結合使用時,可以構成用于精密儀器測量的高精度和靈活的數字控制器的基礎。

數字控制回路

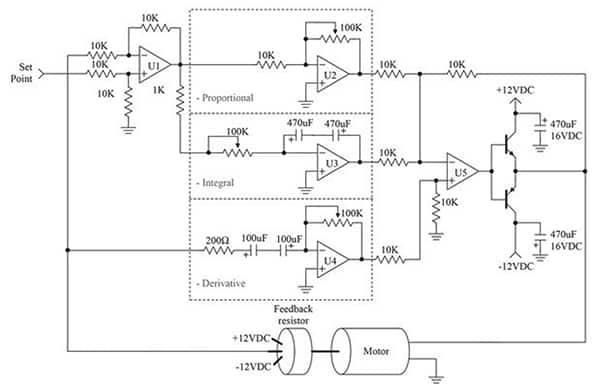

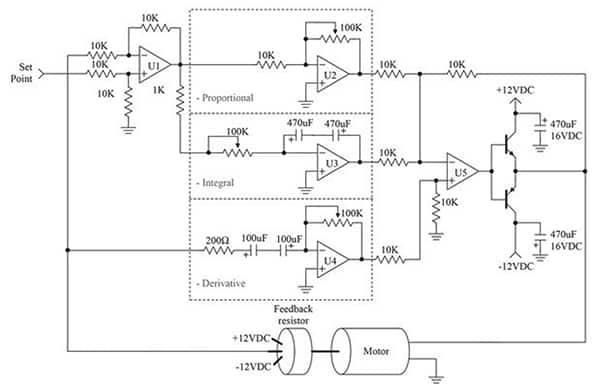

在工程系統中,控制器可確保令人滿意的瞬態和穩態行為。模擬控制器實現具有模擬輸入和輸出,其中信號沿連續時間間隔存在,值在連續幅度范圍內。傳感器測量受控變量并將其行為與參考信號進行比較。測試控制操作使用誤差信號,即參考值與實際值之間的差異(圖 1)。

圖 1:模擬系統電機控制器使用各種放大器 (U1-U5) 以及一組預定的電阻和電容值。(圖片來源:Quora)

圖 1:模擬系統電機控制器使用各種放大器 (U1-U5) 以及一組預定的電阻和電容值。(圖片來源:Quora)

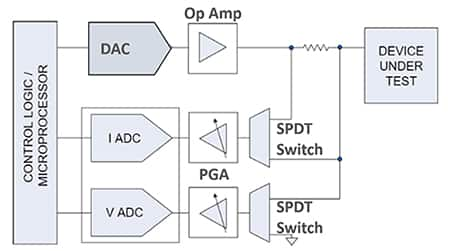

直觀地說,具有連續系統模擬輸出的控制器似乎優于具有采樣輸出值的數字控制器(圖 2)。

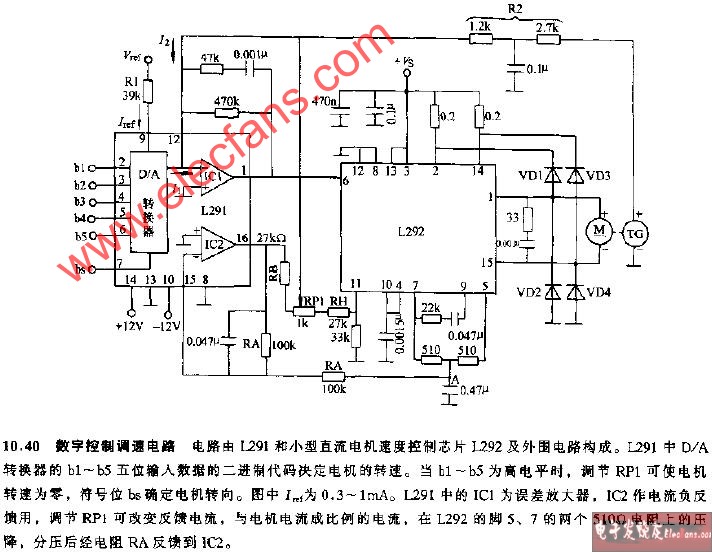

圖 2:采用數字控制器配置的測量系統,帶有一個 DAC、兩個 ADC、模擬放大器和開關。(圖片來源:邦妮·貝克)

圖 2:采用數字控制器配置的測量系統,帶有一個 DAC、兩個 ADC、模擬放大器和開關。(圖片來源:邦妮·貝克)

邏輯將指向模擬控制器中的控制變量或輸出,這些變量或輸出不斷變化,以實現比數字結構中周期性變化的測量更好的控制。

此扣除是有效的。假設所有其他數字和模擬控制因素相同,則模擬控制優于數字控制。那么,為什么要將經典控制器從模擬改為數字呢?這五個原因是準確性、實施錯誤、靈活性、速度和成本。

準確性: 模擬信號的數字表示形式為零和一,通常最多使用 32 位來表示單個模擬值(圖 2)。這些轉換會產生需要解決的小數字量化誤差。另一方面,模擬信號具有電源漂移和外部噪聲,會降低模擬信號的性能。這些模擬溫度和時間相關的漂移難以控制且成本高昂,而老化和溫度對數字控制器的影響可以忽略不計。

實現錯誤: 數字控制器中的實現誤差可以忽略不計。這是因為控制信號的數字處理使用存儲的數值進行加法和乘法功能,而不是模擬元件的溫度漂移誤差,以及電阻器、電容器和電感器不可靠的開箱即用精度。此外,數字控制器的時間常數設置很容易在軟件中修改,而模擬控制器具有固定數量的可用時間常數。數字控制器的更改可以即時進行,使儀器能夠適應各種負載條件并提高整體測試效率。

靈活性: 模擬控制器存在靈活性方面的困難。硬件設計完成后,對印刷電路板的修改既耗時又昂貴。使用數字控制器,修改很容易實現 - 直至完全代碼替換。此外,對數字控制器的形狀或結構沒有限制,并且可以輕松實現涉及額外算術選項的復雜控制器結構。

速度: 計算性能繼續呈指數級增長。這種增加使得以非常高的速率采樣和管理信號成為可能,并且樣本之間的間隔越來越小。現代數字控制器的性能相當于連續模擬監控系統。

成本: 由于半導體制造的進步,IC的成本持續下降,使數字控制器更加經濟,即使對于小型低成本應用也是如此。

數字控制器的模擬實現挑戰

ADC和DAC位于模擬域和數字域的邊界,兩者都具有不同的電氣特性。訣竅是發現兩個設備之間的互補規格,以便它們可以在同一系統中共存。從系統吞吐量的角度來看,確定整體傳輸的速度和噪聲特性至關重要。

ADC 和 DAC 時序估計

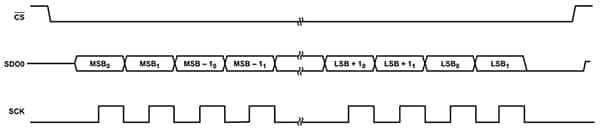

ADC的吞吐速率通常有一個明確的定義,單位為每秒兆采樣數(MSPS)或每秒千采樣數(kSPS)。以頻率赫茲為單位的吞吐時間是以秒為單位的吞吐速率的倒數。吞吐時間是轉換器采樣、采集、數字化和準備后續轉換所需的時間。此時間也是連續轉換應用程序中的最小轉換時間。規格單位定義完整輸出字的轉換速度。例如,如果 ADC 具有數字串行輸出引腳,而轉換器具有 24 位引腳,則模擬輸入的整個 24 位轉換在另一個轉換開始之前傳輸(圖 3)。

圖 3:ADC 時序圖顯示了轉換器接受的數字代碼數量。(圖片來源:ADI公司)

具有2 MSPS規格的ADC每500納秒(ns)輸出一個完整的字。遺憾的是,這個單一的轉換樣本并不能描繪出模擬輸入信號的完整畫面。根據奈奎斯特定理,ADC必須產生至少兩個樣本才能產生模擬輸入信號。至少,為了滿足奈奎斯特定理,這個過程現在需要兩倍500 ns或1微秒(μs)的時間。這是創建模擬信號骨架的最小樣本數。最好使用四個或八個樣本以數字方式重新創建模擬信號。

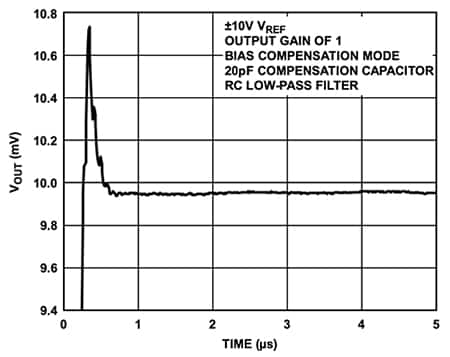

轉到DAC規格,DAC的輸出電壓建立時間是輸出電壓在指定電壓變化下建立到指定水平所需的時間(圖4)。

圖 4:DAC 表現出建立時間誤差,該誤差捕獲達到最終值所需的時間。最壞情況下的建立時間誤差通常發生在輸出在 100 000 和 011 111 ...輸入代碼。(圖片來源:ADI公司)

以圖4為例,DAC在最差情況下建立時間小于1 μs。該值的數學倒數等于1 MHz,也等于1 MSPS。為了符合奈奎斯特標準,DAC必須產生兩個輸出樣本,需要2倍1 μs或2 μs的時間,與ADC一樣,樣本越多越好。

現在,關于奈奎斯特定理的最后一個故事。根據該定理,信號的再現至少需要兩個樣本。在這種情況下,定理僅標識信號頻率。這就是定理需要應用常識的地方。樣本量越大,收集時間越長,但它們會產生更可靠的信號重建。

ADC 和 DAC 頻率噪聲估計

噪聲的定義需要了解實際轉換器分辨率和均方根(rms)噪聲。轉換器分辨率(如24位、20位或1 ppm)的聲明描述了ADC或DAC輸出或輸入的數量。例如,24位ADC每次轉換產生24個輸出代碼,20位DAC為一次轉換收集20個數字輸入值。但是有了這些值,轉換器的頻率精度就沒有定義。

轉換器精度的定義取決于SNR或rms噪聲等噪聲規格。整個輸出頻率范圍內的噪聲ADC規格是典型的分貝(dB)SNR值。信噪比使用公式1計算:

等式 1

ADC或DAC數據手冊定義了器件的輸出范圍。噪聲是轉換器頻帶上的累積和方根(RSS)。

均方根分辨率使用公式2計算:

等式2

對于SNR為105.7 dB的ADC,均方根分辨率為17.6位,這意味著轉換器可以可靠地處理該水平的精度。DAC噪聲規格通常為頻譜噪聲密度值,因此可以輕松快速轉換DAC的實際均方根分辨率。DAC的輸出噪聲使用公式3計算:

等式3

例如,如果 20 位 DAC 的頻譜噪聲密度為 7.5 納伏/√Hz (nV/√Hz),帶寬為 500 kHz,則 DAC噪聲等于 5.3 μV (有效值)。根據該值,DAC在5V輸出范圍內的均方根分辨率等于19.8位。

數字控制器和精密儀器儀表

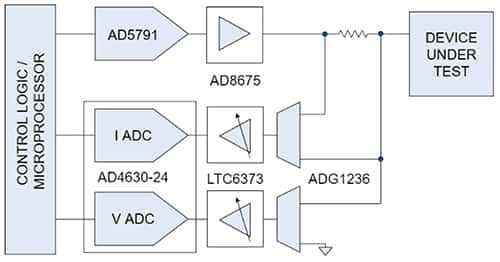

用于移動、汽車和物聯網測試電路的數字控制器器件測試系統示例包含 9 個器件和一個分立電阻器(圖 5)。本電路中的器件包括微處理器、ADC、DAC、驅動器放大器、增益可調儀表放大器和ADI公司的ADG1236SPDT開關。微處理器管理ADC和DAC之間的數字接口和數據,例如ADI公司的AD4630-24和AD5791。

圖 5:數字控制器使用微處理器來管理進出 ADC 和 DAC 的數據。DAC需要一個增益輸出驅動放大器,ADC需要一個放大器系統來衰減信號。(圖片來源:ADI公司)

AD4630-24是一款2 MSPS、24位±0.9 ppm積分非線性(INL)ADC,SNR為105.7 dB,產生17.6位(rms)。該ADC的轉換速度為2 MSPS,至少需要4個輸出采樣才能產生模擬信號。INL表示轉換器的直流精度。

AD5791是一款20位±1 LSB、INL 1 μs建立時間7.5 nV/√Hz頻譜密度DAC,最終產生19.8位(rms)。該DAC的速度為1 MSPS,需要4 μs才能準確生成模擬信號。

該系統中的轉換器還需要運算放大器(op amp)接口來管理輸出驅動和模擬增益。在圖5中,ADI公司的AD8675是一款10 MHz、2.8 nV/√Hz軌到軌輸出運算放大器。該放大器的噪聲使DAC系統的位降至19.1 (rms)。但是,10 MHz放大器帶寬超過了DAC的帶寬。

ADI公司的LTC6373是全差分、可編程增益儀表放大器,可提供增益和一定程度的隔離。如果DAC級實現4 V/V的增益,則LTC6373的增益選項之一是0.25 V/V,這使信號恢復到原始值。LTC6373 的數字增益電平的靈活性有助于實現數字控制器的動態特性。

結論

移動、汽車和物聯網電子測試系統快速發展的設計要求 的 上市 時間 壓力 和 成本 已經 從 傳統 模擬 控制器 轉變 到 數字 控制 環路。這些環路提供更高的精度和靈活性以及更低的成本,但需要仔細注意ADC和DAC的選擇。

如圖所示,通過將ADI公司的24位SAR ADCAD4630-24與ADI公司的20位電壓輸出DAC5791配對,可以創建用于精密儀器儀表測量的高精度、靈活的數字控制器。

審核編輯 黃昊宇

-

數字控制

+關注

關注

2文章

181瀏覽量

25808 -

模數轉換器

+關注

關注

26文章

3200瀏覽量

126810

發布評論請先 登錄

相關推薦

開關電源的數字控制實現方案

PWM類似于模擬控制器的數字控制類型

數字控制真的會取代模擬控制,而成為PFC中的主流控制方式嗎?

開關電源的數字控制實現方案

用數字控制提高無橋PFC性能

模擬控制式和數字控制式VGA(一)可變增益放大器

模擬控制式和數字控制式VGA(二):數字控制式VGA

如何量身定制數字控制回路的模擬元器件

如何定制數字控制回路的模擬組件

如何定制數字控制回路的模擬組件

評論