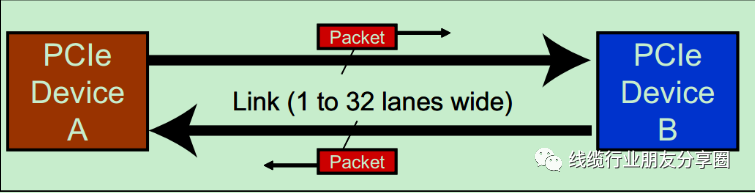

隨著現代處理器技術的發展,在互連領域中,使用高速差分總線替代并行總線是大勢所趨。與單端并行信號相比,高速差分信號可以使用更高的時鐘頻率,從而使用更少的信號線,完成之前需要許多單端并行數據信號才能達到的總線帶寬。PCI總線使用并行總線結構,在同一條總線上的所有外部設備共享總線帶寬,而PCIe總線使用了高速差分總線,并采用端到端的連接方式,因此在每一條PCIe鏈路中只能連接兩個設備。

這使得PCIe與PCI總線采用的拓撲結構有所不同。PCIe總線除了在連接方式上與PCI總線不同之外,還使用了一些在網絡通信中使用的技術,如支持多種數據路由方式,基于多通路的數據傳遞方式,和基于報文的數據傳送方式,并充分考慮了在數據傳送中出現服務質量QoS (Quality of Service)問題。

如今PCIe 7.0 時代已經到來(PCIe 7.0 標準已在修訂?全面普及可能要到2028年),實際商用主流PCIe4.0 ,其發展使服務器硬件間信息交互速度再次躍升,但隨之而來的是不可忽視的信號衰減問題,今天我們科普下PCIe簡介及引腳定義。

PCIe發展歷程

2001年,非營利組織PCI-SIG召集了英特爾、AMD、博通、IBM、微軟等廠商提出了PCIe(Peripheral Component Interconnect Express)新總線標準,此舉是為取代舊的PCI,PCI-X和AGP總線標準。

2003年-2010年:PCIe 1.0 - PCIe 3.0

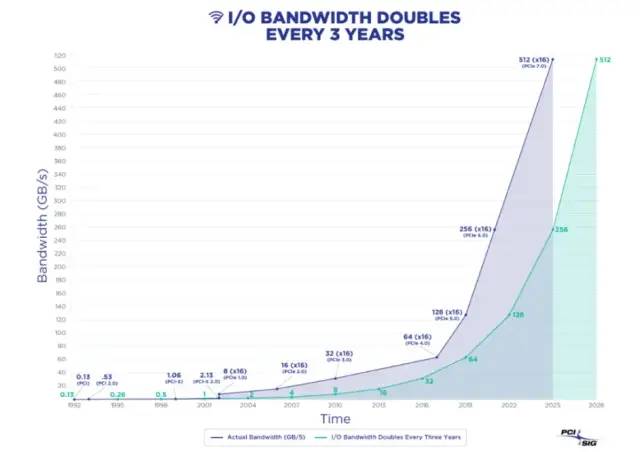

PCIe 技術始于 2003 年,PCIe 1.0數據速率為 2.5GT/s,PCIe 2.0 規范在 2006 年將數據速率翻了一番,達到 5.0 GT/s。前兩代 PCIe 技術使用 8b/10b 編碼,產生了 25% 的編碼開銷。

2010年,PCIe 3.0 將數據速率提高到了 8.0 GT/s ,并采用了新的 128b/130b 編碼機制,使每個引腳的帶寬比 PCIe 2.0 翻了一番。新的編碼機制通過采用三個隨機位翻轉檢測的故障模型確保了高可靠性,并具有多種創新方法來執行數據包的物理層幀,同時保留從上層發送的數據包格式。 PCIe 3.0規范還加入了一些增強信號指令,以及對數據完整性的優化,包括發送器和接收器以及拓撲結構等,再加上重新優化的PLL、數據通道等。

此外,PCIe 3.0標準的更新版本PCIe 3.1在2014年11月發布,加入了包括電源管理、性能優化和功能拓展等多項改變,當然本質的數據傳輸能力沒有變化。2010年推出PCIE3.0,32(x16),可以看到之后幾年一直處于PCIE3.0時代。直到2017年才推出PCIE4.0,64(x16),2017年10月:16.0 GT/s的PCIe 4.0 依照PCIe 1.0到PCIe 3.0的更新節奏來看,相對于2010年發布的PCIe 3.0,PCIe 4.0規范應該要在2014或2015年發布,但實際上,PCI-SIG直到2017年中才發布PCIe 4.0,較預期晚2、3年,這連帶也推遲了應用的時間。

PCIe 4.0花費了7年時間將數據速率從 8.0 GT/s 翻倍到 16.0 GT/s (每條通道大約 2GB/s,或總共 64GB/s)。PCIe 4.0 保留了相同的 128b/130b 編碼方案,PCIe 標準通過軟件和機械接口保持與舊規范和新規范的向后和向前兼容性。也就是說,PCIe 3.0卡可以在支持PCIe 4.0的主板上工作,PCIe 4.0卡也可以在PCIe 3.0主板上工作,但受限于PCIe 3.0接口的性能。

2019年推出PCIE5.0標準,2019 年 5 月:32.0 GT/s 的 PCIe 5.0 過去幾年,計算領域發生了重大變化,云計算、邊緣計算以及人工智能、機器學習和分析等應用引發了對更快的數據處理和移動的需求。隨著計算和內存容量呈指數級增長,我們需要以更快的節奏維持 I/O 帶寬翻倍,以跟上新興應用程序的性能。例如,400 Gb(或雙 200 Gb)網絡需要 32.0 GT/s 的 x16 PCIe 來維持帶寬。

這就要求在PCIe 4.0架構之后不到兩年的時間里發布一個完全向后兼容的PCIe 5.0——這對于一個標準來說是一個重大的成就,去年10月英特爾發布12代酷睿處理器,支持PCIe5.0標準,相信PCIE5.0消費級產品也在不久后面市。AMD搶先NVIDIA 首發支持PCIe 5.0,從 PCIe 4.0 到 PCIe 5.0 規范的演變主要是速度升級。128b/130b 編碼是將帶寬擴展到更高數據速率的協議支持,在PCIe 3.0和PCIe 4.0規范中已經內置了這種編碼。

通道損耗擴展到 36 dB,同時對連接器進行了改進,以最大限度地減少頻率范圍增加所帶來的損耗。PCIe 5.0 架構的增強功能之一是對備用協議的內置支持。隨著 PCIe 技術發展成為帶寬最高、能效最高和部署最廣泛的接口,某些用途需要額外的協議,例如,某些加速器和智能網卡可以緩存系統內存并將其內存映射到系統內存空間,以便在PCIe協議之外進行高效的數據交換。

同樣,系統內存正在遷移到 PCIe PHY,因為它提供了高能效的高帶寬和低延遲解決方案。PCI-SIG 預計 PCIe 4.0 和 PCIe 5.0 將在一段時間內共存,PCIe 5.0 用于對吞吐量要求高的高性能需求,例如用于 AI 工作負載和網絡應用程序的 GPU。因此,PCIe 5.0 將主要用于數據中心、網絡和高性能計算 (HPC) 企業環境,而不那么密集的應用(如臺式機應用)將適用于 PCIe 4.0。

PCIe 6.0正式發布!有史以來變化最大一次:x16帶寬增至256GB/s;2022年1月11日,PCI-SIG正式發布了PCIe 6.0最終版本1.0,從技術上來說,PCIe 6.0是PCIe問世近20年來,變化最大的一次。 PCIe 6.0 規范目標要求 根據PCI-SIG的介紹,PCIe 6.0主要有三大變化:數據傳輸速率從32GT/s翻倍至64GT/s;編碼方式從NRZ 信令模式轉向PAM4信令模式;從傳輸可變大小TLP到固定大小FLIT.

新技術提供市場導向,市場需求反向推動新技術的發展。面對人工智能、物聯網、云端數據存儲以及最近火熱的汽車等領域,交互時代需要更快、更高效的接口傳輸數據,所以我們可以看到每一代PCIE推出都帶來翻倍的帶寬。新技術產品的推出,都優先應用于高性能計算服務器、云端數據存儲等大型服務器領域。

消費級市場推出PCIE新技術產品,需周邊配套產品支持以及成本等方面考慮,所以消費領域的應用往往要慢兩至三年,在實際應用方面,剛剛發布不久的PCIe 6.0目前自然還尚無具體進展,現在主流的應用還在PCIe 3.0和PCIe 4.0,不過PCIe 5.0已經進入初步的推廣期,自2021年底開始,便開始有廠商推出支持PCIe 5.0的高速網卡與SSD產品,并且一些新的GPU、CPU開始采用PCIe 5.0了。

這也讓當前的PCIe應用環境形成了3.0、4.0、5.0、6.0“四代同堂”的奇特現象,并且仍將持續一段時間。 整體而言,新一代PCIe 5.0與PCIe 6.0已經崛起,并陸續投入應用,PCIe 6.0帶來的新特性,包括64GT/s的數據速率、PAM4編碼方式、具有吞吐量和延遲優勢的 FLIT等等,必然會更好地推動行業發展。

審核編輯 :李倩

-

PCI

+關注

關注

4文章

663瀏覽量

130251 -

總線

+關注

關注

10文章

2878瀏覽量

88052 -

PCIe

+關注

關注

15文章

1234瀏覽量

82585 -

引腳

+關注

關注

16文章

1193瀏覽量

50412 -

并行總線

+關注

關注

0文章

30瀏覽量

13462

原文標題:PCIE發展史科普篇

文章出處:【微信號:線纜行業朋友分享圈,微信公眾號:線纜行業朋友分享圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe延遲對系統性能的影響

pcie帶寬對計算性能的影響

PCIe與NVMe存儲的關系

PCIe 4.0與PCIe 3.0的性能對比

DDR4接口引腳定義及功能

PCIe 5.0 SerDes 測試

pcie4.0和pcie3.0接口兼容嗎

MINI PCIE連接器的接口基本定義簡述

常見芯片引腳的定義及其功能

PCIe簡介及引腳定義

PCIe簡介及引腳定義

評論