作者:Tom Bosia, Russell Martin, Marc Goldfarb, Dragoslav Culum, Ben Walker, and EdBalboni

無線基站曾經被包含在大型氣候控制空間中,但現在,它們可以安裝在任何地方。隨著無線網絡服務提供商試圖實現覆蓋無處不在,基站組件供應商面臨著以更小的封裝提供更多功能的壓力。

ADI公司的一對集成電路(IC)通過重新定義接收器前端混頻器的含義來提供解決方案。從本質上講,IC將許多一旦添加到接收器混頻器的元件(如本振(LO)和中頻(IF)放大器)集成到混頻器IC本身中。它們能夠大幅縮小蜂窩基站,同時還提供軟件定義無線電 (SDR) 靈活性來處理許多不同的無線標準。

所討論的IC是ADRF6612和ADRF6614型號,均設計用于700 MHz至3000 MHz的RF范圍、200 MHz至2700 MHz的LO范圍以及40 MHz至500 MHz的IF范圍。它們采用低側或高側 LO 注入,包括一個板載鎖相環 (PLL) 和多個低噪聲壓控振蕩器 (VCO),全部封裝在 7 mm × 7 mm 48 引腳 LFCSP 外殼中。這種集成度和組件密度通過多樣性和可編程性得到增強,以支持現代微蜂窩所需的小體積中的多種不同無線標準。

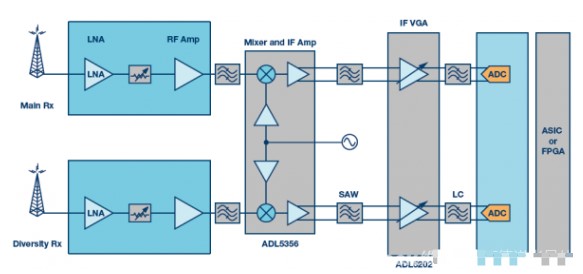

為了了解這些高度集成的混頻器IC節省的空間,記住2010年左右蜂窩基站接收器的前端可能會有所幫助,如圖1所示。雙混頻器架構覆蓋了大約 1 GHz 的帶寬,需要多個組件來處理當時 800 MHz 至 1900 MHz 的蜂窩頻率范圍。 頻率合成由單獨的PLL和窄帶VCO模塊提供,該模塊需要獨特的PLL環路濾波器才能獲得最佳性能。每個感興趣的頻段都使用了專用的VCO模塊,增加了基站內所需的電路板面積。

圖1.框圖表示2010年左右的典型蜂窩無線基站。

此外,這些分立元件通過低阻抗傳輸線互連,這會導致一些信號損失。因此,需要大電流將VCO輸出驅動到足夠的水平,以使混頻器在信號阻塞條件下產生低相位噪聲和噪聲系數。

集成VCO的接收器IC并不新鮮。但是,實現多運營商、全球移動通信系統(MC-GSM)無線網絡所需的寬帶寬和低相位噪聲水平一直是一個挑戰。GSM的通道復用方案要求接收LO具有極低的相位噪聲,特別是在800 kHz的備用通道偏移頻率下,如圖2所示。如果這些交替通道上的相位噪聲過大與相同800 kHz偏移的無用信號混合,則可能導致相位噪聲轉換為IF輸出,從而降低系統靈敏度。

圖2.信道復用方案要求在GSM無線系統中使用具有低相位噪聲的寬帶寬VCO,以避免由于阻塞而導致性能下降。

低VCO相位噪聲通常通過高質量因數(高Q)諧振電路和窄帶設計來實現。分頻還可以降低噪聲。通過在接收器LO頻率的整數倍下工作VCO,隨后的分頻可將相位噪聲降低6 dB/倍頻程,如圖3所示。1800 MHz至1900 MHz頻段GSM的相位噪聲要求極其困難,大約是800 MHz至900 MHz頻段的兩倍。

圖3.這種VCO電路配置可以實現倍頻程帶寬。

除了低相位噪聲外,現代基站接收器設計還必須支持目前無線通信網絡中使用的許多調制方案。除GSM外,其他調制方案還包括寬帶碼分多址(WCDMA)和長期演進(LTE)系統。接收器設計通常由許多不同的VCO組成,這些VCO具有中等相位噪聲性能水平,以便將它們組合在一起以覆蓋基站內的倍頻程帶寬。

一旦將多個VCO配置為為最高工作頻率產生倍頻程帶寬,就可以通過二進制分頻實現較低的LO頻率。這種方法用于ADRF6612接收器混頻器,其中VCO基頻范圍為2.7 GHz至5.6 GHz,兩級分頻通過從1分頻到32來實現200 GHz至2700 MHz的LO頻率。對于同時包含MC-GSM的應用,ADRF6614接收器混頻器包括兩個額外的高性能VCO內核,可提供1800 MHz至1900 MHz GSM頻段所需的LO頻率。

由于現代無線微蜂窩可能不具備氣候控制環境的優勢,因此這些接收器IC等組件必須在寬極端溫度下提供一致、可靠的性能。為了在寬工作溫度范圍內實現指定性能,ADRF6612和ADRF6614 IC中的PLL和VCO采用多種校準技術。

對于低噪聲的寬帶寬,每個VCO內核都采用一個8位電容數模轉換器(CDAC),該轉換器可自動為給定LO頻率選擇正確的頻段(128個中的1個)。VCO儲罐振幅的任何變化都由系統仔細監控,并使用自動電平控制(ALC)系統調整振幅以獲得最佳輸出振幅。每當重新編程工作頻率時,每個IC都會執行校準序列。這可確保所選頻段將VCO調諧變容二極管的調諧電壓集中在最佳范圍內,以保持頻率合成器在所需的工作溫度范圍內鎖定。

每個ADRF6612和ADRF6614 IC中的四個VCO內核經過定位,以確保其工作范圍為不斷變化的環境條件和器件制造容差提供合適的重疊。由于環境和過程的變化,內核通常會沿同一方向移動頻率,因此頻率合成器內置了足夠的重疊,以始終實現鎖定條件。

一旦確定了校準解決方案,頻率應無限期地保持,調諧電壓范圍支持所需的保持范圍。在時分雙工(TDD)系統中,基站可能會在時隙間改變頻率,該工作時間可以以微秒為單位進行測量。在頻分雙工 (FDD) 系統中,可能需要在單個頻率上保持鎖定多年。

在ADRF6612和ADRF6614 IC系統工作期間的任何時候都不允許停機。因此,在145°C的溫度范圍內,VCO的變容二極管調諧電壓范圍和頻率調諧靈敏度(kV)涵蓋了溫度和元件老化效應的變化。每個IC持續監控器件溫度,并根據需要調整VCO偏置。

ADRF6612和ADRF6614 IC采用獨特的方法,可最大限度降低雜散信號產物對接收器靈敏度的影響。將頻率合成器的整數模式與緊密環路濾波器結合使用,可產生小于?100 dBc的低基準雜散產物。最小雜散信號對于調制方案(如MC-GSM)至關重要。對于LTE和其他調制方案,或需要精細頻率階躍的地方,頻率合成器可以在小數N分頻模式下工作。參考路徑包含一個 13 位分頻器,整數和小數路徑均包含 16 位分頻器,以提高靈活性。

對于需要共置、相位跟蹤接收通道的應用,例如在多輸入多輸出(MIMO)系統中,多個ADRF6612和ADRF6614 IC可以菊花鏈方式級聯,以允許一個單元充當主頻率合成器,分別通過其外部LO輸出和輸入端口為額外的從接收器供電。通過這種方式,可以將額外的LO分配放大器及其相關的相位噪聲增加降至最低。

為了同時支持高側和低側LO注入,每個IC的LO鏈提供靈活的信號處理,如圖4所示。使用1至32的整數分頻比,即使對于具有高中頻的700 MHz頻段,也可以進行低側注入。LO級還在200 MHz至2700 MHz的整個LO范圍內為無源混頻器內核提供方波驅動。1

圖4.該LO信號鏈用于支持無線基站接收器。

現代無線基站帶內信號的頻率接近低電平輸入信號,因此蜂窩接收器可以充當阻塞信號。在這種情況下,來自阻塞信號附近的LO放大器的相位噪聲直接混入目標信號頂部的IF輸出頻段。這會增加本底噪聲并降低接收器的信噪比(SNR),有時甚至會顯著降低。

由于阻塞信號可能很大(高功率),因此VCO相位噪聲必須極低,并且LO鏈不會降低阻塞信號失調處的本底噪聲。在這些非常高的阻塞電平下,接收器噪聲系數最終將由阻塞信號主導,并根據阻塞信號的功率電平而降低。

在接收鏈的分立實現中,可以在LO路徑中引入一些濾波,以最小化來自VCO和LO分配放大器的阻塞失調處的相位噪聲。但是,在集成前端中,必須注意避免LO鏈中的附加相位噪聲。

ADRF6612和ADRF6614 IC采用高增益LO鏈和硬限幅放大器,將LO鏈驅動至限幅。當每級進入硬限制時,LO鏈的小信號增益(否則會增加相位噪聲)會大大降低,從而最大限度地減少阻塞條件下的噪聲系數下降。

來自阻塞信號的噪聲折疊會降低接收器的輸出噪聲頻譜,從而降低接收器的噪聲系數,從而提高輸出本底噪聲系數。ADRF6612和ADRF6614接收器IC設計用于承受較大的阻塞信號,同時接收器噪聲系數的下降降至最低,如圖5所示。即使輸入阻塞電平為10 dBm,接收器的噪聲系數在與載波偏移10 MHz時也僅降低3.2 dB,即使轉換增益在該極端阻塞電平下壓縮了1 dB。

圖5.該圖比較了ADRF6614接收器IC的輸出噪聲頻譜與低電平和高電平阻塞信號(分別為左電平和右電平)。

這些接收器IC的高集成度為現代無線基站設計人員帶來了顯著的性能改進和直流功耗節省,如圖6所示。IC采用一種技術,可同時優化片內混頻器周圍的RF和IF級。2

圖6.信號鏈顯示了典型無線基站接收器中采用的組件。

該技術首次在ADRF6612中實現,在整個溫度范圍內提供超過25 dBm的最小IIP3,在整個頻率范圍內具有低功耗,在整個溫度范圍內提供29 dBm(高達2 GHz)。該技術還提供最佳的接收路徑噪聲系數性能和高轉換增益,如圖7所示。3,4

圖7.圖中顯示了ADRF6612接收器IC的實測增益、噪聲系數和輸入三階交調截點(IIP3)。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13596瀏覽量

213542 -

振蕩器

+關注

關注

28文章

3832瀏覽量

139119 -

混頻器

+關注

關注

10文章

680瀏覽量

45696

發布評論請先 登錄

相關推薦

混頻器的作用和原理

AGC中頻放大器的設計

ADL5355:1200 MHz至2500 MHz平衡混頻器、LO緩沖器、中頻放大器和RF巴倫數據表

ADL5353:2200 MHz至2700 MHz平衡混頻器、LO緩沖器、中頻放大器和RF巴倫數據表

ADL5354:2200 MHz至2700 MHz、雙平衡混頻器、LO緩沖器、中頻放大器和RF巴倫數據表

ADL5812:雙高IP3、700 MHz至2800 MHz、雙平衡、無源混頻器、中頻放大器和寬帶LO放大器產品手冊

ADL5357:500 MHz至1700 MHz平衡混頻器、LO緩沖器、中頻放大器和RF巴倫數據表

ADL5358:500 MHz至1700 MHz、雙平衡混頻器、LO緩沖器、中頻放大器和RF巴倫數據表

ADL5356:1200 MHz至2500 MHz、雙平衡混頻器、LO緩沖器、中頻放大器和RF巴倫數據表

ADL5355 1200 MHz至2500 MHz平衡混頻器、LO緩沖器、中頻放大器和RF巴倫數據表

干貨|接收器IC混合式混頻器、頻率合成器和IF放大器

接收器IC混合混頻器、合成器和中頻放大器

接收器IC混合混頻器、合成器和中頻放大器

評論