凌力爾特提供的精密 ADC 可提供高水平的性能。為了實現這種高性能,必須正確實現許多設計元素,例如低噪聲電源和基準電壓源、適當的旁路、接地層、快速建立驅動器和低抖動時鐘。即使其中一個元件執行不力,也會嚴重影響ADC的性能。

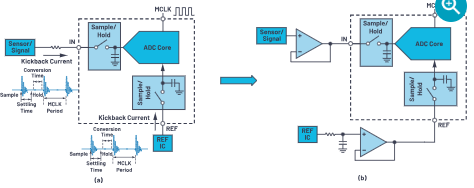

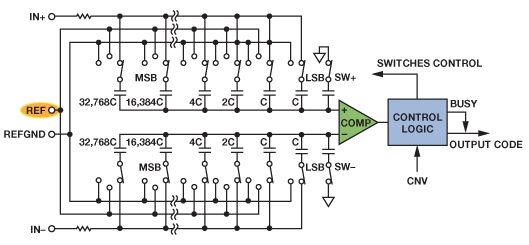

施加在ADC基準輸入端的電壓是一個特別關鍵的元件。通常,為了節省資金或電路板空間,在具有多個精密ADC的系統中,工程師會傾向于在系統中共享一個基準電壓源,而不緩沖每個基準電壓源輸入。ADC中沒有內部基準電壓緩沖器的基準電壓源引腳通常不是靜態節點。當ADC經歷轉換過程時,REF引腳上會出現一系列毛刺,必須快速建立,才能使ADC準確轉換輸入信號。如果共用基準電壓,這些毛刺會干擾相鄰ADC的轉換。即使相同類型的ADC同時轉換,也會發生這種情況。本文旨在說明當多個精密ADC共享一個公共基準電壓源時會發生什么,以說服讀者避免使用這種快捷方式。

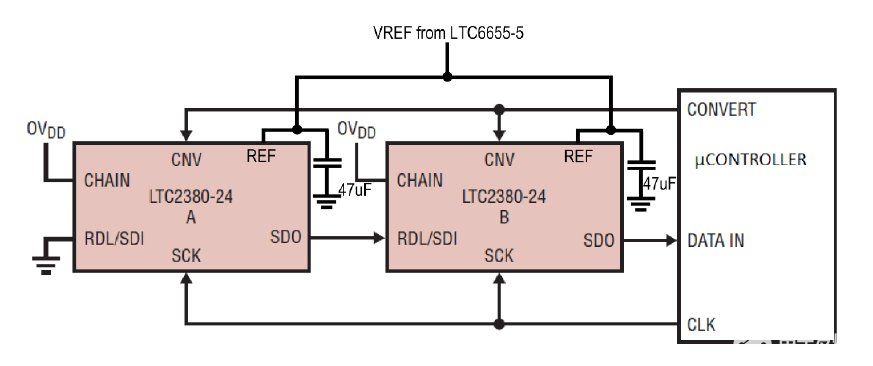

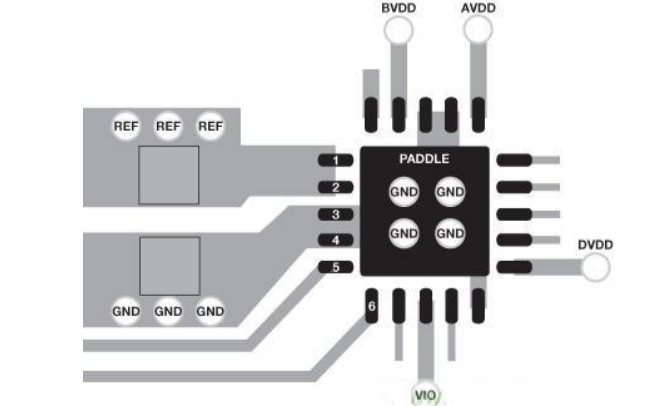

圖 1 所示電路示出了兩個 LTC2380-24 ADC 以鏈式模式連接,采用一個公共基準。LTC?2380-24 是一款低噪聲、低功率、高速 24 位逐次逼近寄存器 (SAR) ADC,具有一個集成的數字平均濾波器。LTC2380-24 具有一個 145dB 的動態范圍,并能在一個 -117dB 的典型 THD 下采樣高達 2Msps。47μF基準旁路電容放置在盡可能靠近ADC的REF引腳的位置,以最大限度地提高其效率。數據是用圖1所示電路獲取的,通過移除ADC A并將ADC B的RDL/SDI輸入接地來修改電路。一個ADC和兩個ADC情況的時序相同,以最大程度地減少時序變化可能導致的任何差異。

圖1.兩個 LTC2380-24 ADC 共用一個公共基準

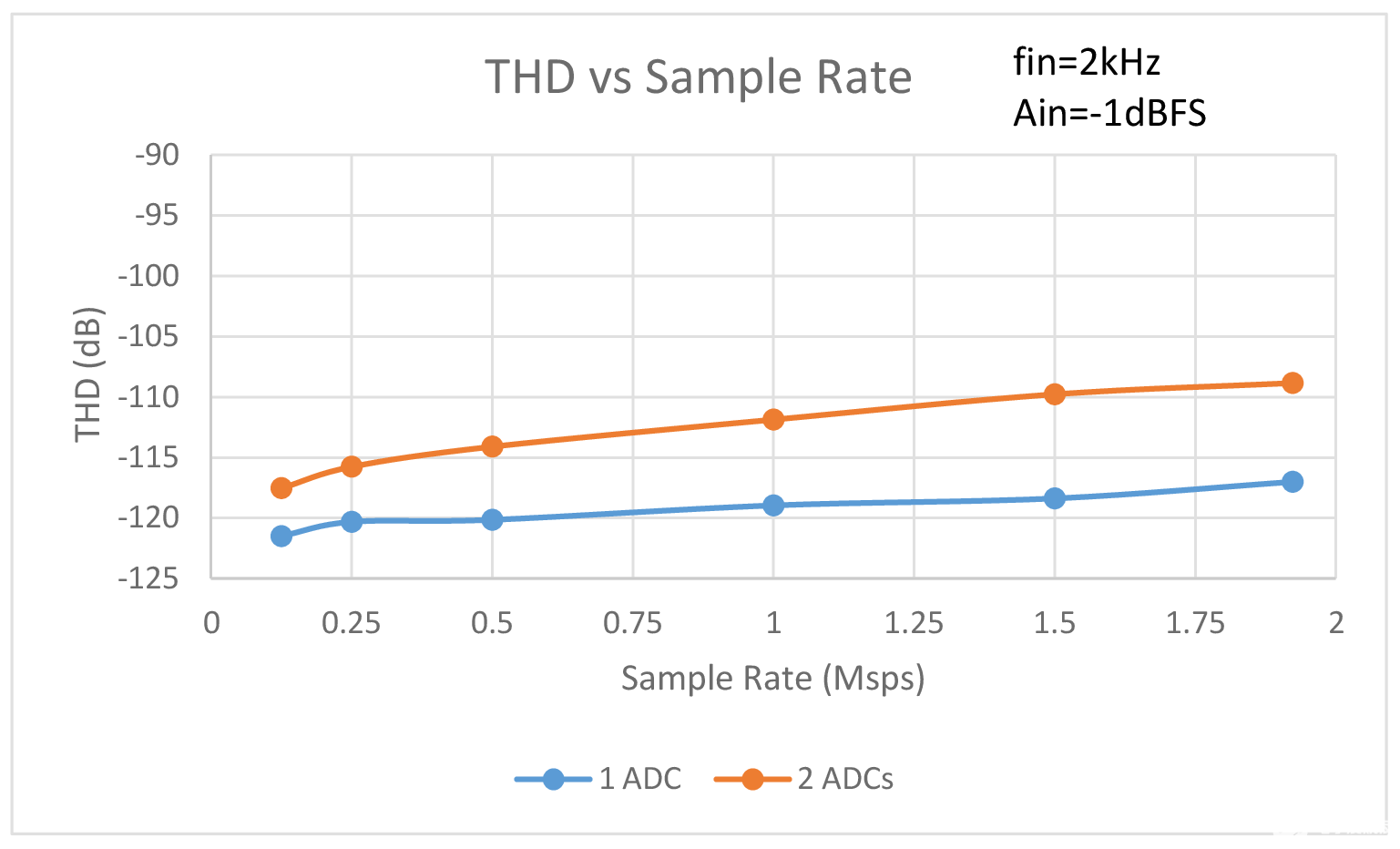

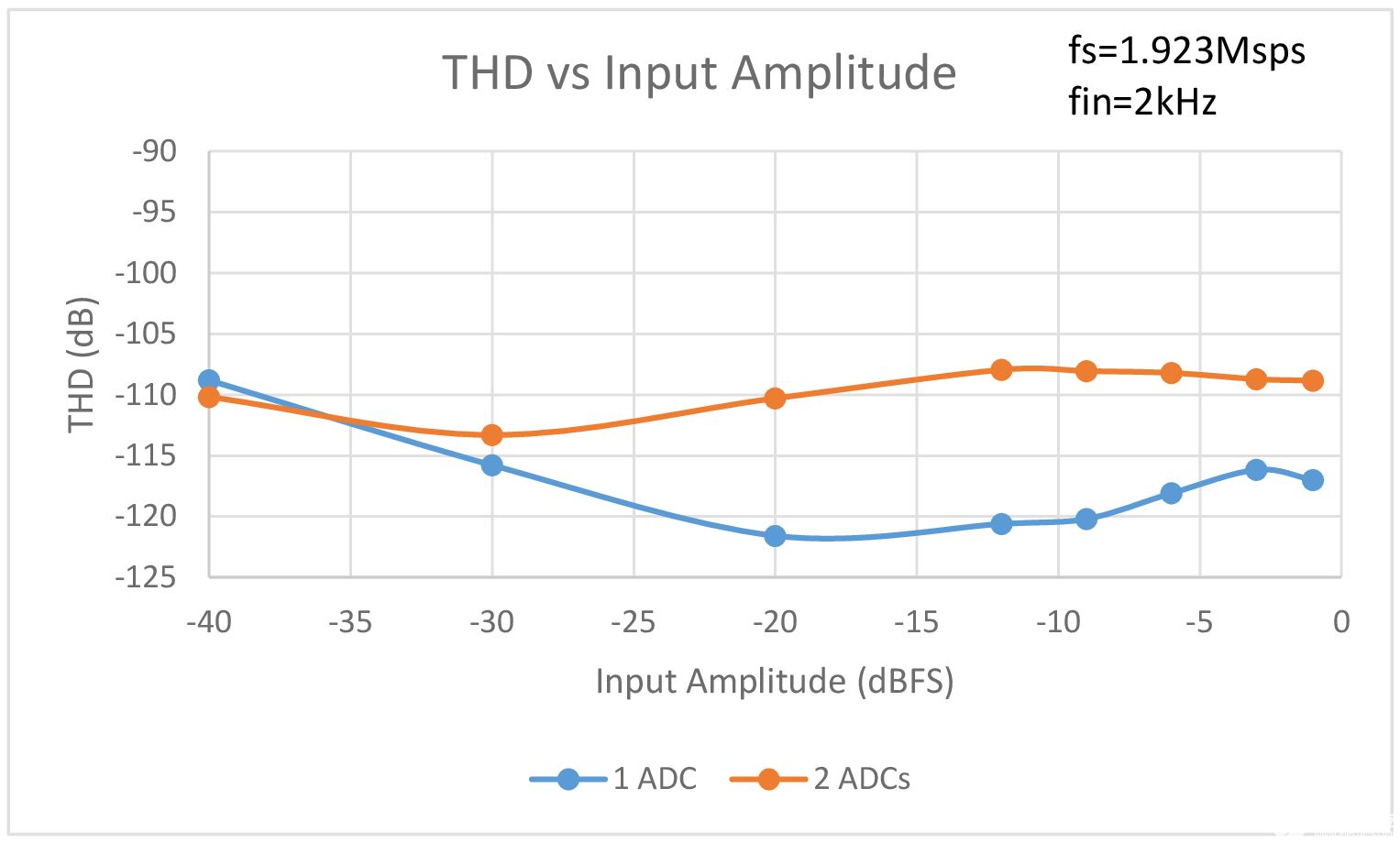

圖2比較了一個ADC和兩個共享相同基準電壓源的ADC的THD與采樣速率。如圖2所示,共享基準電壓源會導致THD在最大采樣速率下下降多達8dB。當采樣速率減慢至125ksps時,差異降至仍然顯著的4dB。圖3所示的THD與輸入幅度比較顯示,與單個ADC相比,共享基準電壓源會導致THD下降超過10dB,輸入幅度范圍為-20dBFS至-9dBFS。低于-30dBFS的輸入幅度時,THD性能幾乎相同。性能上最大的差異出現在圖4所示的THD與輸入頻率比較中。當輸入頻率高于41kHz時,當2個ADC共用一個基準電壓源時,THD性能開始斷崖式下降。當輸入頻率為50kHz時,共享一個基準電壓源的兩個ADC的THD性能幾乎不在圖表上,為-49dB,而單個ADC的THD性能為-104dB。即使在低輸入頻率下,THD的差異也始終大于7dB。

圖2.一個ADC和兩個共享公共基準電壓源的運算速率與采樣速率的關系

圖3.一個ADC和兩個共享一個基準電壓源的ADC的THD與輸入幅度的關系

圖4.一個ADC和兩個共享一個基準電壓源的ADC的THD與輸入頻率的關系

本文提供的電路和數據旨在演示當多個高性能ADC共享同一基準電壓源而每個基準電壓源輸入沒有緩沖器時發生的性能損失。在采樣速率、輸入幅度和輸入頻率范圍內,THD顯著下降。閱讀本文后,希望任何設計精密ADC電路的人都能被說服,要么為所使用的每個ADC使用單獨的基準電壓源,要么用公共基準電壓緩沖每個ADC基準電壓輸入。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17704瀏覽量

249958 -

adc

+關注

關注

98文章

6495瀏覽量

544461 -

電壓源

+關注

關注

1文章

410瀏覽量

32765 -

基準電壓源

+關注

關注

1文章

140瀏覽量

20825

發布評論請先 登錄

相關推薦

精密逐次逼近型ADC基準電壓源的設計方案

CTSD精密ADC:輕松驅動ADC輸入和基準電壓源,簡化信號鏈設計

共享基準電壓源可能會影響精密ADC性能

共享基準電壓源可能會影響精密ADC性能

評論