高速模數轉換器(ADC)是定義上的器件 對模擬信號進行采樣,因此必須具有采樣時鐘 輸入。一些使用ADC的系統設計人員觀察到速度較慢 比最初應用采樣時鐘時的預期啟動時間長。 令人驚訝的是,這種延遲的原因往往是錯誤的啟動 外部施加的ADC采樣時鐘的極性。

許多高速ADC具有以下采樣時鐘輸入 特性:

微分

內部偏置至設定的輸入共模電壓 (VCM)

設計用于交流耦合到時鐘源

此討論適用于具有具有 這些屬性。

差分ADC時鐘輸入緩沖器通常具有設計輸入切換 閾值偏移。如果沒有這樣的偏移,切換閾值將 發生在0V差分時。在沒有偏移的時鐘緩沖器的情況下 在非驅動和交流耦合的情況下,時鐘輸入(CLK+ 和 CLK–)將 每個器件均在內部上拉至共模電壓。在這種情況下, CLK+ 上的直流電壓和 CLK– 上的電壓是相同的,這 表示差分電壓等于0V。

在輸入端沒有信號的理想世界中,時鐘緩沖器不會 切換。實際上,電子系統中總是至少存在一些噪聲。 在此假設情況下,輸入切換閾值為0V,任何噪聲 在輸入端將超過時鐘緩沖器的切換閾值并導致 無意中切換。

當時鐘中設計了足夠的輸入切換閾值偏移時 緩沖區,相同的條件不會導致切換。因此,設計 交流耦合差分時鐘的切換閾值電壓的偏移 緩沖器是有益的,因此,時鐘緩沖器通常包括 切換閾值偏移。

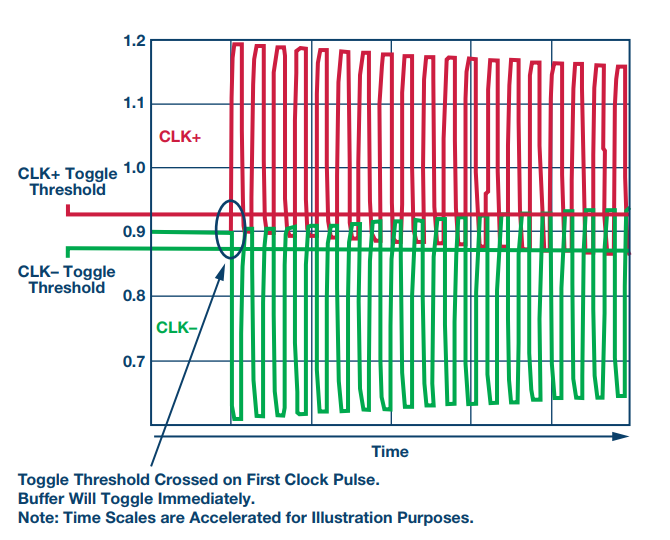

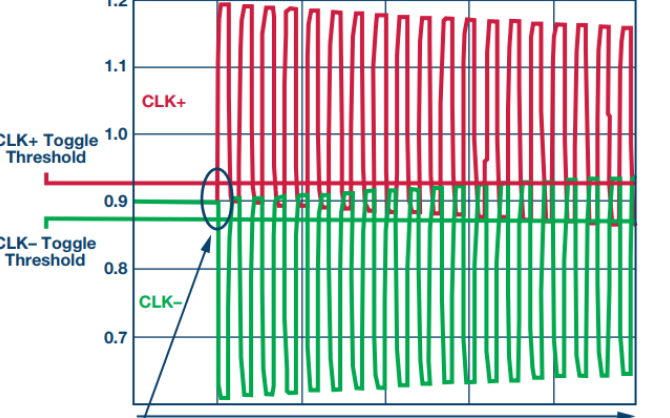

在沒有應用時鐘的情況下,CLK+ 和 CLK– 將分別被拉到相同的位置 VCM由時鐘緩沖器中的內部偏置電路實現。當時鐘 最初應用時,CLK+ 和 CLK– 上的時鐘邊沿將正擺動 和消極的,或消極的和積極的遠離以前 建立了市調機制。在圖1中,VCM = 0.9V。

圖 1 顯示了時鐘處于非活動狀態后應用的時鐘(任一 首次啟動系統時,或時鐘驅動程序處于非活動狀態后 一段時間)。在這種情況下,CLK+ 在第一個邊緣上擺動為正 和 CLK– 擺動為負。在輸入切換開關中添加正偏移 閾值,此時鐘信號將在其第一個邊沿切換時鐘緩沖器,如 如圖 1 所示。時鐘輸入緩沖器將立即產生時鐘

圖1.啟動時,CLK+ 在第一個邊緣擺動為正,CLK– 擺動為負。

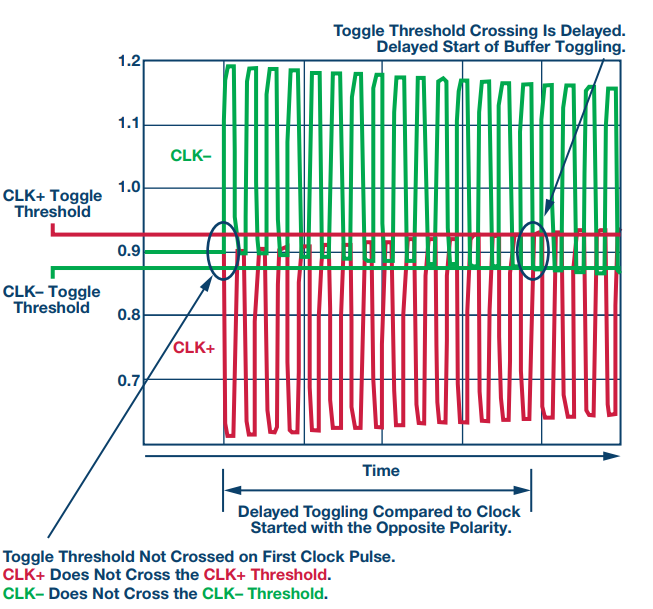

如果時鐘以相反的極性開始,CLK—— 在第一個邊緣擺動為正,CLK+ 擺動為負。隨著 輸入切換閾值增加相同的正偏移,此時鐘信號 不會在其第一個邊沿和后續邊沿上切換時鐘緩沖器 直到波形被拉到穩定狀態,并穿過切換開關 隨時間變化的閾值,如圖 2 所示。

圖2.啟動時,CLK+ 在第一個邊緣擺動為負,CLK– 擺動為正。

可以看出,初始啟動時鐘的極性會有所不同 在切換具有輸入閾值偏移的時鐘緩沖器時。在一種情況下(CLK+ 在本例中最初上升)時鐘緩沖區理想情況下將開始切換 首次應用時鐘時立即。極性相反 (CLK+在本例中最初落下),時鐘緩沖區將不會啟動 首次應用時鐘時立即切換。

如果您發現 ADC 啟動出現意外延遲,請嘗試反轉 時鐘啟動極性。這可能會改變您的啟動時間。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8694瀏覽量

147087 -

緩沖器

+關注

關注

6文章

1921瀏覽量

45473 -

adc

+關注

關注

98文章

6495瀏覽量

544467

發布評論請先 登錄

相關推薦

嵌入式Linux啟動時間優化的秘密之四-啟動腳本

電機啟動時間一般是多久?怎么縮短啟動時間呢?

電機啟動電流與啟動時間的關系是什么?

電腦啟動時間長的原因及處理方法

Linux系統啟動時間優化方案

Xilinx7系列基于PCIe的設計如何滿足PCIe啟動時間的要求

基于FPGA的PCIe設備如何才能滿足PCIe設備的啟動時間的要求?

嵌入式 Linux 啟動時間優化

ADC時鐘極性與啟動時間的關系

ADC時鐘極性與啟動時間的關系

評論