高速混合信號IC的設計需要深刻的改變,以應對其日益增加的復雜性和性能要求。

傳統的功能分區和專業領域(如電路設計、布局設計和驗證)正在迅速模糊。開發人員跨不同技術領域的創新能力是關鍵。這些技術趨勢的影響不僅限于產品開發,它們還深刻影響著業務戰略。

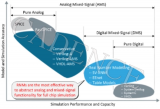

高速混合信號系統將數字信號處理、RF(包括微波/毫米波)和有線通信連接起來,創造了技術和業務相關挑戰的強大組合。這些挑戰是由對普遍訪問高吞吐量數據傳輸的需求快速增長所驅動的。

5G通信承諾更快,更普遍的連接,支持多種通信標準,同時降低基礎設施的尺寸和運營成本。對更高集成度、低功耗和降低成本的需求都有望加速到一個似乎根本不可能得到減速摩爾定律支持的水平。

摩爾定律的焦點是晶體管密度。但在過去,CMOS縮放也提供了速度提升,使數字和模擬電路都受益,盡管損害了許多其他關鍵的模擬特性。然而,更高的數字密度使ADI公司克服了納米工藝的一些缺陷。

雖然晶體管密度的增加和成本的降低將持續至少五年左右,但更精細的光刻節點的速度改進正在大幅減少。數字電路在擴展到16納米及以上時,開關能量和功率仍將下降,但我們不應期望門的運行速度比以前的節點快得多。畢竟,數字處理器的時鐘速度在大約十年前就已經停滯不前,通過并行性實現了更高的處理速度。

盡管數字功能的成本持續下降,但公司仍然面臨前期成本飆升和設計復雜性等財務障礙。這些因素正在迅速增加,這決定了工程和商業選擇。

當我們繼續在比例光刻中構建復雜的系統時,我們必須問,這種回報是否值得。比以往任何時候都更沒有簡單而廣泛的答案。

正如我們行業其他轉折點的情況一樣,超越根深蒂固的假設的工程師的獨創性將是關鍵。大幅降低功耗,從而減小尺寸和提高集成度的途徑可以概括為三個步驟:

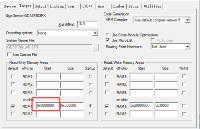

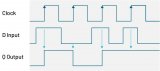

第一步是混合信號和數據轉換器系統的架構創新,包括不同形式的模擬并行性、高階連續時間循環和新興的時域轉換器。第二步是更多地使用數字輔助模擬技術,包括自調整和校準、動態元件匹配和抖動。最后,工程師需要智能地在不同芯片之間劃分功能塊,同時在適當的CMOS節點以及SiGe、GaAs和GaN等化合物半導體工藝中集成適當的技術,以創建高性能模塊和封裝。

通過這種方式,電源管理、RF和混合信號模塊等傳統組件之間的功能界限將變得模糊,從而為更大的協同設計打開大門。企業高管們請注意:我們不會通過營銷或漸進式創新來擺脫這個難題。如果我們要繼續提供財務回報,我們需要技術領先來承擔所需的風險,為下一代混合信號系統的設計人員提供支持。

審核編輯:郭婷

-

微波

+關注

關注

16文章

1044瀏覽量

83733 -

晶體管

+關注

關注

77文章

9702瀏覽量

138430 -

RF

+關注

關注

65文章

3055瀏覽量

167102

發布評論請先 登錄

相關推薦

ADS1299信號偏移是什么原因引起的?

混合域示波器的原理和應用

如何避免焊接機器人焊縫偏移

利用ADS1235和ADS1261中的交流激勵模式減少電橋測量偏移和漂移

時鐘抖動和時鐘偏移的區別

INA849輸出信號嚴重偏移是什么原因導致的?

熔接機v型槽偏移怎么調整

什么是中斷向量偏移,為什么要做中斷向量偏移?

混合信號設計中的偏移

混合信號設計中的偏移

評論