負載效應 (loading) 的控制對良率和器件性能有重大影響,并且它會隨著 FinFET(鰭式場效應晶體管)器件工藝的持續微縮變得越來越重要。當晶圓的局部刻蝕速率取決于現有特征尺寸和局部圖形密度時,就會發生負載效應。刻蝕工藝 loading 帶來的器件結構上的微小變化可能會對器件良率和性能產生負面影響,例如在偽柵多晶硅刻蝕過程中,由于刻蝕的負載效應,可能會在柵極和鰭結構交叉區域產生多晶硅邊角殘留,進而造成 FinFET 結構的改變,并直接影響 FinFET 柵極的長度和電學性能。多晶硅邊角殘留對良率和器件性能的影響,包括可接受的殘留的尺寸大小,可使用 SEMulator3D提前預測。

FinFET器件的多晶硅邊角殘留

建模和工藝窗口檢查

多晶硅邊角殘留會在鰭片柵極交叉區域產生金屬柵極凸起。這些凸起可以在許多不同的 FinFET 節點上找到,多晶硅邊角殘留通常在偽柵多晶硅刻蝕工藝中形成。

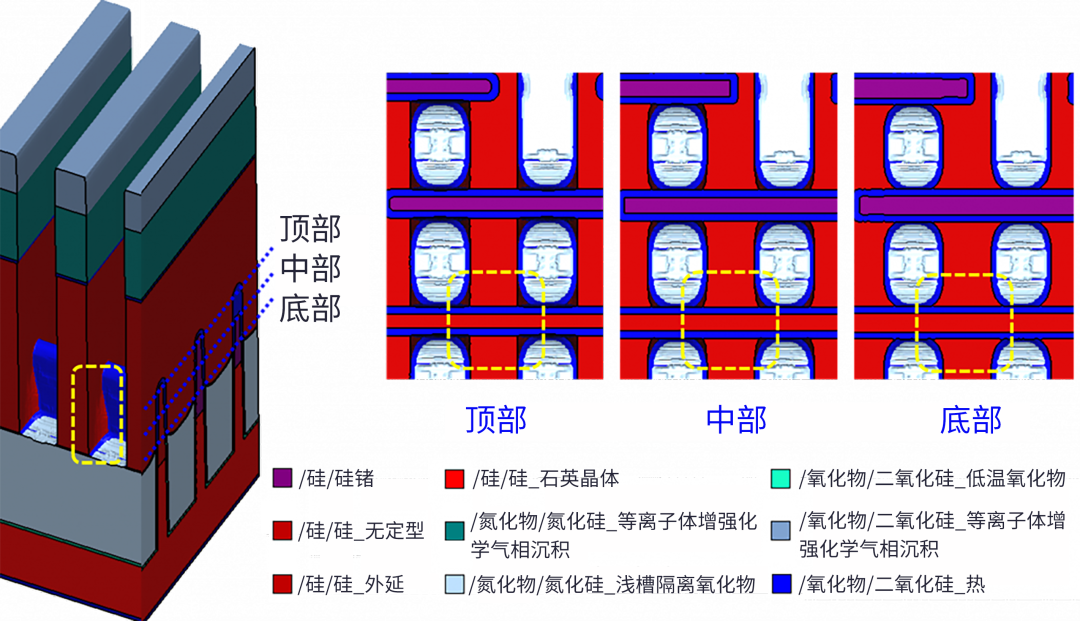

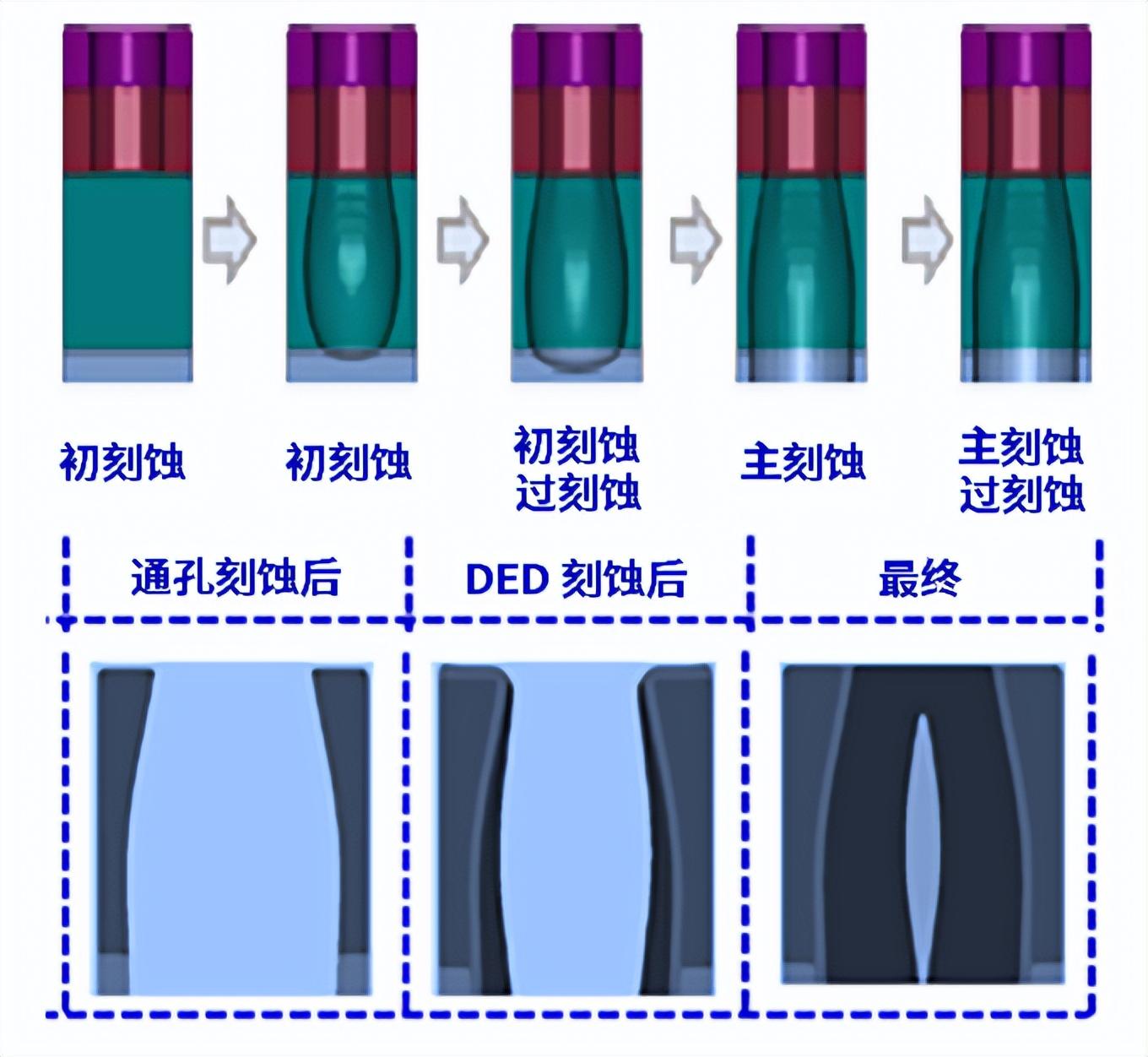

圖1:在不同高度生成的3D邊角殘留及其輪廓

我們在 SEMulator3D 中構建了一個使用 SRAM111 結構的 5nm logic 虛擬工藝模型,以研究多晶硅刻蝕殘留的行為。在這個模擬的多晶硅刻蝕工藝中,SEMulator3D 使用了圖形負載刻蝕來模擬多晶硅殘留輪廓。圖1(左)顯示了計算機生成的多晶硅殘留結構,不同高度(鰭片頂部、中部和底部)的多晶硅輪廓見圖1(右)。

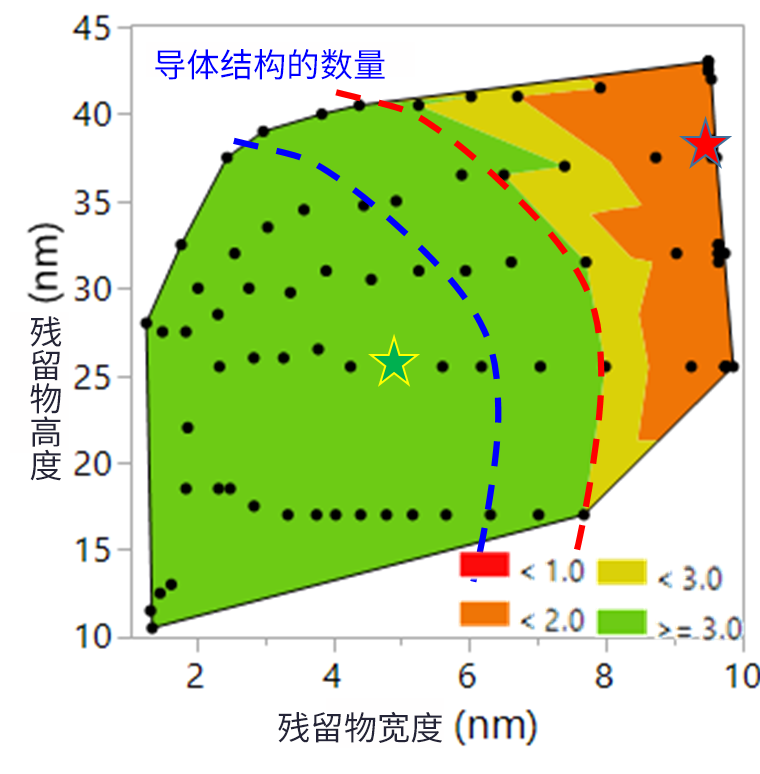

在該模擬器件發生結構硬失效(如短路)之前,多大的多晶硅邊角刻蝕殘留是可以被接受的,可以通過在虛擬 DOE(實驗設計)中測試100種殘留寬度和高度的組合來研究這個問題。我們測量了虛擬制造過程中關鍵步驟的導體結構數量,作為了解器件中是否有短路或故障(如源漏外延與偽柵多晶硅之間的短路)的一個指標 。如果殘留物太大并使偽柵多晶硅與源漏外延層短接,那么結構中導體結構 (net) 的數量將小于3。圖2所示的等高線圖包含不同殘留寬度和高度下的導體結構數量,綠色區域顯示,可以把器件源漏柵3個導體結構區分開的器件結構。考慮到殘留寬度和高度的潛在制造差異(可能分別為1.5nm和5nm),安全的工藝窗口需要往左下方做適當平移(如藍色虛線所示)。

圖2:包含不同殘留物寬度和高度下導體結構數量的等高線圖

多晶硅邊角殘留

對FinFET器件性能的影響

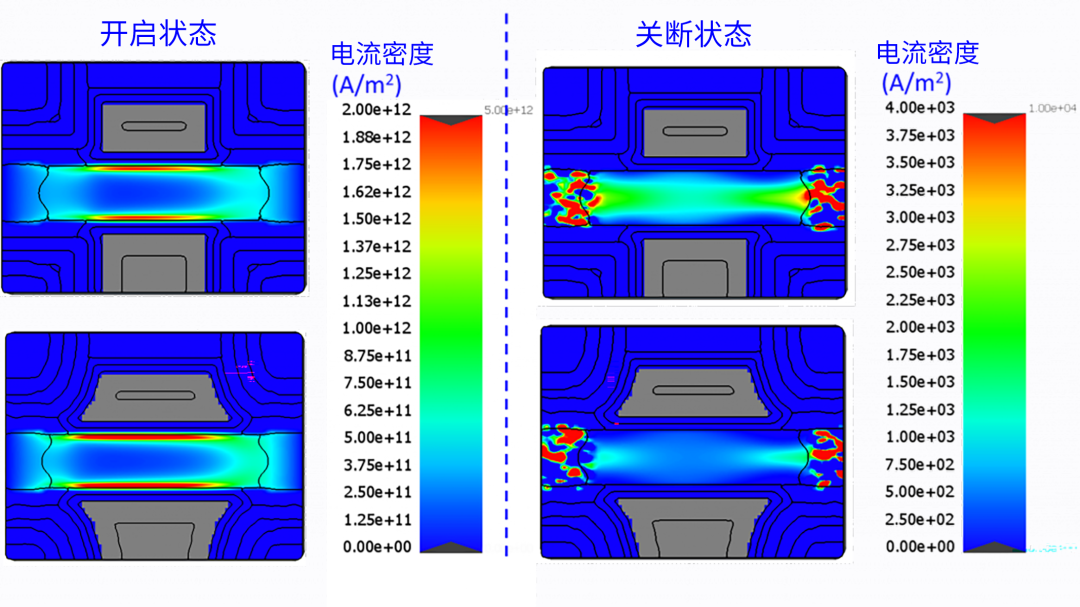

使用可接受的多晶硅殘留(沒有硬失效)之后,我們模擬了器件電學性能。結果表明,較大的殘留實際上有益于開啟狀態下的驅動電流提升、關斷狀態下漏電流、亞閾值擺幅和漏致勢壘下降 (DIBL) 的減小。與無殘留的理想結構相比,它可以通過更高的開啟狀態電流 (108%) 和更低的關斷狀態漏電流 (50%) 提高器件性能。為了進一步了解該器件性能提升的機制,我們研究了存在較大殘留時鰭片底部的開啟和關斷狀態下的電流密度分布(見圖3)。

開啟狀態時,如果存在多晶硅殘留,通道長度會加大,殘留覆蓋了源極/漏極和柵極之間的部分串聯電阻區,從而使這個區域的串聯電阻減小,導致驅動電流增大;器件關斷時,源極和漏極之間的大部分鰭片區域都可以由柵極控制。因此,當存在多晶硅殘留時,源極和漏極之間的電阻較高,并帶來較低的關斷漏電流。

圖3:鰭片底部的通/斷態電流分布(上圖:無殘留,下圖:有殘留)

結論

本文中,我們使用了 Coventor SEMulator3D 來研究 5nm FinFET 工藝中的工藝窗口以及多晶硅邊角刻蝕殘留對器件性能的影響。這項研究幫助我們更好地了解不同偽柵多晶硅殘留尺寸下可接受的工藝窗口和相關器件性能。我們的研究表明,不必追求多晶硅邊角殘留的最小化,而是可以通過控制多晶硅殘留的尺寸,在不損失良率的同時獲得器件性能的提升。

審核編輯:湯梓紅

-

晶體管

+關注

關注

77文章

9684瀏覽量

138091 -

FinFET

+關注

關注

12文章

248瀏覽量

90209 -

負載效應

+關注

關注

0文章

16瀏覽量

2774

原文標題:使用虛擬實驗設計預測先進FinFET技術的工藝窗口和器件性能

文章出處:【微信號:泛林半導體設備技術,微信公眾號:泛林半導體設備技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

5nm及更先進節點上FinFET的未來:使用工藝和電路仿真來預測下一代半導體的性能

借助虛擬工藝加速工藝優化

labview實驗設計

基于labview的高頻電子虛擬實驗設計

基于FinFET IP的數據轉換器設計

實驗設計基礎

Xilinx與臺積電合作采用16FinFET工藝,打造高性能FPGA器件

使用虛擬實驗設計加速半導體工藝發展

使用虛擬實驗設計加速半導體工藝發展

使用虛擬實驗設計預測先進FinFET技術的工藝窗口和器件性能

使用虛擬實驗設計預測先進FinFET技術的工藝窗口和器件性能

評論