最近在用LTspice仿真D觸發(fā)器的一個串并輸入功能,只有第一個觸發(fā)器的波形跟理論分析一致,其他剩余的就是怎么也不行。 經(jīng)過資料查找,和不停地嘗試,最終還是找出了原因。 確實每一個工具還是有其特點的,跟實際的芯片還是有差異。

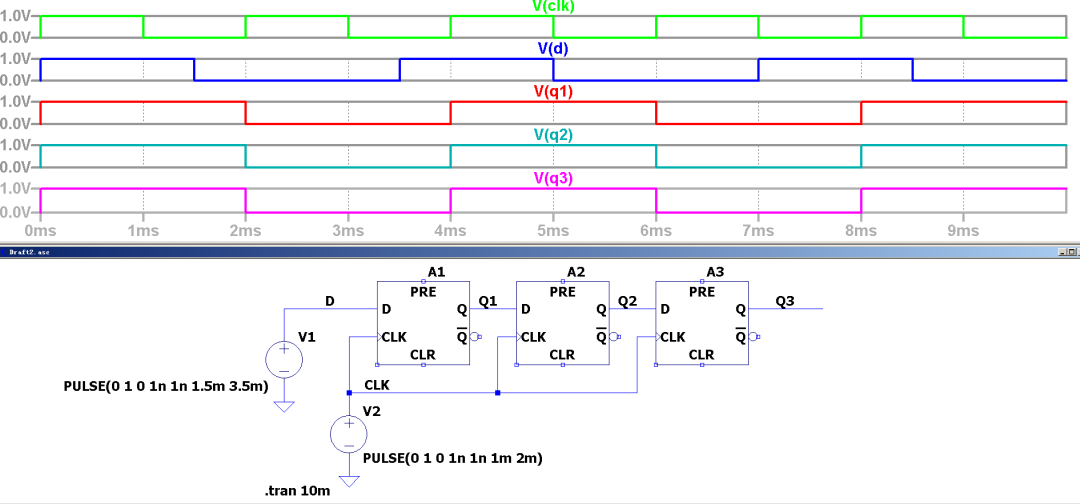

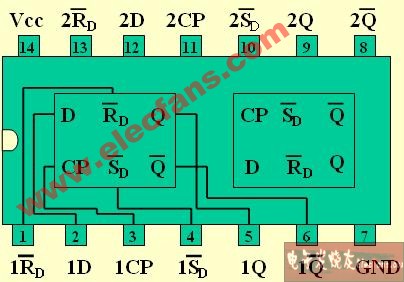

今天就來看看這個問題的前世今生。 首先看一下要仿真的電路圖。

在這種類型的寄存器中,輸入是一次一位串行,輸出也是串行一位。 帶D觸發(fā)器的串行輸入串行輸出移位寄存器設計,每個觸發(fā)器一次只能存儲一位,因此對于 4 位移位寄存器,需要四個觸發(fā)器。 如上所示,串行數(shù)據(jù)通過第一個觸發(fā)器的 D 應用到所有剩余的觸發(fā)器。 當一系列數(shù)據(jù)輸入寄存器時,每一位都隨著時鐘脈沖的每個正沿提供給下一個觸發(fā)器,并且隨著每個時鐘脈沖,串行數(shù)據(jù)從一個觸發(fā)器移動到下一個觸發(fā)器。 如果時鐘每跳動四次也就是四個周期,那么可以并行取出一次,也就完成了串行轉并行的功能。

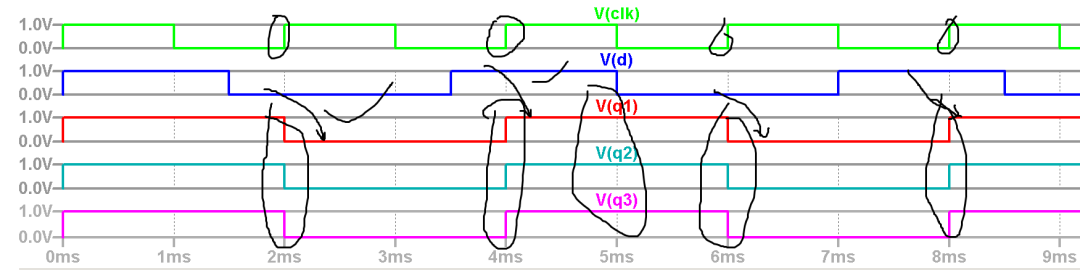

打開LTspice以后,放置元器件然后進行仿真,但是得出來的結果如下。 兩個電源設置上升沿和下降沿都設時間都為1ns,頻率和高電平讓其不一樣。

可以看到,輸入并沒有移位,而是Q2和Q3都是跟Q1一模一樣的波形。 這個是不對的,我們可以看到,該跳轉的沒有跳轉。 可以看到只有Q1的輸出是正確的。

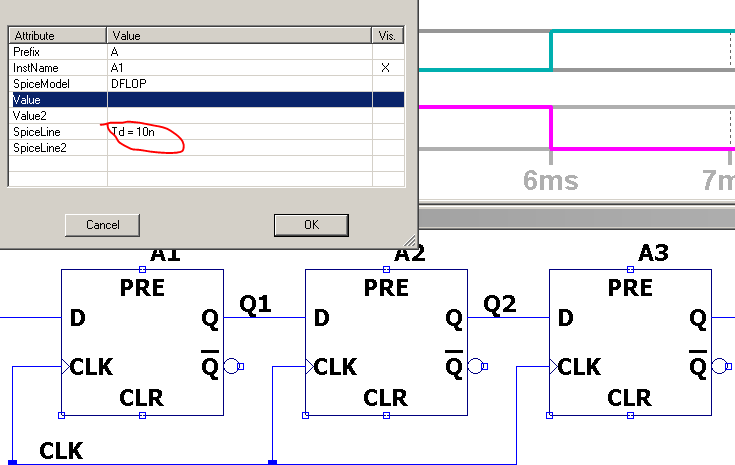

這個問題困擾我也挺久,后來發(fā)現(xiàn)是由于這個器件可以說理想器件吧,輸出沒有延時導致的。 我也嘗試過設置這個器件的上升沿和下降沿但是都不行,只有設置了這個器件的延時功能,就可以了。 如果所示,只要打開觸發(fā)器的屬性,然后在SpiceLine里面輸入延時10nS。 具體如下圖所示。

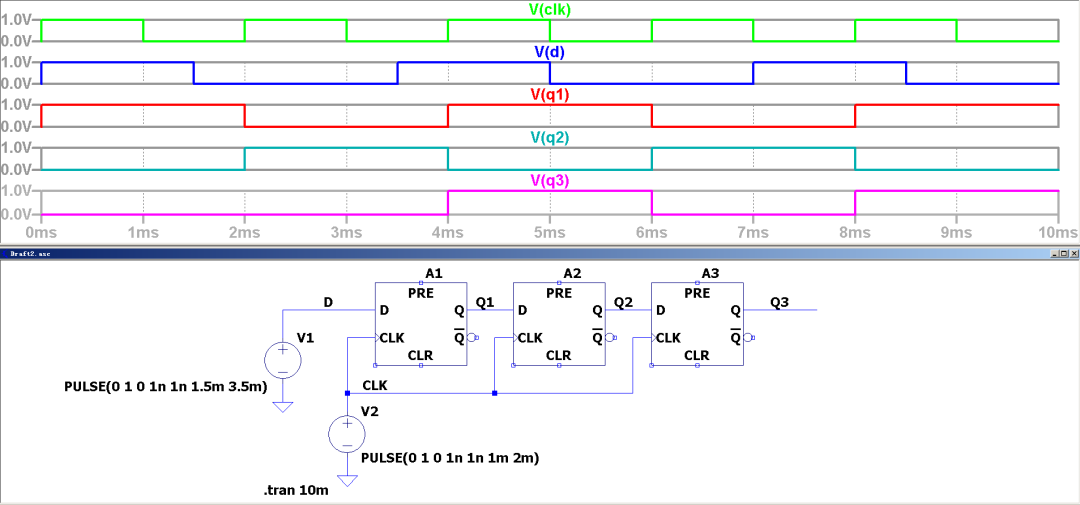

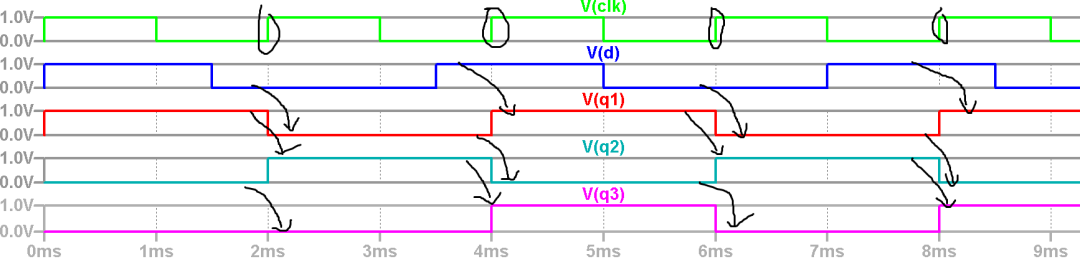

此時再運行這個仿真電路圖,就可以得出來正確的結果。 如下圖所示。

我們再來分析一下,這次的波形結果。

如圖中箭頭所標出來的,這次的波形就完全符合理論分析了。 每一次時鐘跳轉的時候,其D觸發(fā)器會把其輸入轉到輸出。

-

寄存器

+關注

關注

31文章

5444瀏覽量

125227 -

仿真

+關注

關注

52文章

4314瀏覽量

136192 -

D觸發(fā)器

+關注

關注

3文章

176瀏覽量

48896 -

觸發(fā)器

+關注

關注

14文章

2041瀏覽量

62302 -

LTspice

+關注

關注

1文章

127瀏覽量

14061

發(fā)布評論請先 登錄

D觸發(fā)器,CLK突變時,輸入D也突變,觸發(fā)器的輸出應該如何判定?

D觸發(fā)器工作原理是什么?

評論