■ ASIC(Application Specific Integrated Circuit,專用集成電路)

ASIC 是為滿足顧客特定需求而設計制造、面相特定用途的集成電路的總稱。面向特定用途的集成電路分為全定制IC和半定制 IC。通常所說的ASIC主要指門陣列、嵌入式陣列、標準單元 ASIC、結構化 ASIC 等。

■ ASSP(Application Specific Standard Product,專用標準產品)

相對于 ASIC 這種為特定顧客定制的 LSI,ASSP 是面向某一特定領 域或應用的通用 LSI。因為不是針對某一顧客而特別定制的芯片,所以 作為通用器件(標準器件)具有可提供給不同客戶的優勢。

CPLD 是指將多個小規模 SPLD 作為基本邏輯塊,再通過開關連接而成的中規模(大規模)PLD,因為單純擴大AND-OR 陣列規模會導致資源浪費。CPLD邏輯部分的延遲時間和開關部分的延遲時間比較固定, 因此設計較為容易。

■ DLL(Delay-Locked Loop,延遲鎖定環)

DLL 的基本功能和 PLL 的相同:可以實現零傳輸延遲;可以為分散邏輯門陣列)。

■ IP(Intellectual Property,設計資產)

IP 本來的意思是知識產權,而在半導體領域,CPU 核、大規模宏單 元等功能模塊被稱為IP(設計資產)。使用經過驗證的成品功能模塊(IP),比重新設計電路更高效且可以縮短開發周期。為了和固件、中間 件等軟件 IP 區別開來,電路 IP 也被稱為“硬 IP”或“IP 核”。

■ LUT(Look-up Table,查找表)

通過將函數的真值表存放在少量內存單元中來實現組合邏輯電路功能的模塊稱為 LUT。直接用電路的方式實現復雜函數,產生的電路可能會存在面積過大或速度過低等問題,而基于 LUT 的實現方式則有可能解決這些問題。

■ LVDS(Low Voltage Differential Signaling,低電壓差分信號)

LVDS 是一種使用差分方式傳輸低電壓、小振幅信號的接口技術。該數字傳輸標準可以達到數百 Mbit/s 信號傳輸速度。

■ PLD(Programmable Logic Device,可編程邏輯器件)

PLD 是用戶可將設計電路寫入芯片的可編程邏輯器件的總稱。代表性的 PLD 有 SPLD、CPLD 和 FPGA 等。

■ PLL(Phase-Locked Loop,鎖相環)

PLL 是一種用來同步輸入信號和輸出信號頻率和相位的相位同步電路,也可用來實現時鐘信號的倍頻(產生輸入時鐘整數倍頻率的時鐘)。在 FPGA 芯片上,PLL 用來實現對主時鐘的倍頻和分頻,并且 PLL的輸出時鐘之間保持同步。與基于延遲的 DLL 原理不同,PLL 采用 VCO(壓控振蕩器)來產生和輸入時鐘相似的時鐘信號。

■ RTL(Register Transfer Level,寄存器傳輸級)

RTL 用來表示使用 HDL 進行電路設計時的設計抽象度,是一種比晶體管和邏輯門級別的設計抽象度更高的寄存器傳輸級(RTL)的設計方式。RTL 設計將電路行為描述為寄存器間的數據傳輸及其邏輯運算的組合。

■ SERDES(Serializer-Deserializer,串行器-解串器)

SERDES 通過用串行、并行相互轉換模塊,來實現使用高速串行接口連接并行接口的功能。最近的高速通信接口以串行為主流,因此不需要考慮并行通信中布線長度不一所導致的傳輸位間的時間偏移問題。

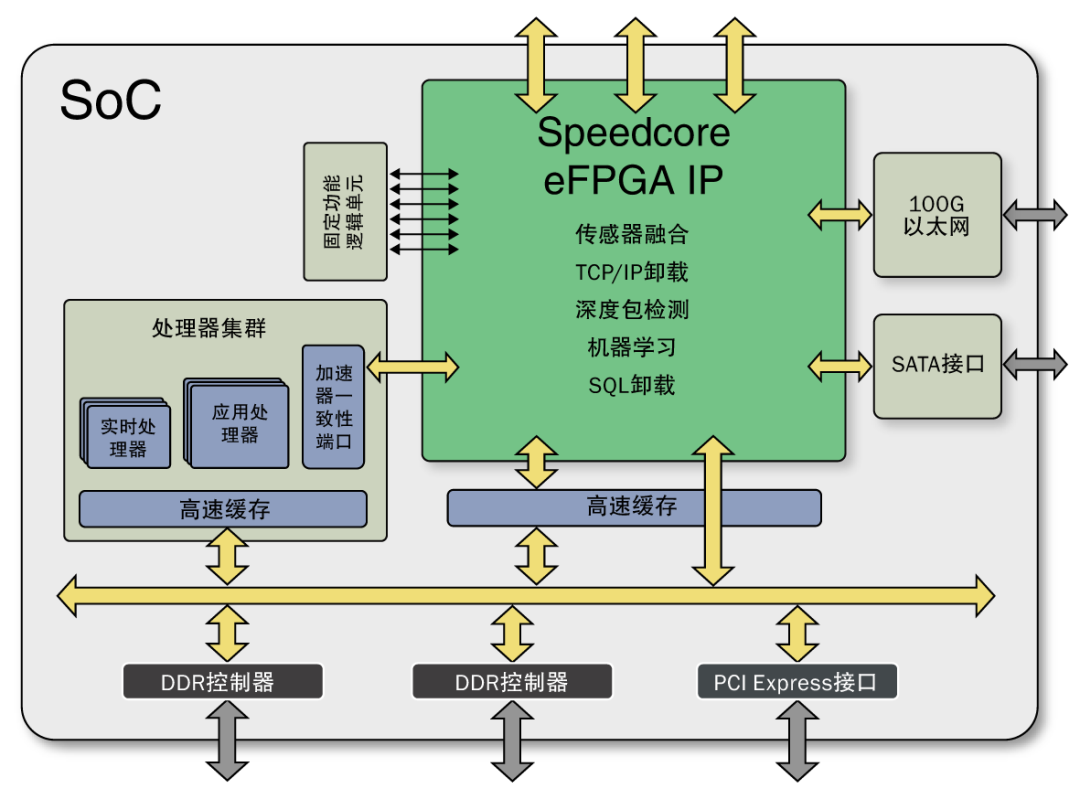

■ SoC(System on a Chip,片上系統)

從前的 LSI 按照功能分為處理邏輯、內存、接口等產品,而今后的趨勢是將各種豐富的功能系統性地集成到一片 LSI 上,這種 LSI 被稱為SoC 或系統 LSI。

■ SPLD(Simple PLD,簡單可編程邏輯器件)

SPLD 是由標準積之和形式的 AND-OR 陣列(積項)構成的小規模PLD。也有一些附加嵌入各種宏單元或寄存器的產品。

■ SRAM(Static Random Access Memory,靜態隨機存儲器)

SRAM 是一種可以自由進行讀寫操作的半導體隨機存儲器(RAM),并且屬于斷電后數據會丟失的易失性存儲器。由于不像 DRAM 那樣需要周期性地刷新操作(保持數據),因此被稱為靜態存儲器。

■ 反熔絲(anti-fuse)

反熔絲在通常狀態下絕緣,加以高電壓時絕緣層會打開通孔熔通成為連接狀態。由于它和合金熔絲的特性相反,因此被稱為反熔絲。反熔絲形成的內部連接阻抗低,可用來實現高速電路。雖然反熔絲具有非易失性,但是編程寫入的操作只能進行一次。

■ 嵌入式陣列(embedded array)

嵌入式陣列的開發流程是在用戶決定好所需的硬宏單元時就先行投放晶圓進行生產,硬宏單元之外的用戶邏輯部分先部署門陣列。用戶完成邏輯設計后,只要在金屬層工序實施用戶邏輯的布線即可完成生產。這樣,就可以同時具有標準單元 ASIC 中硬宏單元的高性能,以及堪比門陣列的短開發周期這兩方面的優勢。

■ 時鐘樹(clock tree)

大規模 LSI 中的布線延遲會導致各個信號到達時間不一致。特別是同步電路設計中電路的動作由時鐘控制,這種信號傳播上的時間差會帶來不好的影響。因此需要時鐘樹這種時鐘專屬的布線和驅動電路來改善信號的偏差和傳播速度。

■ 門陣列(Gate Array,GA)

門陣列是一種除布線之外所有掩膜工序都提前完成,用戶只需要進行片上門電路之間的金屬布線工程就能完成生產的芯片開發方式。這種方式具有開發周期短的優勢。門陣列分為門電路區域和布線區域固定的通道(channel)型,以及門電路遍布整個芯片的門海(sea-of-gate)型。

■ 高層次綜合(High Level Synthesis,HLS)

高層次綜合指直接使用 C 語言或者基于 C 的語言描述算法功能,再由工具自動將其綜合為含有寄存器、時鐘同步等硬件概念的 RTL 描述的過程。

■ 結構化ASIC(structured ASIC)

結構化 ASIC 是指為了縮短開發周期,在門陣列基礎上加以 SRAM、時鐘 PLL、輸入 / 輸出接口等通用功能模塊,將需要定制開發的部分降低到最小限度的芯片開發方式。例如制造方預先在專用布線層設計好時鐘電路等方法,可以有效減輕用戶的設計成本。

■ 標準單元ASIC(cell-based ASIC)

在基于標準單元庫基礎之上,提供更大規模電路模塊(巨型單元、宏單元等)的 IC 開發方式。在使用標準單元實現的隨機邏輯之上,提供 ROM、RAM、微處理器等巨型單元。系統 LSI 是在標準單元 ASIC的基礎上多功能化和大規模化而來的產物。

■ 軟核處理器(soft-core processor)

軟核處理器是可以通過邏輯綜合來實現的微處理器核,在 FPGA 領域得到了廣泛的應用。軟核具有很多優勢,例如可以在不同 FPGA 系列中使用,可以根據需要定制搭載必要數量的周邊電路和 I/O,還可以根據需要自由裝載多個處理器(多核化)等。

■ 動態部分重配置(dynamic partial reconfiguration)

部分重配置是指在可重構設備上實現的電路中,只對其中一部分進行重新配置。動態部分重配置則是指在其他部分正常工作的情況下,動態地對某一部分進行重新配置。使用動態部分重配置功能可以卸載無須同時工作的電路,從而得到面積和功耗上的改進。

■ 動態可重構處理器(Dynamically Reconfigurable Processor,DRP)

動態可重構處理器是可重構系統的一種,商品化的產品通常是將粗粒度的 PE(Processing Element,處理單元)和分散的內存模塊按二次元陣列型放置,各個 PE 的指令和 PE 之間的連接可以動態地(在工作時)改變。

■ 硬件描述語言(Hardware Description Language,HDL)

硬件描述語言是描述硬件行為和連接的編程語言。最早的數字電路設計通過組合 AND、OR、NOT、FF(Flip-Flop)等邏輯電路的符號來繪制電路圖完成設計,這些年基于硬件描述語言的設計方法成為主流。硬件描述語言中,Verilog HDL 和 VHDL 作為行業標準應用得最為廣泛。

■ 硬宏單元(hard macro)

硬宏單元是指 FPGA 內部嵌入的固定的硬件電路模塊。雖然可以使用 FPGA 的基本門來實現乘法器這類電路,但消耗的資源非常多,開銷會增大。而如果使用硬宏單元,就不會對應用的性能有過多的影響。

■ 閃存(flash memory)

一般的 EEPROM 可以對指定地址的內存進行擦除,而閃存是一種通過簡化結構提高了速度和集成度,但只能批量擦除的 EEPROM。FPGA 中閃存的使用方式有兩種,一種是將閃存單元用作邏輯和布線記憶單元的直接型,另一種是用閃存對 SRAM 型 FPGA 進行配置的間接型。

■ 制程工藝(process technology)

雖然半導體制程的開發有兩大分支——工藝和材料,但回顧基于硅材料的晶體管發展歷史,微型工藝的進步是半導體產業成長的主要基礎。LSI 主要構成器件是 MOS 型場效應管(MOSFET),只要可以制造更微小的 MOSFET,就能同時實現降低功耗、加快反應速度和增加單位面積晶體管數量等目標。

■ 乘積項(product term)

所有邏輯表達式都可以變換為與項(AND)的邏輯或(OR),也就是積之和的形式。由 AND 陣列和 OR 陣列組成的 AND-OR 構造稱為乘積項形式。乘積項是 SPLD 和 CPLD 中代表性的基本結構。

■ 可重構系統(reconfigurable system)

可重構系統是靈活運用細粒度(FPGA)或粗粒度(PE 陣列)的可重構器件,根據應用特征改變包括數據通路(data path)在內的硬件結構的系統總稱。這種方式比開發專用硬件更具彈性,又可以針對各種問題的算法優化結構實現高性能運算。

■ 可重構邏輯(reconfigurable logic)

可重構邏輯是可以在 PLD 中通過重新寫入配置來改變電路結構的LSI 的總稱。FPGA 和 CPLD 都屬于這一類,它們都使用 SRAM 單元、EEPROM 單元或閃存單元作為存儲器件。在工作中可以改變電路結構的器件被稱為動態可重構邏輯。

■ 粒度(granularity)

這里的粒度指電路規模。通常“粒度”一詞用來描述粉狀物體顆粒的大小程度,比如顆粒的粗糙程度、細膩程度。目前主流 FPGA 中基本邏輯塊的粒度位于門陣列(晶體管級別)和 CPLD(乘積項)之間,但通常也被稱為細粒度(fine grain)。而粗粒度(coarse grain)通常指具有4~32 位 PE(Processing Element)陣列的動態可重構處理器。

■ 邏輯綜合(logic synthesis)

邏輯綜合是指從 Verilog HDL 或 VHDL 等硬件描述語言編寫的 RTL電路轉換為 AND、OR、NOT 等門級網表(門間連線信息)的過程。

■ 邏輯塊(logic block)

邏輯塊是指用來實現邏輯的電路塊。CPLD 中的邏輯塊是乘積項結構的宏單元。FPGA 中的邏輯塊雖然叫法因廠商而異,但大致都是由LUT 和觸發器組成的基本單元,再加上一些提高性能的附加電路構成的。

審核編輯 :李倩

-

FPGA

+關注

關注

1644文章

21993瀏覽量

615569 -

寄存器

+關注

關注

31文章

5427瀏覽量

123746 -

數字傳輸

+關注

關注

0文章

15瀏覽量

9022

原文標題:【收藏】理解FPGA的基礎知識——FPGA專業術語

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

想快速掌握電路電子術語?這些關鍵名詞別錯過!(附:基礎詞匯電子版)

探索物聯網專業術語:開啟智能互聯世界的鑰匙

玩轉FPGA必備的基礎知識

Achronix Speedcore eFPGA的特性和功能

Verilog vhdl fpga

FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

【《大語言模型應用指南》閱讀體驗】+ 基礎篇

求助關于論壇的選擇

14芯M16公頭連接器專業術語

評論