3D NAND閃存實現了新一代的非易失性固態存儲,適用于幾乎所有我們可以想像得到的電子設備。

3D NAND能夠實現超過2D NAND結構的數據密度,即便是在新一代技術節點上制造時也是如此。

然而,目前提高3D NAND存儲容量的方法可能會帶來一些在存儲器儲存、結構穩定性和電氣特性方面的不利影響。

3D NAND器件及其工作原理

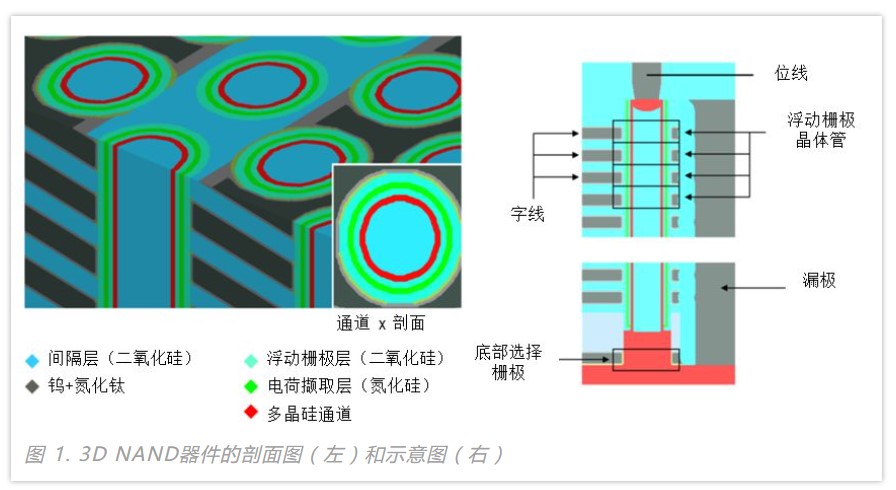

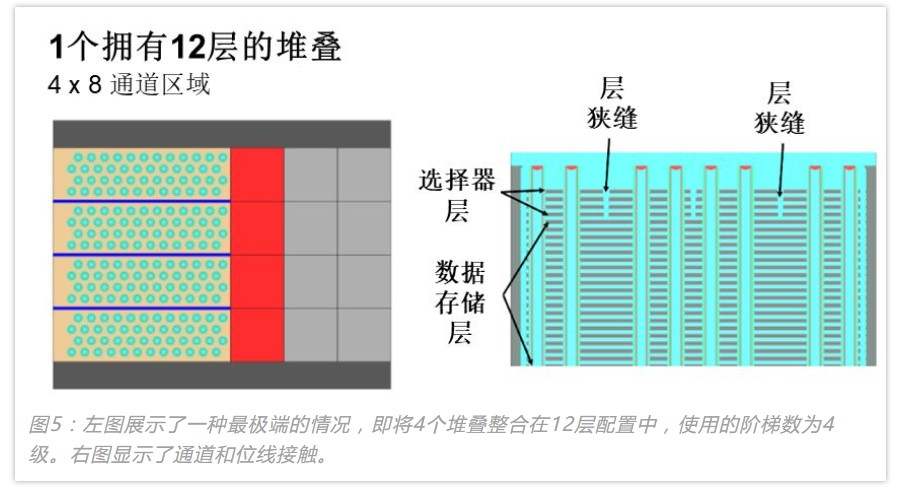

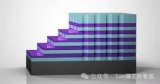

3D NAND器件包括三個主要組成部分:一是存儲數據的通道區域,它以垂直方式穿過交替堆疊的導體層和絕緣層;二是“階梯”,用于訪問上文提及各層中的每個字線;三是狹縫,用于隔離連接位線的通道。下圖展示了3D NAND堆疊的剖面圖(左)與示意圖(右):

如上圖所示,電荷擷取型3D NAND結構采用鎢和二氧化硅的交替堆疊,其垂直圓柱狀通道穿透整個堆疊。當電壓施加到字線時,電子通過隧道從通道區域移動到由氮化硅組成的電荷擷取層,數據被寫入或擦除。

存儲容量挑戰

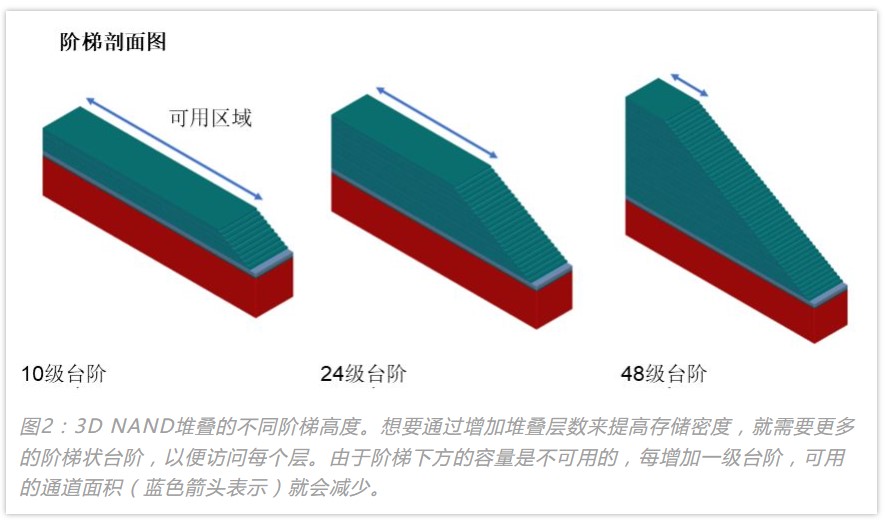

雖然3D NAND存儲容量的提高看似可以通過添加更多堆疊層非常輕松地實現,但堆疊高度的增加會帶來很大的挑戰。如下圖所示,通道的可用面積將會減小:

隨著“階梯”高度的提高,可用的空間隨之減少。在某些類型的3D NAND中,由于去除了階梯“臺階”之間的犧牲層,產生了更多的挑戰。

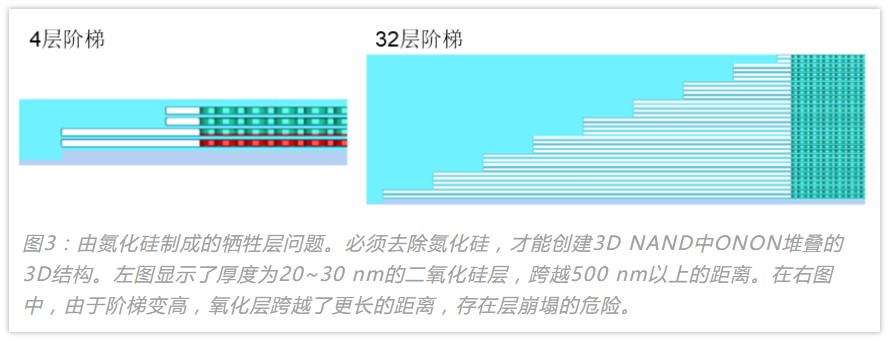

在這些結構中,工程師通過濕法刻蝕去除犧牲層,是為了給之后制造工藝中的原子層沉積創造空間。

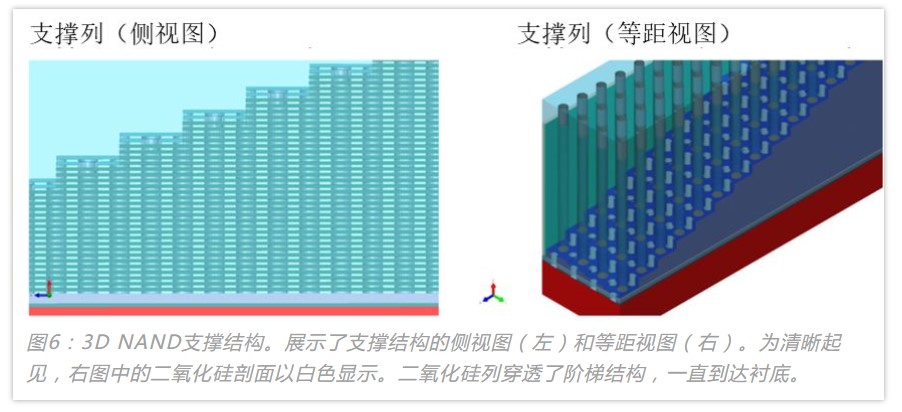

因此,更高的階梯意味著有更長的隔離層將懸浮在空中,也意味著結構崩塌的可能性更高:

對臺階進行分區,可在臺階結構中插入更多字線接觸通孔,從而創建更緊湊的階梯,而不出現崩塌的危險。

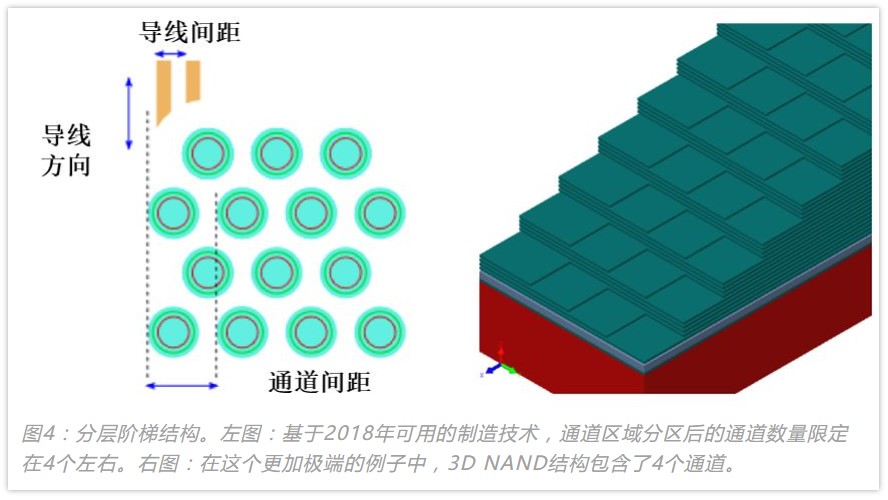

但是,由于所有通道必須進行電氣隔離,可訪問通道的數量取決于適應通道間距的最小導線間距(假設每個通道都有自己的導線)。

基于目前的制造技術(2018年底/2019年初),分區后的通道數量被限制在四個左右:

但是,更寬的堆疊(因需要的狹縫數量少而受用戶歡迎)可能包含四個以上的通道,它們需要被分成多個周期組。

通過使用刻蝕工藝來穿透一部分層,將通道組隔離,有效地使用幾個浮動柵級層作為選擇器晶體管:

支撐列影響分析

由于3D NAND的制造工藝非常復雜,因而我們很難全面理解在存儲容量和穩定性方面的各種權衡因素,以及由于在堆疊中添加更多層、臺階分區、層穿透而導致的其他屬性變化。

以下所示的虛擬工藝模型模擬了建議的制造步驟。我們使用SEMulator3D?來測試不同支撐列數量和接觸通孔尺寸產生的結果。

所添加的列用于在去除階梯層之間的犧牲材料過程中支撐整個結構,它的孔由刻蝕形成,并用二氧化硅填充。

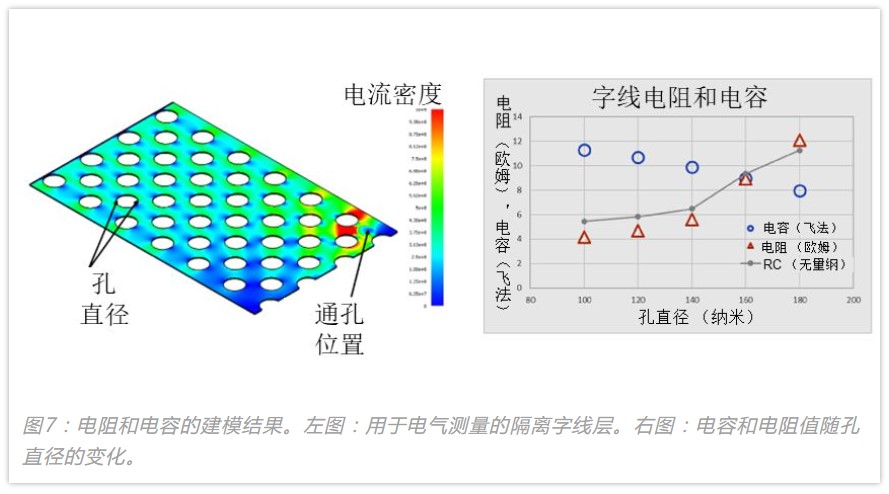

在對Semulator3D模型執行的電氣分析中,我們研究了隔離字線層,并模擬了列尺寸對電阻和字線電容的影響(在右圖中,孔直徑表示列寬度):

擴大支撐列可以提供更好的結構穩定性,但會增加字線電阻,占用更多的空間。

因此,在器件的結構完整性允許的情況下,最大程度地減小支撐列的尺寸和數量對器件結構是有幫助的。

本研究展示了分層3D NAND階梯結構的實際工藝模型。我們還應用了虛擬的制造技術,加深在使用支撐列增強高密度存儲結構穩定性過程中的各種權衡因素的理解。

審核編輯:劉清

-

晶體管

+關注

關注

77文章

9682瀏覽量

138080 -

NAND閃存

+關注

關注

2文章

219瀏覽量

22750 -

固態存儲

+關注

關注

1文章

51瀏覽量

12875

原文標題:3D NAND閃存的存儲密度

文章出處:【微信號:半導體設備與材料,微信公眾號:半導體設備與材料】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

預期提前,鎧俠再次加速,3D NAND準備沖擊1000層

3D NAND的發展方向是500到1000層

【半導體存儲】關于NAND Flash的一些小知識

TechWiz LCD 3D應用:撓曲電效用仿真

3D集成電路的結構和優勢

3D打印在珠寶行業的設計和制造應用-CASAIM

安寶特產品 安寶特3D Evolution:增材制造零件查找器

3D封裝熱設計:挑戰與機遇并存

上海伯東工業級3D打印機為機器人的制造工藝帶來新變革

鎧俠瞄準2027年:挑戰1000層堆疊的3D NAND閃存新高度

尼龍材料3D打印加工服務小批量3D打印模型制作

3D NAND結構給制造過程帶來的挑戰

3D NAND結構給制造過程帶來的挑戰

評論