在MIMXRT1021CAG4B使用中,當系統上電后,發現不同的端口在通電后具有不同的值。例如,現在使用GPIO_EMC_39和喚醒引腳,兩者結果是不同的。從GPIO數據手冊中,GPIO DATA寄存器的復位值為0x00000000。但對于喚醒引腳,復位后狀態后為高電平。

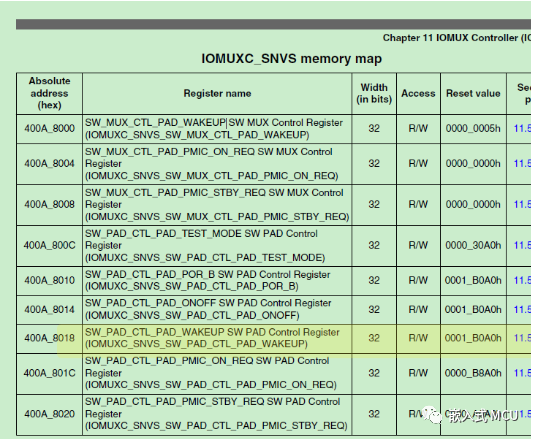

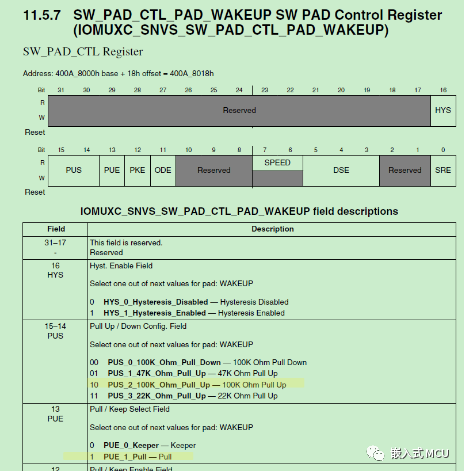

-> GPIO引腳默認為輸入功能,而非輸出功能。因此,它由上拉和下拉配置決定。對于喚醒PIN,可以檢查以下寄存器:

默認情況下,使能了內部100K上拉,因此上電復位后,GPIO口是高電平。針對GPIO_EMC_39 也是一樣的,如果添加DCD將配置SDRAM SEMC端口,它將由SEMC配置結果決定。在從QSPI加載應用程序代碼之前,如下相關信號被驅動為HIGH,為什么呢?

| GPIO_PAD | DEFAULT SIGNAL |

| GPIO_EMC_08 | SEMC_DM00 |

| GPIO_EMC_29 | SEMC_CS0 |

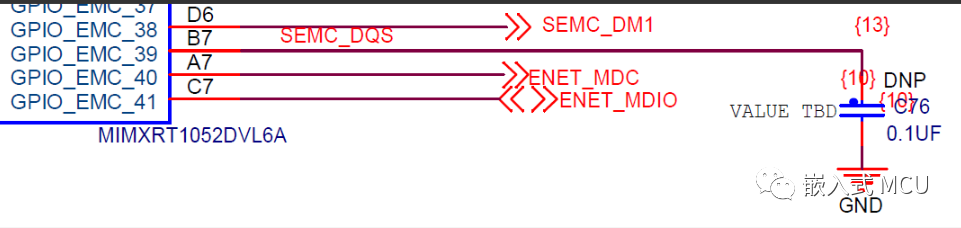

| GPIO_EMC_39 | SEMC_DQS |

問題是,將上述這些信號用作GPIO,并將其用作電機的啟用以及打開/關閉閥門的控制。這些信號具有相當強的下拉電阻,因此認為處理器正在積極地將這些信號配置為輸出并將其驅動為高電平。為什么這些信號在通電時會短暫地切換到高電平,如何防止這種情況發生嗎?

->該問題與DCD配置有關。在RT1020EVK上做了一個快速測試,沒有看到這個問題。可以檢查C76處的電壓以確定GPIO_EMC_39引腳狀態。

還有一種應用場景,需要在固件升級后保留輸出狀態。通常它需要在固件升級后重新啟動,但在重新啟動期間輸出狀態將會被重置。如何實現在固件升級后保持輸出狀態高電平呢?

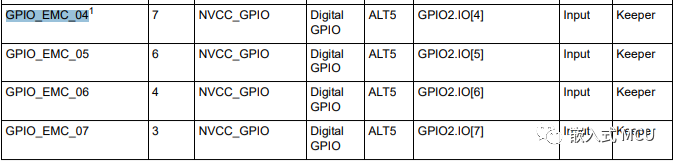

事實上,GPIO輸出狀態由代碼控制,如果更新固件,然后復位,代碼將運行,GPIO狀態完全由代碼控制。但是在復位期間,可以外接上拉電阻,因為,如果引腳是輸入Keeper的,那么它是由外部信號決定的。GPIO_EMC_05和06中的Keeper 電路已啟用,在復位期間將輸出高電平。但對于GPIO_EMC_04,它將在復位期間用作調試 JTAG_ACT功能,它將輸出低電平。

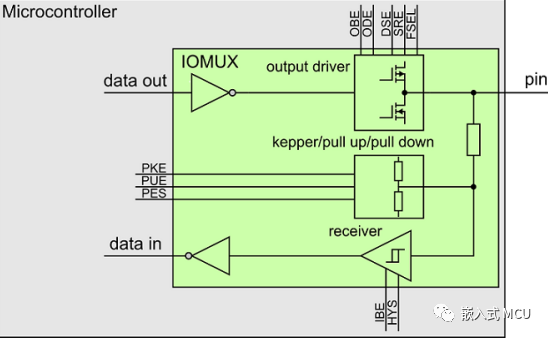

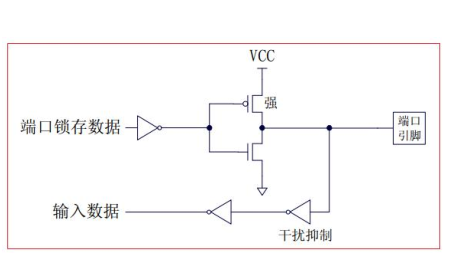

當輸出驅動器被禁用時,Keeper功能夠保持先前的輸出值。

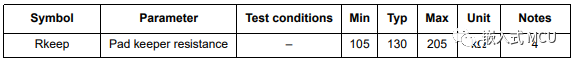

Keeper的內部電阻遠高于標準輸出驅動器的內部電阻——見上表。此選項對于在邏輯值更改時需要大量能量的應用中節省功耗,但在僅需要保持狀態時幾乎不需要消耗能量。另一種類型的應用是必須確保引腳在任何情況下都被驅動,即使強度小得多,因此輸出引腳不會浮空,并且其電平被定義。

pull / keeper 由PKE、PUE和PUS位控制。pull / keeper 可通過pull / keeper 啟用(PKE)位啟用。當pull / keeper 啟用時,可以選擇PUE(上拉啟用)位啟用器件對應的功能。

I2C / I2S 要求雙向通信,如下位在 IOMUX中需要配置:

? 輸入 IBE = 0b1

? 輸出OBE = 0b1

? 開漏功能ODE = 0b1

? 針對低頻信號的配置PKE = 0b1, PUE = 0b1, PUS = 0b11或者外接上拉用于固定的或者高頻信號

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

Data

+關注

關注

0文章

62瀏覽量

38266 -

引腳

+關注

關注

16文章

1193瀏覽量

50412 -

GPIO

+關注

關注

16文章

1204瀏覽量

52052

原文標題:MIMXRT1021CAG4B GPIO口復位值

文章出處:【微信號:嵌入式 MCU,微信公眾號:嵌入式 MCU】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MIMXRT1021和MIMXRT1024 ADC通道數

GPIO寄存器詳解

比較器MIMXRT1020-EVK引腳更改示例問題求解

MIMXRT1021CAG4A無法正常啟動是為什么?

為什么命令flash-erase-region在某些板上會失敗,而在其他板上卻不會?

JTAG引腳是否可以用作該控制器中的GPIO引腳?

如何使用SD卡啟動MIMXRT1024CAG4B?

STC15單片機的GPIO口驅動LED資料合集

【STM32】STM32F4 GPIO八種模式及工作原理詳解

【STM32】STM32F4 GPIO八種模式及工作原理詳解

在MIMXRT1021CAG4B MCU上打印printf()到指定的串口

MIMXRT1064CVL5B連接HyperRAM

MIMXRT1062CVL5B和MIMXRT1062XVN5B的區別

CAG4M-FP-FA 初級用戶手冊 CAG4M-FP-FA V850E/CAG4-M 閃存編程適配器用戶手冊

MIMXRT1021CAG4B GPIO口復位值詳解

MIMXRT1021CAG4B GPIO口復位值詳解

評論