本文通過探討在具有嚴格功耗和成本限制的系統中使用同步解調進行傳感器信號調理的一些設計考慮因素來擴展討論。經過精心設計,模擬系統在簡單、低成本和低功耗方面無與倫比。這種架構在模擬域中執行大部分信號處理。

傳感器激勵

傳感器無處不在,用于測量溫度、光、聲音和各種其他環境參數。一些傳感器充當與參數相關的電壓或電流源。例如,熱電偶產生的電壓與參考結和測量點之間的溫差成正比。大多數傳感器具有傳遞函數,這些傳遞函數遵循與物理參數的已知關系。傳遞函數通常為阻抗,其中電流是傳感器輸入,傳感器兩端的電壓指示感興趣的參數。電阻傳感器(如稱重傳感器、RTD 和電位計)分別用于測量應變、溫度和角度。首先,電阻式傳感器與頻率無關,沒有相位響應。

許多傳感器需要交流激勵信號,因為它們的傳遞函數在頻率和相位上發生變化。示例包括電感式接近傳感器和電容式濕度傳感器。生物特征阻抗測量可以產生有關呼吸頻率、脈搏率、水合作用和許多其他生理參數的信息。在這些情況下,幅度、相位或兩者可用于確定感測參數的值。

在某些應用中,探頭將被測樣品變成傳感器。例如,色度計使用LED將光線照射到被測液體樣品中。樣品的光吸收調節光電二極管檢測到的光量,以揭示被測液體的特征。血氧水平可以通過測量血管組織中紅光和紅外光的光吸收差異來確定。超聲波換能器根據超聲波在氣體中傳播時的多普勒頻移來測量氣體流速。所有這些系統都可以使用同步解調來實現。

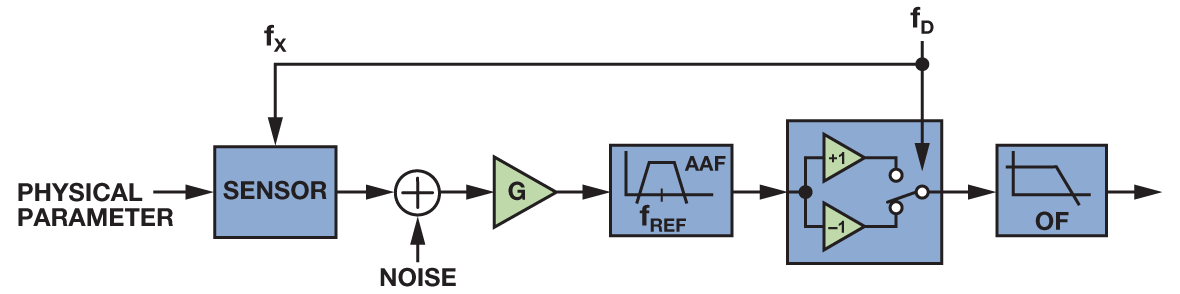

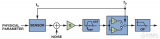

圖1所示為用于測量傳感器輸出信號的同步解調系統。激勵信號,fx,充當載波,傳感器根據被測參數的幅度、相位或兩者進行調制。信號可以放大和濾波,然后由相敏檢波器(PSD)調制回直流。輸出濾波器(OF)將信號的帶寬限制在被測參數的頻率范圍內。

圖1.同步解調系統。

傳感器輸出端的噪聲可能是由內部源或外部耦合引起的。低頻(1/f)噪聲通常會限制傳感器或測量電子設備的性能。許多傳感器也容易受到低頻環境噪聲的干擾。光學測量容易受到背景光的影響,電磁傳感器容易受到電源輻射的影響。自由選擇激勵頻率以避免噪聲源是同步解調的一個關鍵優勢。

選擇能夠降低這些噪聲源影響的激勵頻率是優化系統性能的重要方法。所選的激勵頻率應具有低本底噪聲,并且距離噪聲源足夠遠,以便適度的輸出濾波可以將噪聲降低到可接受的水平。傳感器激勵通常是功率預算中最大的項目。如果傳感器的靈敏度與頻率的關系已知,則可以通過以靈敏度較高的頻率激勵傳感器來降低功耗。

相敏檢測器

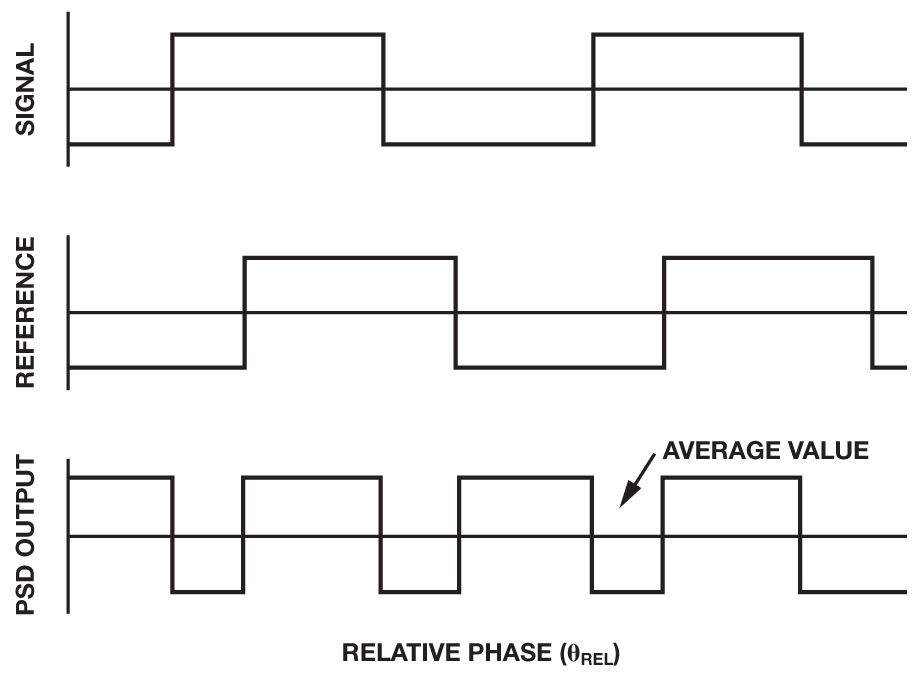

了解抗混疊濾波器(AAF)和OF的要求需要了解PSD。考慮一個PSD,它使用激勵信號將輸入信號同步乘以+1和–1。這相當于將輸入信號乘以相同頻率的方波。圖2a顯示了輸入信號、基準電壓源和PSD輸出的時域波形,其中輸入信號是相對于基準電壓源具有任意相位的方波。

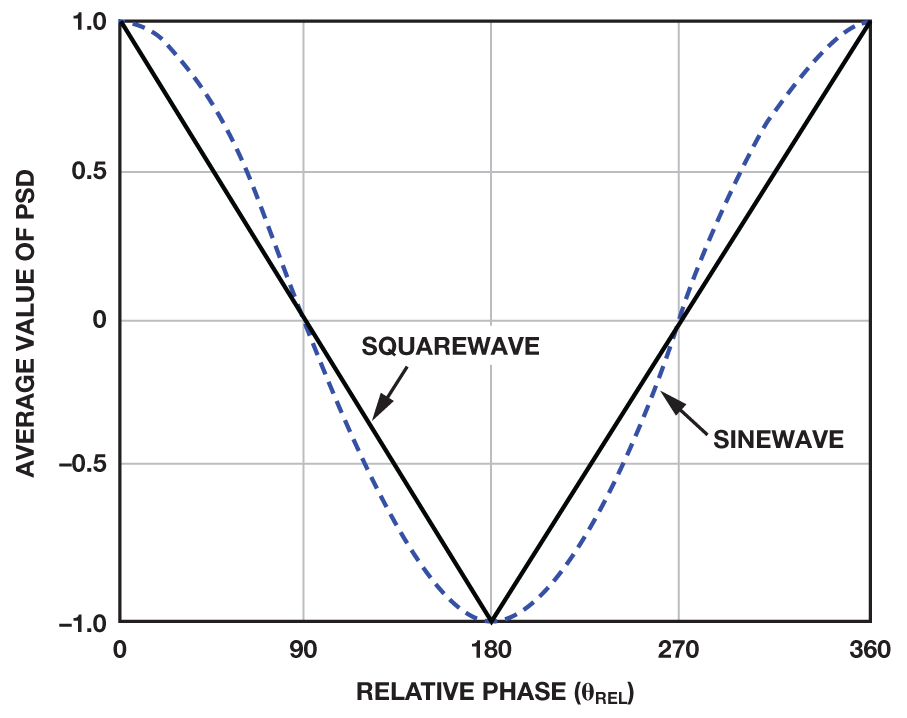

當輸入和基準完全同相時,相對相位為0°,開關輸出為直流,PSD輸出電壓為+1。隨著相對相位的增加,開關輸出變為參考頻率兩倍的方波,占空比和平均值線性減小。在相對相位為90°時,占空比為50%,平均值為0。在相對相位為180°時,PSD輸出電壓為–1。圖2b顯示了方波和正弦波輸入信號的相對相位從0°掃描到360°時PSD的平均輸出值。

圖2.(a) 私營部門司的時域波形。

(b) 私營部門司產出作為相對相位函數的平均值。

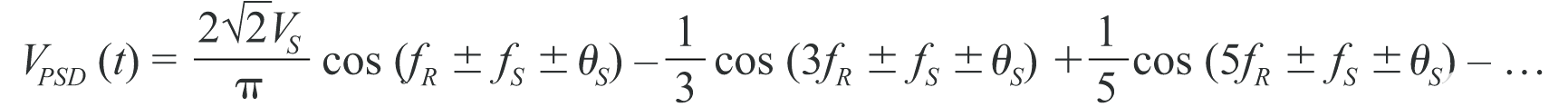

正弦波情況不如方波情況直觀,但可以通過逐項相乘并分為和差分量來計算,如下所示:

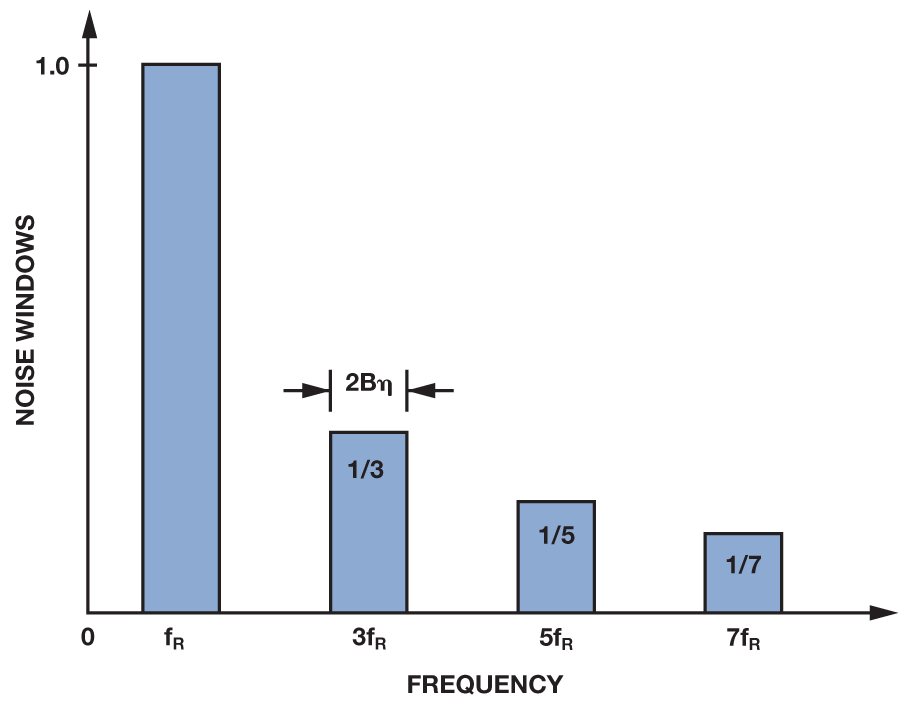

根據需要,PSD產生與基頻下輸入信號相對相位的余弦成比例的響應,但它也產生對信號的每個奇次諧波的響應。由于輸出濾波器被認為是相敏檢波器的一部分,信號傳輸路徑看起來像一系列以參考信號的奇次諧波為中心的帶通濾波器。帶通濾波器的帶寬由低通輸出濾波器的帶寬決定。PSD輸出響應是這些帶通濾波器的總和,如圖3所示。直流處出現的響應部分落在輸出濾波器的通帶內。在參考頻率的偶次諧波處出現的響應部分將被輸出濾波器抑制。

圖3.有助于PSD輸出的信號輸入頻譜。

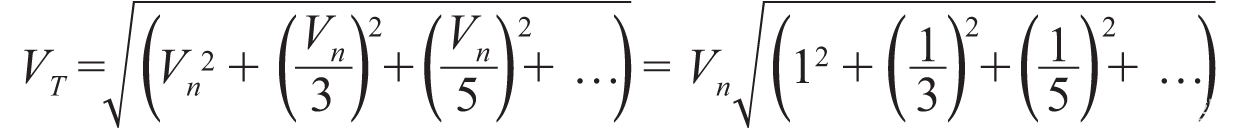

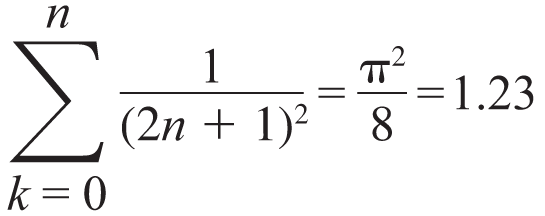

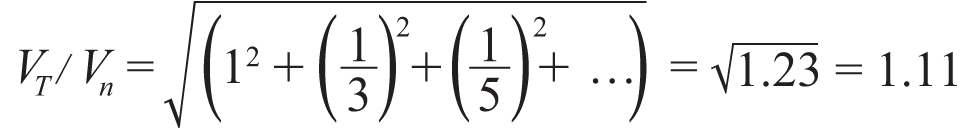

乍一看,輸出濾波器通帶中無限的諧波混疊似乎注定了這種方法的失敗。但是,噪聲混疊的影響得到了緩解,因為每個諧波項都按遞減因子縮放,并且各種諧波處的噪聲相加為平方根和。假設輸入信號的噪聲頻譜密度恒定,我們可以計算諧波混疊的噪聲影響。

讓 Vn是以基頻為中心的傳輸窗口中的積分噪聲。總均方根噪聲,VT是

使用一個方便的公式來計算幾何級數的總和,該公式指出

諧波窗口引起的均方根噪聲增加為

因此,所有諧波窗口引起的均方根噪聲僅使總噪聲增加11%或1 dB。輸出仍然容易受到帶通濾波器通帶中的干擾因素的影響,PSD之前傳感器或電子設備的諧波失真會導致輸出信號誤差。如果這些諧波失真項大得令人無法接受,則可以使用抗混疊濾波器來減少它們。以下設計示例將考慮抗混疊和輸出濾波器的要求。

LVDT設計示例

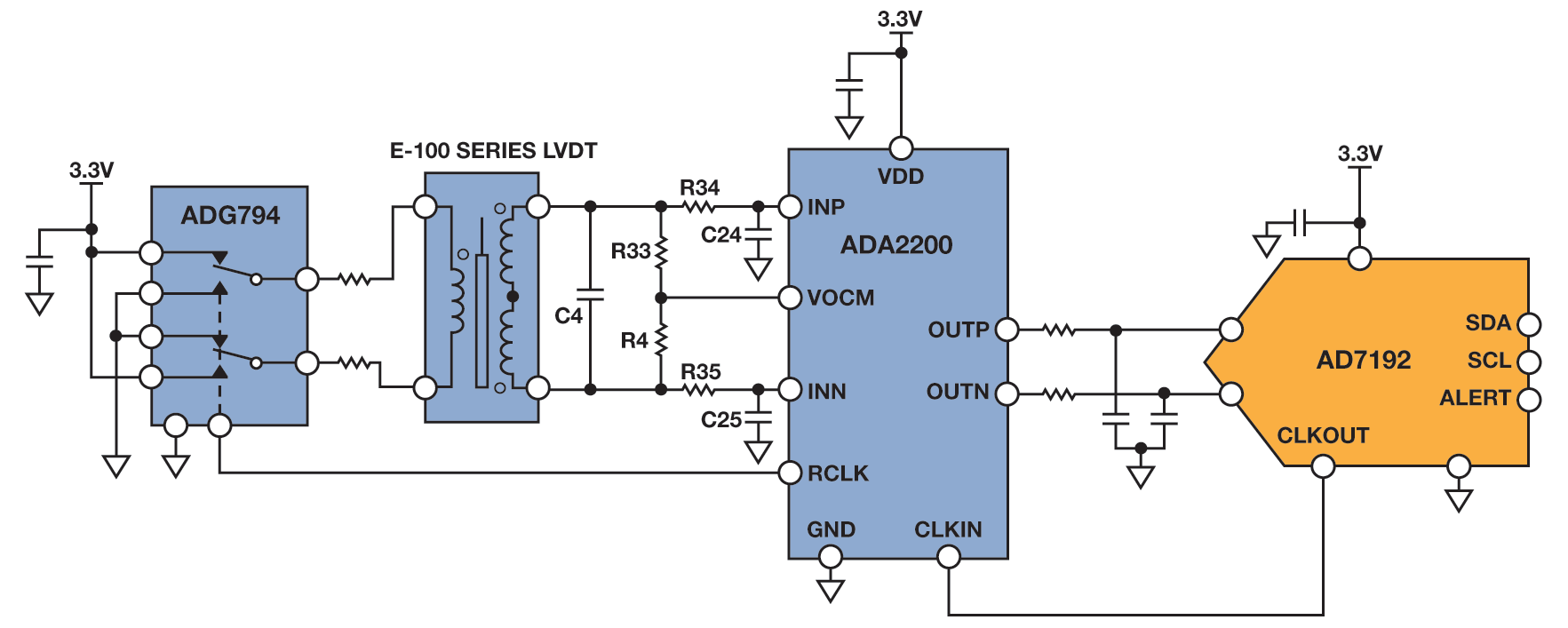

圖4顯示了一個同步解調電路,該電路從線性可變位移變壓器(LVDT)中提取位置信息,LVDT是一種特殊繞組的變壓器,具有固定在待測位置上的可移動磁芯。激勵信號施加到初級。次級上的電壓與磁芯的位置成比例變化。

LVDT有許多類型以及從中提取位置的方法。該電路在4線模式下使用LVDT。兩個LVDT次級輸出連接,使電壓相互對立,執行減法。當LVDT磁芯處于零位置時,次級上的電壓相等,繞組兩端的差電壓為零。當磁芯從零點位置移動時,次級繞組兩端的壓差增加。LVDT輸出電壓的符號隨方向而變化。本例選擇的LVDT測量±2.5mm的滿量程磁芯位移。電壓傳遞函數為0.25,這意味著當磁芯從中心位移2.5 mm時,施加到初級端的差分輸出將為每伏250 mV。

圖4.簡化的LVDT位置檢測電路。

集成同步解調器

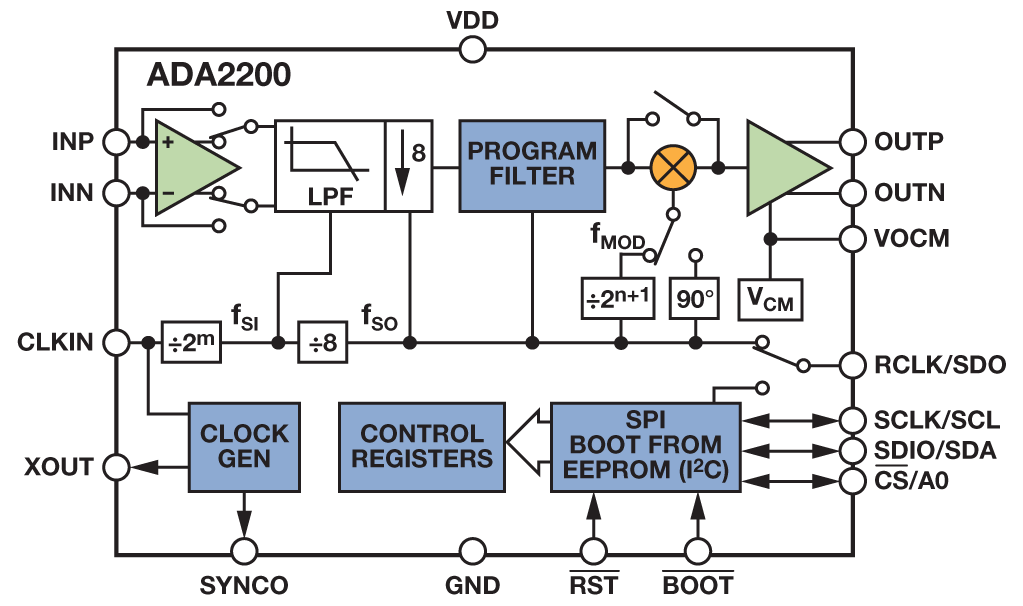

ADA2200集成同步解調器采用獨特的電荷共享技術,在模擬域中執行離散時間信號處理。其信號路徑由輸入緩沖器、執行抗混疊濾波的FIR抽取濾波器、可編程IIR濾波器、相敏檢波器和差分輸出緩沖器組成。其時鐘生成功能將激勵信號與系統時鐘同步。可編程功能通過SPI兼容接口進行配置。

圖5.ADA2200同步解調器

24位Σ-Δ型ADC產生的4.92 MHz時鐘用作主時鐘。ADA2200產生為濾波器和PSD計時所需的所有內部信號,以及在RCLK引腳上生成激勵信號。它將主時鐘除以 1024,以產生 4.8kHz 信號來控制 CMOS 開關。CMOS 開關將低噪聲 3.3V 源轉換為 LVDT 的方波激勵信號。用于激勵源的 3.3V 電源也用作 ADC 基準電壓源,因此電壓源中的任何漂移都不會降低測量精度。在滿量程位移時,LVDT將輸出1.6 V峰峰值輸出電壓。

抗鋸齒濾波

LVDT輸出和ADA2200輸入之間的RC網絡提供LVDT輸出信號的低通濾波,并產生最大化解調器輸出信號所需的相對相移。回想一下圖2b,最大PSD輸出是如何在0°或180°的相對相移時發生的。ADA2200具有90°相位控制功能,也可使用±90°相對相位偏移。

解調頻率的奇數倍處的信號能量將出現在輸出濾波器的通帶中。FIR抽取濾波器實現抗混疊濾波,在這些頻率下提供至少50 dB的衰減。

如果需要,IIR濾波器可以提供額外的濾波或增益。由于IIR濾波器位于相敏檢波器之前,其相位響應將影響PSD信號輸出帶寬。在設計濾波器響應時必須考慮到這一點。

輸出濾波器

應選擇輸出濾波器的通帶,使其與被測參數的帶寬相匹配,但要限制系統的寬帶噪聲。輸出低通濾波器還必須抑制在PSD的偶數倍處產生的輸出雜散。

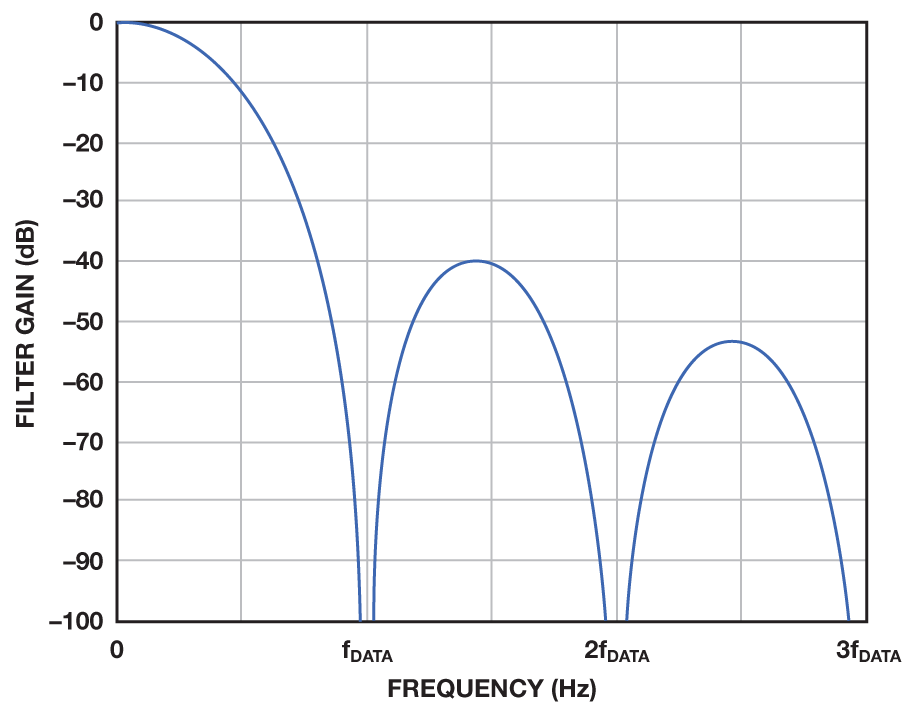

本電路使用AD7192 Σ-Δ型ADC固有的LPF。它可以被編程為具有 sinc。3或 sinc4響應,傳遞函數以輸出數據速率的倍數歸零。圖 6 顯示了 sinc3傳遞函數歸一化為ADC輸出數據速率。

將ADC的輸出數據速率設置為等于解調頻率,可抑制PSD輸出端的雜散。ADC的可編程輸出數據速率充當可選帶寬輸出濾波器。可用的輸出數據速率(f數據) 為 4.8 kHz/n,其中 1 ≤ n ≤ 1023。因此,ADC針對每個輸出數據值在n個解調時鐘周期內對解調器輸出求平均值。由于主時鐘和ADC時鐘是同步的,ADC輸出濾波器的傳遞函數零點將直接落在調制頻率的每個諧波上,并且對于n的任何值,所有輸出雜散都將被抑制。

圖6.AD7192 sinc3濾波器傳遞函數

可編程輸出數據速率可在噪聲和帶寬/建立時間之間進行直接權衡。輸出濾波器的噪聲帶寬為0.3 × f數據;3 dB 頻率:0.272 × f數據;和 3/F 的建立時間數據.

ADC數字濾波器在4.8 kHz的最高輸出數據速率下具有約1.3 kHz的3 dB帶寬。解調器和ADC之間的RC濾波器在該頻率下相對平坦,以最大限度地降低ADC所需的帶寬。在最大數據速率較低的系統中,RC濾波器轉折頻率可以成比例地降低。

噪聲性能

電路的輸出噪聲是ADC輸出數據速率的函數。表1顯示了數字化數據中的有效位數與ADC采樣速率的關系,假設滿量程輸出電壓為2.5 V。噪聲性能與LVDT磁芯位置無關。

表 1.噪聲性能與帶寬的關系

| 模數轉換器數據速率 | 輸出帶寬(赫茲) | ENOB (rms) | ENOB (p-p) |

| 4800 | 1300 | 13.8 | 11.3 |

| 1200 | 325 | 14.9 | 12.3 |

| 300 | 80 | 15.8 | 13.2 |

| 75 | 20 | 16.2 | 13.5 |

如果ADA2200的輸出噪聲與頻率無關,則輸出數據速率每降低4×,預期有效位數將增加一位。由于ADA2200輸出驅動器的1/f噪聲在較低的輸出數據速率下,ENOB不會增加太多,在較低的輸出數據速率下,該噪聲開始主導本底噪聲。

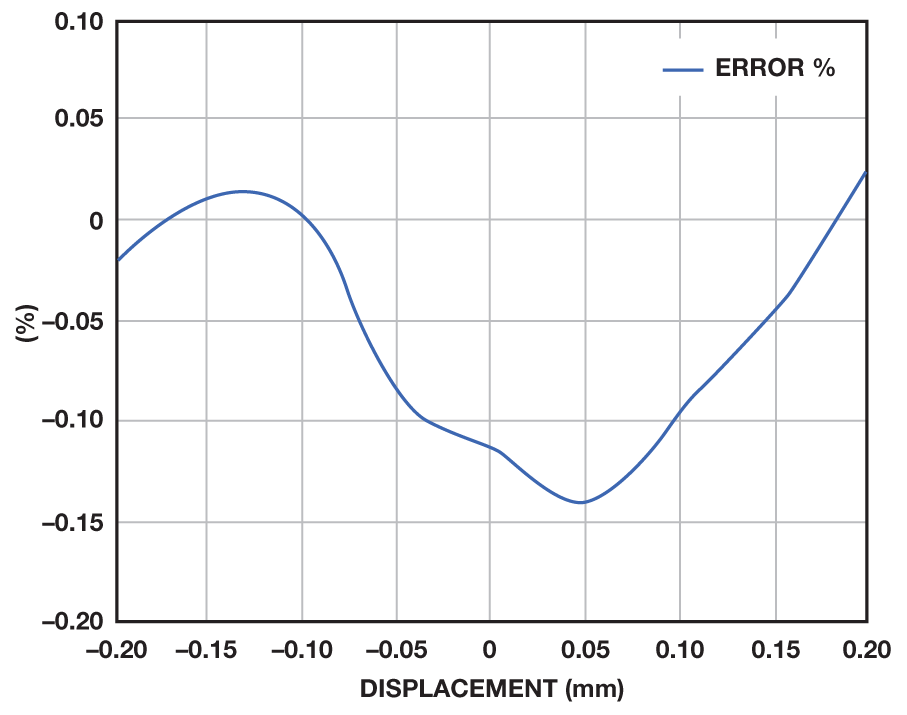

線性

通過首先在±2.0 mm的磁芯位移下執行兩點校準來測量線性度。根據這些測量結果,確定了斜率和偏移量,以建立最佳直線擬合。接下來,在±2.5毫米滿量程范圍內對磁芯位移進行測量。從直線數據中減去測量數據以確定線性誤差。

圖7.位置線性誤差與LVDT磁芯位移的關系。

用于電路評估的 E 系列 LVDT 在 ±2.5mm 位移范圍內指定了 ±0.5% 的線性度。電路性能超過LVDT規格。

功耗

該電路的總功耗為10.2 mW,其中驅動LVDT的功率為6.6 mW,其余部分為3.6 mW。通過增加LVDT激勵信號,可以提高電路SNR,但代價是功耗增加。或者,可以通過降低LVDT激勵信號并使用低功耗、雙通道運算放大器放大LVDT輸出信號以保持電路的SNR來降低功耗。

結論

許多傳感器信號調理挑戰都具有可以通過同步解調解決的特性。激勵頻率低于1 MHz且動態范圍要求在80 dB至100 dB范圍內的系統可以通過低成本、低功耗模擬電路來解決,只需最少的數字后處理。了解相敏檢波器的工作原理以及傳感器輸出端可能的噪聲特性是確定系統濾波器要求的關鍵。

審核編輯:郭婷

-

傳感器

+關注

關注

2550文章

51035瀏覽量

753083 -

解調器

+關注

關注

0文章

286瀏覽量

25812 -

運算放大器

+關注

關注

215文章

4929瀏覽量

172839

發布評論請先 登錄

相關推薦

教你設計低成本、低功耗的同步解調器

低功耗同步解調器設計考慮因素

低功耗同步解調器設計注意事項

低功耗同步解調器設計注意事項

評論