作者:Michal Brychta and Derrick Hartmann

4 mA至20 mA模擬電流環路常見于加工廠和工廠環境。雖然兩種環境中的基本信令相同,但帶寬要求卻大不相同。工廠控制系統可能需要位置和位移傳感器的環路帶寬為 100 Hz。另一方面,典型的過程控制系統只需要幾赫茲的更新速率,并且通常啟用HART。HART(高速可尋址遠程傳感器)協議允許在傳統的模擬 4 mA 至 20 mA 電流環路上進行雙向 1.2 kHz/2.2 kHz FSK(頻移鍵控)調制數字通信。設計滿足這兩種情況的4 mA至20 mA輸入可能具有挑戰性。本文概述了一種大大簡化此類設計的方法。

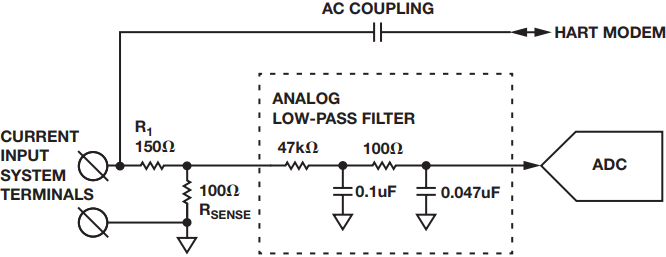

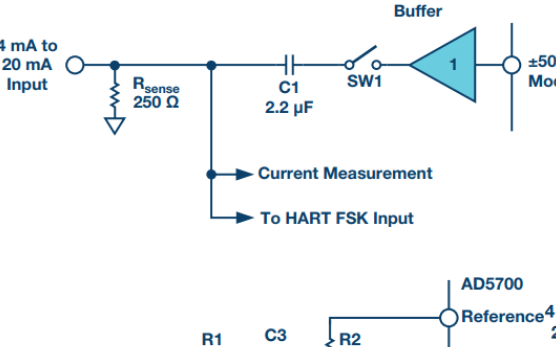

圖1中的電路圖顯示了實現HART模擬輸入的傳統方法。

圖1.帶無源濾波器的HART使能輸入。

R1和 R意義提供 250 Ω 的系統終端阻抗。HART FSK信號從那里交流耦合到HART調制解調器。4 mA 至 20 mA 模擬信號由精密 100 Ω R 轉換意義電阻至0.4 V至2 V電壓信號。然后,模擬低通濾波器從模擬信號中衰減HART FSK組件,然后再將其傳遞到ADC。二階低通模擬濾波器的帶寬為25 Hz,滾降為–40 dB/十倍頻程。

該電路符合HART規范,可將HART FSK信號衰減至低于4 mA至20 mA滿量程的–60 dB以上,確保HART FSK通信對4 mA至20 mA模擬輸入的干擾小于0.1%。

另一方面,該模擬低通濾波器在系統輸入滿量程步進后需要近70 ms才能在0.1%以內建立。長建立時間和低帶寬不適用于需要快速操作且不需要HART通信的系統。模擬濾波器確實可以繞過,但這需要額外的模擬電路,例如開關或多路復用器。

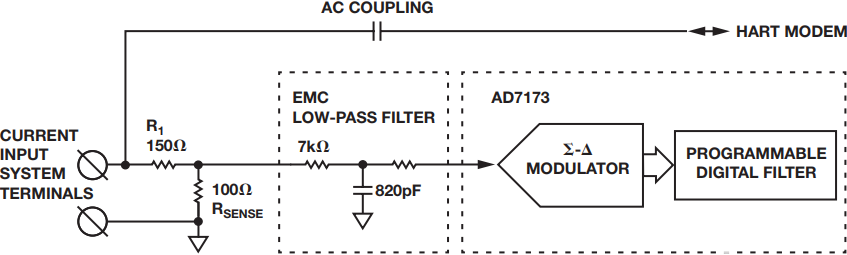

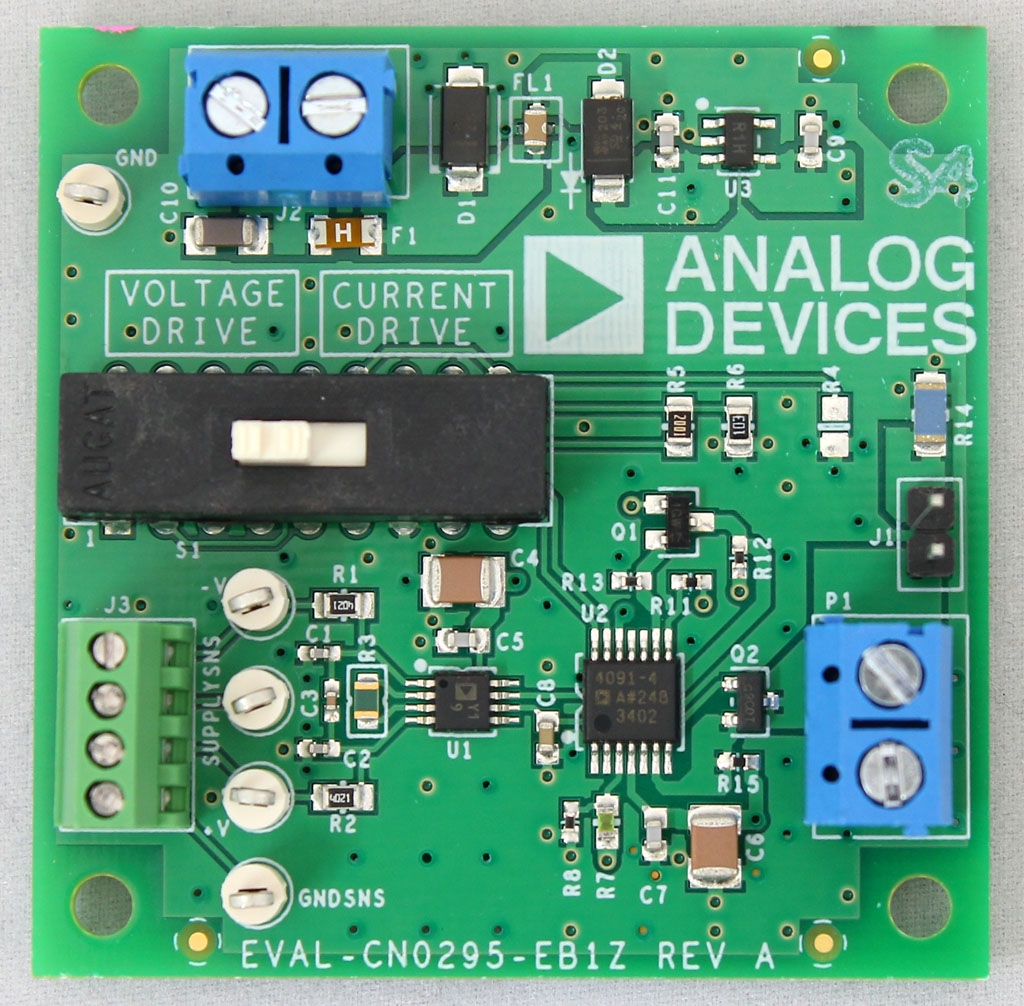

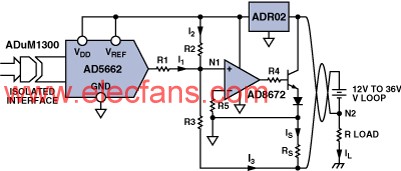

圖2顯示了啟用HART的模擬輸入的另一種方法。

圖2.支持HART,靈活的帶寬輸入。

與前一個電路類似,HART FSK信號由250 Ω輸入阻抗交流耦合,4 mA至20 mA模擬信號由精密100 Ω R轉換。意義電阻至0.4 V至2 V電壓信號。然而,在該電路中,一個相當輕的低通濾波器將信號帶寬限制在27 kHz左右,只是為了提供系統抗擾度和電磁兼容性(EMC)。在系統輸入端進行滿量程步進后,濾波器在40 μs內建立至0.1%。

該信號通過內置數字濾波器傳遞到∑?ADC,例如ADI公司的AD7173。數字濾波器可以編程為較慢的操作和最佳的HART FSK信號抑制,或者在需要快速模擬輸入功能時快速操作。

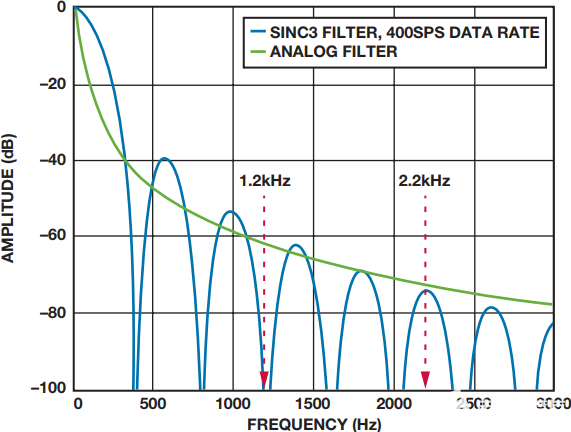

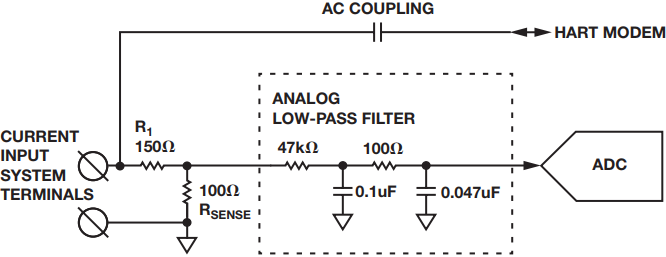

AD7173數字濾波器具有多種工作模式。適合抑制HART FSK信號的模式之一是陷波設置為400 Hz或子倍的sinc3濾波器,它在1.2 kHz的較低HART FSK頻率下提供深濾波器陷波,在2.2 kHz的較高頻率下提供顯著衰減。圖3中的圖表顯示了該數字濾波器的頻率響應及其與圖1模擬濾波器的比較。

圖3.帶無源濾波器的HART使能輸入。

不幸的是,現實世界并沒有那么簡單。當通過HART發送完整的消息時,HART FSK調制信號頻譜不僅包含基本調制頻率的能量,而且還包含介于1.2 kHz和2.2 kHz載波之間、低于和高于1.2 kHz的分量。

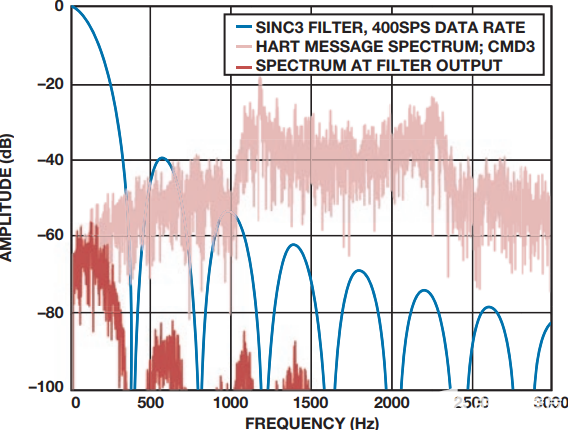

圖4顯示了ADC輸入端HART FSK消息的典型頻譜,以及被具有400 Hz陷波的sinc3濾波器衰減時的頻譜。在這種情況下,主站正在發送HART命令3,而從站正在響應該命令。

圖4.哈特消息譜。

從這個圖中可以明顯看出,HART消息的一部分,特別是在較低頻率下,仍然可以存在于模數輸出數據中。也就是說,可以輕松更改數字濾波器設置,以在4 mA至20 mA輸入速度和HART FSK信號抑制之間設置適當的平衡。

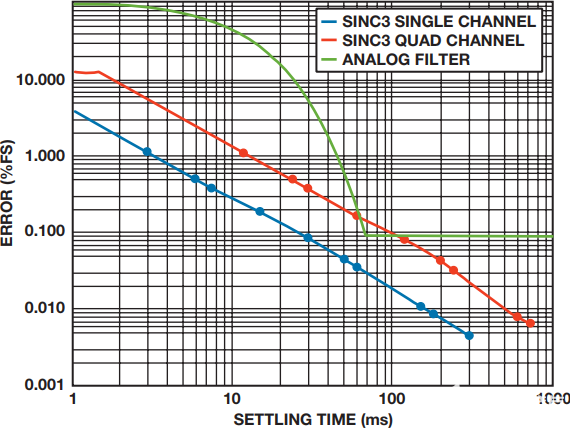

圖5顯示了系統性能,以相對于4 mA至20 mA滿量程的百分比誤差與模擬濾波器(如圖1所示)和sinc3數字濾波器(如圖2所示)的系統速度的關系。

圖5.Sinc3濾波器與模擬濾波器。

模擬濾波器固定在硬件中,并具有固定的建立時間。對于系統輸入端的快速變化模擬信號,模擬濾波器輸出誤差主要取決于其緩慢建立。例如,如果系統輸入每40 ms改變一次滿量程,則濾波器輸出的建立速度不會接近正確值的1%。對于慢速輸入信號,模擬濾波器輸出誤差主要取決于其抑制HART FSK信號的低頻分量的能力。對于典型的HART命令3消息,該誤差約為4 mA至20 mA滿量程的0.09%。

另一方面,數字sinc3濾波器的建立時間是用戶設置的參數,由HART FSK信號引起的濾波器輸出誤差與濾波器設置相對應。例如,前面討論的具有400 Hz陷波的sinc3濾波器對應于7.5 ms的建立時間,當與HART命令3通信時,模數結果中測得的干擾小于4 mA至20 mA滿量程的0.4%。在具有四個模擬輸入的系統中,sinc3濾波器在通道之間按順序切換。具有 400 Hz 陷波的相同 sinc3 濾波器現在需要 4 × 7.5 = 30 ms 來掃描所有四個通道。這就是為什么該圖在30 ms時顯示4通道系統相同的~0.4%誤差。

對于更精確的4 mA至20 mA輸入,sinc3濾波器可以設置為30 ms建立,對應于100 Hz陷波,并將HART信號抑制到滿量程的0.1%以下。如果系統中更重視速度,則建立時間為6 ms(~500 Hz陷波)的sinc3濾波器仍可抑制低于4 mA至20 mA滿量程0.5%的HART通信信號。如果速度是唯一要求且不需要HART通信,則本例中使用的AD7173可以采樣超過31 kSPS,每通道建立時間為161 μs。

總之,傳統的模擬低通濾波器更容易理解,而且,對于電路板上每個通道多幾個元件的價格,在某些情況下,在多通道系統中實現時可能會提供更好的模擬輸入性能。另一方面,集成在∑?ADC上的數字sinc3濾波器具有極大的靈活性,可以一直提供給終端系統用戶。數字解決方案需要較少的硬件,如果設置得當,其在濾波HART FSK信號方面的性能明顯優于單通道系統中的模擬解決方案,并且在多達4通道系統中具有可比性或更好。

審核編輯:郭婷

-

傳感器

+關注

關注

2550文章

51035瀏覽量

753077 -

濾波器

+關注

關注

161文章

7795瀏覽量

177994 -

調制解調器

+關注

關注

3文章

854瀏覽量

38803

發布評論請先 登錄

相關推薦

具有HART的完全隔離、單通道電壓、4mA至20mA輸出電路圖

靈活的4mA至20mA壓力傳感器變送器,集成電壓或電流驅動

利用HART兼容性簡化模擬電流環路設計

基于HART兼容性簡化模擬電流環路設計

高精度環路供電式4mA至20mA現場變送器包括BOM及層圖

4mA–20mA Loop Powered Temperat

ADI實驗室電路:完整的HART兼容型4mA至20mA解決方案

支持HART的電流輸入以及與向余量受限的4mA至20mA輸入設計中添加HART功能

由 4mA 至 20mA 電流環路提供的 7.4mA DC 電源

AD5410/AD5420:單通道、12/16位、串行輸入、4mA至20mA 電流源DAC

靈活的帶寬4mA至20mA電流輸入具有輕松的HART兼容性

靈活的帶寬4mA至20mA電流輸入具有輕松的HART兼容性

評論