本應用筆記描述了低頻振蕩器設計和晶體選擇如何影響工作電流。當振蕩器采用容量有限的電源(如紐扣鋰電池或超級電容器)運行時,最小化工作電流會增加工作時間。

介紹

Maxim擁有豐富的低功耗、電池備份實時時鐘(RTC)產品組合。Maxim設計RTC時,主要考慮因素是當RTC采用備用電源供電時,將振蕩器的功耗要求降至最低,從而最大限度地延長備份電源的使用壽命。晶體振蕩器提供合理的精度,多年來的開發工作一直專注于最小化功耗。

振蕩器設計目標包括:

提供足夠的電流和增益來啟動和維持振蕩

提供寬工作電壓范圍

將外部噪聲對精度的影響降至最低

關鍵晶體和振蕩器參數

圖1顯示了晶體諧振器的等效電路。晶體有兩個零相位的頻率,如圖2所示。較低的頻率是串聯諧振頻率。在串聯諧振頻率下,L1和C1抵消,阻抗由R1確定。 第二個更高的頻率是并聯諧振頻率。在并聯共振時,電阻最大。

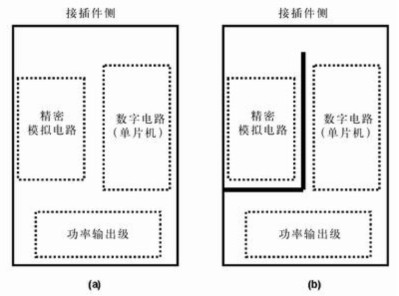

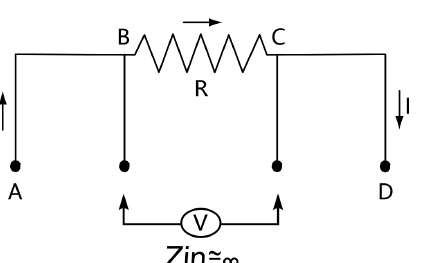

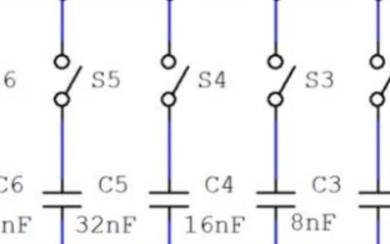

并聯諧振振蕩器電路(圖3)使用設計為在指定負載電容下工作的晶體。這導致電路在串聯諧振點和并聯諧振點之間的頻率下工作。負載電容的變化會導致振蕩器頻率的變化。

晶體等效串聯電阻(ESR)在經過SMT回流焊后趨于向上移動,因此與通孔封裝晶體相似的SMT晶體可能具有更高的最大ESR規格。同樣,較小的音叉晶體通常比較大的音叉晶體具有更高的ESR規格。

圖1.晶體諧振器的等效電路。

圖2.晶體相位和阻抗響應。

圖3.穿孔型(逆變器變化)振蕩器電路。

振蕩器電流

正如 Eric Vittoz 所觀察到的,當晶體振蕩器電路(圖 3)中的兩個負載電容值相等時,振蕩(或臨界跨導)的最小電流可以用下面的公式近似。

| g麥克利特≈ 4Ω2 × CL2 × R紅沉降率 | (公式1) |

其中 ω 是以弧度為單位的頻率,CL為等效容性負載,R紅沉降率是晶體的ESR。假設振蕩器是弱反轉工作的CMOS器件。

Vittoz 還確定振蕩器幅度和偏置電流由以下公式相關:

|

(公式2) |

我在哪里

B0和我B1是零階和一階修改的貝塞爾函數。

因此,我們可以顯示給定振蕩器電壓下振蕩器電流與不同ESR和C值之間的關系L,如以下示例所示。假設 V1= 400mVP-P紐T= 26mV,ESR = 35kΩ,CL= 6pF,然后

≈ 4,然后

IO≈ 4Ω2 × CL2 × R紅沉降率× nUT× 4

≈ 4 × (32,768 × 6.283)2 × (6e-12)2 × 35e+3 × 0.026 × 4

≈ 22.2nA。

表 1 顯示了兩個 C 之間的關系L和振蕩器電流上的 ESR,使用 V 的值1和 nUT以上。

表 1.晶體 ESR 和 CL與振蕩器電流的比較

| ESR (Ω) | CL(pF) | IO(nA) |

| 35,000 | 6 | 22.2 |

| 70,000 | 6 | 44.4 |

| 35,000 | 12.5 | 88.9 |

| 70,000 | 12.5 | 177.8 |

由于在g的方程中麥克利特該 CL項為平方,負載電容加倍具有使振蕩器電流增加四倍的效果。將晶體ESR提高兩倍會導致所需的振蕩器電流加倍。請注意,這是估計的最小振蕩器電流,不包括用于放大振蕩器輸出的附加電路消耗的電流,也不包括用于將頻率分頻至1Hz的器件中的電流。

振蕩器設計要求

振蕩器的設計應使其具有足夠的增益,可以在整個工作溫度和電壓范圍內工作。在工作條件下,幅度必須始終足以驅動以下增益和緩沖級。為了最小化振蕩器電流要求,對于給定的振蕩電壓,低CL是需要的。下 CL但是,會增加振蕩器對外部噪聲影響的敏感性。低 C 的可用性差L晶體可以選擇具有更高C的晶體L必要的,但代價是振蕩器電流增加。同樣,如果設計需要小型晶體封裝,則需要驅動高ESR晶體的振蕩器設計,從而增加必要的振蕩器電流。

此外,用于添加所需功能的電路,例如用于提高振蕩器抗擾度的毛刺濾波器,或用于檢測振蕩器何時停止的電路,都會增加電路的總電流消耗。

結論

在為低功耗RTC設計振蕩器時,需要考慮許多權衡。增加 CL將提高抗噪性,并可能提供更多的晶體型號可供選擇,但代價是振蕩器電流。同樣,設計振蕩器以使其以相對較高的ESR晶體運行需要更高的振蕩器電流。增加毛刺濾波器或振蕩器停止檢測電路也增加了有益的功能,但會消耗額外的電流。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17769瀏覽量

250739 -

電容器

+關注

關注

64文章

6228瀏覽量

99846 -

振蕩器

+關注

關注

28文章

3839瀏覽量

139167

發布評論請先 登錄

相關推薦

選用晶體振蕩器注意事項

振蕩器的使用方法 振蕩器的注意事項

PIC32MX器件的輔助振蕩器(SOSC)晶振設計注意事項

低電流應用的振蕩器設計注意事項

低電流應用的振蕩器設計注意事項

評論