MAX2769C ADC輸出支持兩種類型的基帶接口:默認模式和DSP接口模式。本應用筆記討論如何為DSP接口模式配置ADC寄存器。默認模式配置請參考MAX2769C數據資料。

介紹

MAX2769C是全球導航衛星系統(GNSS)接收器,在單芯片上集成GPS、GLONASS、伽利略和北斗導航衛星系統。這款單轉換 GNSS 接收器旨在為工業應用和廣泛的消費類應用(包括移動手機)提供高性能。

MAX2769C包括一個片內ADC,用于對下變頻GNSS信號進行數字化處理。ADC輸出CMOS邏輯電平,I和Q通道均具有一個或兩個量化位,I通道最多為三個量化位。還提供I和Q模擬輸出,可旁路片內ADC。

當使用ADC時,MAX2769C支持兩種類型的基帶接口:

在默認模式下,I和Q采樣分別在I0和I1輸出以及Q0和Q1輸出上輸出。用戶可以選擇寄存器配置使用每個I和Q樣本的位數。每個CLK_OUT周期的I和Q輸出上輸出一個樣本。

在DSP接口模式下,多達4位可以多路復用到單個輸出上。

MAX2769C數據資料僅詳細解釋默認模式。本應用筆記說明如何配置DSP接口模式所需的寄存器。

DSP 接口模式

概述

DSP接口有兩個目的。首先,DSP接口將ADC數據組裝成幀,這些幀通過幀號在每個幀的開頭插入時序信息。其次,DSP接口為多位ADC數據輸出情況下的數據序列化提供了一種手段。

幀計數器的值作為時間戳插入到每個幀開頭的數據流中。DIEID 代碼的 2 位和STRM_BITS字的 2 位前綴為 28 位長的幀號,使得幀(時間戳)的總長度為 32 位,位于每個幀的開頭。

在幀戳位之后,GPS 數據被序列化為位 0 的 16 位段,后跟位 1、位 2 和位 3。要序列化的位數由STRM_BITS字控制,該字在 1 位、2 位和 4 位大小寫之間進行選擇。

描述

片內多位ADC對下變頻GPS信號進行數字化處理,并將數據輸出為四個邏輯信號(位0、位1、位2、位3),分別代表I和/或Q通道中的符號/幅度、無符號二進制或二進制補碼二進制數據。有關數據格式的詳細說明,請參閱IC數據手冊。

ADC的分辨率最多可設置為每通道3位。例如,符號/幅度格式的 2 位 I 和 Q 數據映射如下:位 0 = Sign_I,位 1 = Mag_I,位 2 = Sign_Q,位 3 = Mag_Q。

數據可以序列化為位 0 的 16 位段,后跟位 1、位 2 和位 3。要序列化的位數由STRM_BITS字控制,該字在位 0、位 0 和位 1、位 0 和位 2、位 0、位 1、位 2 和位 3 大小寫之間進行選擇。

如果僅序列化位 0,則數據流僅包含位 0 數據。如果選擇了位 0 和位 1(或位 2)的序列化,則流數據模式由 16 位位 0 數據后跟 16 位位 1(或位 2)數據組成,后者后跟 16 位位 0 數據,依此類推。在這種情況下,串行時鐘的速度必須至少是ADC時鐘的兩倍。

如果選擇位 0、位 1、位 2、位 3 的 4 位串行,則串行時鐘必須至少比 ADC 時鐘快 4 倍。

如果使用小數時鐘分頻器,則串行(CLK_SER)和ADC (CLK_ADC)時鐘之間的瞬時分頻比在小數時鐘分頻器的控制下連續變化。例如,如果小數時鐘周期等于串行時鐘周期的 4.5 倍,則通過一系列交替的 /4 和 /5 周期實現 4.5 的平均分頻比。

ADC數據并行加載到四個保持寄存器中,這些保持寄存器對應于四個ADC輸出。保持寄存器的長度為16位,由ADC時鐘計時,ADC時鐘是從小數分頻器輸出獲取的時鐘。在16位ADC周期結束時,數據被傳輸到四個移位寄存器,并在下一個16位ADC周期內串行移位至輸出。移位寄存器由串行時鐘計時,該串行時鐘必須足夠快,以便在從ADC加載下一組數據之前將所有64 = 4 x 16位數據移出。在所有 64 位數據流式傳輸到輸出后,數據遵循全零模式。DATA_SYNC信號用于表示每個有效 16 位數據片的開頭。此外,ADC時鐘每128至16,384個周期輸出一個TIME_SYNC信號。

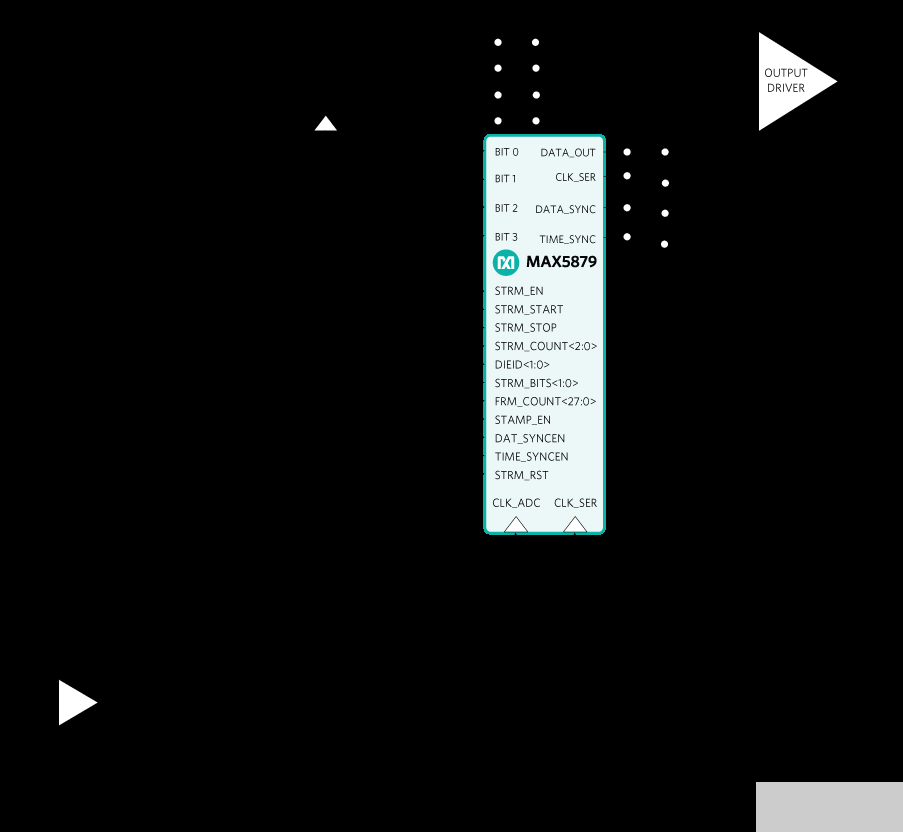

圖1.頂級連接和控制信號。

3線SPI接口控制信號

STRM_EN:此命令配置IC,使DSP接口插入信號路徑。同時,所有內部寄存器均被復位。

STRM_START:此命令的正邊緣允許將數據流式傳輸到輸出。它還支持時鐘和幀同步輸出。

STRM_STOP:此命令的正邊緣禁用數據流到輸出。它還禁用時鐘和幀同步輸出。

STRM_COUNT<2:0>:該控制信號選擇數據(時間)計數器的長度;最小值為 128 位 (000),最大值為 16,394 位 (111)。

DIEID<1:0>:這個詞標識IC的硬件版本。MAX2769C的默認版本對應于00。

STRM_BITS<1:0>:這個詞定義了要流式傳輸到輸出的位數。

00 = 位 0

01 = 位 0,位 1 10 = 位 0,位 2

11 = 位 0,位 1,位 2,位 3

FRM_COUNT<27:0>.這個詞定義了開始流式傳輸的幀號。當命令STRM_EN啟用流模式,但未收到命令STRM_START時,此模式處于活動狀態。在這種情況下,幀計數器在斷言STRM_EN時重置,并開始計數。當幀數達到FRM_COUNT定義的值時,流式傳輸開始。

STAMP_EN:此信號允許在每幀的開頭插入幀號。如果禁用,則僅將ADC數據流式傳輸到輸出。

DAT_SYNCEN:該控制信號使DATA_SYNC輸出端的同步脈沖成為可能。每個脈沖的上升沿與有效數據流的開頭重合,有效數據流始終從位 0<0> 數據開始,并在 16、32 或 64 個周期后停止,具體取決于流的位數。

TIME_SYNCEN:當通過 STRM_EN 命令啟用流時,此信號始終啟用時間同步脈沖的輸出。否則,時間同步脈沖僅在數據流在輸出端處于活動狀態時可用,即在STRM_START和STRM_STOP命令限制的時間間隔內。

STRM_RST:此命令重置所有計數器,而不考慮流周期內的時間。

圖2.方框圖。

時序圖

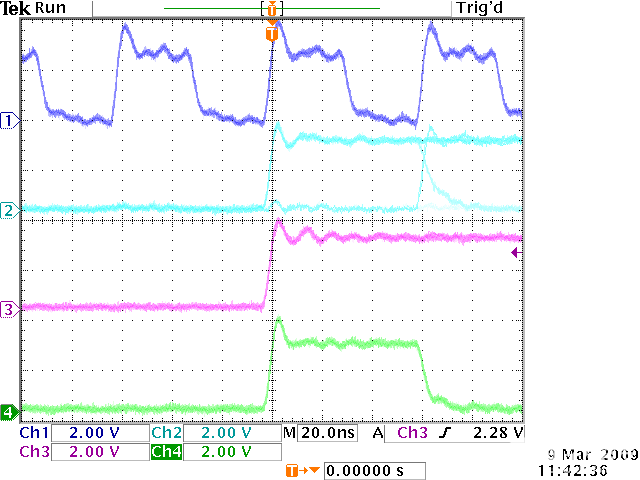

在DSP接口模式下,基帶是MAX2769C DATA_SYNC、TIME_SYNC和DATA_OUT輸出的接收器。DATA_SYNC、TIME_SYNC和DATA_OUT信號置位在CLK_SER的上升沿,需要鎖存到時鐘下降沿的基帶中。圖3和圖4顯示了DSP接口信號的功能時序。

圖3.時序圖。

圖4.具有時間戳輸出的時序圖。

| 計時值 | ||||

| 時間 | SYw | 偏差 | ||

| t延遲 | 0ns | ±2納秒 | ||

|

0.5 | ±0.03 | ||

表1中的數字表示通常預期的時序值和與標準值的預期最大偏差。圖5進一步顯示了實際應用中三種信號之間的關系。

CLK_SER信號的占空比主要由施加在MAX2769C引腳15 (XTAL)上的基準信號的占空比決定。所提供的數字適用于使用Rakon IT3205CE系列16.368MHz TCXO作為參考的情況。

本數據代表Maxim迄今為止為提供具體應用指導所做的最大努力,但不作任何保證。

圖5.CLK_SER、DATA_OUT和TIME_SYNC之間的關系。深藍色 (1) = CLK_SER,淺藍色 (2) = DATA_OUT,粉紅色 (3) = TIME_SYNC,綠色 (4) = DATA_SYNC。

寄存器配置

| 位名 |

位置 (0 = LSB) |

違約 | 功能 |

| STRM_EN | 11 | 0 | 用于串行數據流的DSP接口使能。該位配置IC,使DSP接口插入信號路徑。設置 1 啟用接口,或設置 0 禁用接口。 |

| STRM_START | 10 | 0 | 此命令的正邊緣允許將數據流式傳輸到輸出。它還支持時鐘、數據同步和幀同步輸出。 |

| STRM_STOP | 9 | 0 | 此命令的正邊緣禁用數據流到輸出。它還禁用時鐘、數據同步和幀同步輸出。 |

| STRM_COUNT | 8:6 | 111 |

將時間計數器的長度設置為 128 (000) 到 16384 (111)。 注意:IC數據手冊將這些位顯示為保留位,但這些位仍然可以控制。 |

| STRM_BITS | 5:4 | 01 | 流式傳輸的位數。D[5:4] = 00: I MSB;01: 我 MSB, I LSB;10: I MSB, Q MSB;11: I MSB, I LSB, Q MSB, Q LSB. |

| STAMP_EN | 3 | 1 | 該信號允許在每幀的開頭插入幀號。如果禁用,則僅將ADC數據流式傳輸到輸出。 |

| TIME_SYNCEN | 2 | 1 | 當通過 STRM_EN 命令啟用流時,此信號始終啟用時間同步脈沖的輸出。否則,時間同步脈沖僅在數據流在輸出端處于活動狀態時可用,例如,在STRM_START和STRM_STOP命令限制的時間間隔內。 |

| DAT_SYNCEN | 1 | 0 | 該控制信號使能DATA_SYNC輸出端的同步脈沖。每個脈沖與對應于給定輸出位的16位數據字的開頭重合。 |

| STRM_RST | 0 | 0 | 此命令重置所有計數器,而不考慮流周期內的時間。 |

| 位名 |

位置 (0 = LSB) |

違約 | 功能 |

| L_CNT | 27:16 | 256天 | 設置 L 計數器的值。000100000000 = 256 小數時鐘分頻器,10000000000 = 2048 小數時鐘分頻器 |

| M_CNT | 15:4 | 1563年 | 設置 M 計數器的值。011000011011 = 1563 小數時鐘分頻器,100000000 = 2048 小數時鐘分頻器 |

| FCLKIN是 | 3 | 0 | 小數時鐘分頻器。設置1以選擇來自小數時鐘分頻器的ADC時鐘,或設置0以繞過來自小數時鐘分頻器的ADC時鐘。 |

| ADCCLK | 2 | 0 | ADC 時鐘選擇。設置0以選擇來自基準分頻器/乘法器的ADC和小數分頻器時鐘。 |

| 瑟克 | 1 | 1 | 0 選擇來自基準分頻器的串行器時鐘。 |

| 模式 | 0 | 0 | DSP接口模式選擇,設置為1表示標準模式操作。 |

審核編輯:郭婷

-

dsp

+關注

關注

553文章

7987瀏覽量

348745 -

CMOS

+關注

關注

58文章

5710瀏覽量

235411 -

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

adc

+關注

關注

98文章

6495瀏覽量

544466

發布評論請先 登錄

相關推薦

用DSP的I2C接口配置TVL320AIC12K的寄存器,為什么讀出寄存器的數據顯示為默認值?

MAX2112寄存器配置問題

如何在stm32上通過SPI將32位字傳輸到GPS接收器芯片(MAX2769C)?

MPC860寄存器配置

MAX11120-MAX11128低功耗,逐次逼近寄存器串行ADC

max2769cfcen配置使用指南

MAX2769 GPS接收機用戶指南

如何編程MAX32620FTHR平臺及配置寄存器

IO口配置常用的8個寄存器 1.6

GPIO寄存器

STM32F103寄存器配置相關學習 —— GPIO

如何為DSP接口模式配置MAX2769C ADC寄存器

如何為DSP接口模式配置MAX2769C ADC寄存器

評論