保持多個電信設(shè)備之間的時鐘同步是任何大型安裝的基本功能。一種常見的時鐘分配方法由ITU-T G.703 2048kHz同步接口(T12)指定。雖然DS26303 E1/T1/J1八通道線路接口單元(LIU)完全支持該規(guī)范,但需要一些額外的配置設(shè)置才能正常工作。本應(yīng)用筆記介紹如何使能2048kHz同步接口模式,并配置DS26303以用于時鐘分配應(yīng)用。

介紹

DS26303 E1/T1/J1八通道接口單元(LIU)鮮為人知的特性之一是它能夠發(fā)送和接收符合國際電信聯(lián)盟ITU-T建議書G.703(2001年11月)第13節(jié)2048kHz同步接口(T12)的信號。本應(yīng)用筆記介紹如何正確編程DS26303,使能2048kHz同步接口模式,使器件可用于時鐘分配應(yīng)用,如建筑集成定時電源(BITS)或同步電源單元(SSU)。需要注意的是,DS26303有兩種型號可供選擇:DS26303-120和DS26303-75。兩者之間的唯一區(qū)別是默認(rèn)的E1線路阻抗設(shè)置。人們需要意識到這一事實(shí),并確保在設(shè)計階段使用的特定設(shè)備與用于制造的設(shè)備相同。

DS26303編程用于2048kHz同步接口模式

對DS26303進(jìn)行編程以支持2048kHz同步接口是一個多步驟的過程,需要使用DS26303數(shù)據(jù)資料中未記錄的一些寄存器。所有未記錄登記冊的完整說明可在下面的附錄中找到。

在使能2048kHz同步接口模式之前,需要執(zhí)行幾個配置步驟來確保DS26303按預(yù)期工作。

第 1 步。更改內(nèi)部時鐘圖以使用與LIU通道關(guān)聯(lián)的發(fā)送時鐘(通常是TCLK輸入)而不是主時鐘(MCLK輸入)。默認(rèn)情況下,當(dāng)使能2048kHz同步接口模式時,DS26303使用公共MCLK輸入作為時鐘源。這將導(dǎo)致TTIP/TRING引腳上的輸出信號頻率鎖定到MCLK輸入,而不是TCLK輸入。要對DS26303進(jìn)行編程,以TCLK輸入作為時鐘源,使用以下軟件配置。

將地址 0x1F 處的 ADDP 寄存器設(shè)置為值 0x03,這將選擇全局測試寄存器庫。

將地址 0x07 處的 TXDIG 寄存器設(shè)置為 0x10 值。通過將TXDIG寄存器的位4設(shè)置為1,2048kHz同步接口模式將使用TCLK輸入而不是MCLK輸入。需要注意的是,改變TXDIG寄存器的位4也會影響通常使用MCLK輸入作為時鐘的另外兩個功能,特別是傳輸所有1(TAOE)和自動發(fā)送所有1(ATAOS)功能。因此,當(dāng)禁用2048kHz同步接口模式時,需要將該位設(shè)置回0。但是,如果工程師希望在啟用TAOE或ATAOS時使用TCLK輸入作為時鐘源,則TXDIG寄存器的第4位可以設(shè)置為1。

第 2 步。

更改短路檢測電路 (SCDC) 的限流值,以防止禁用 TTIP/TRING 發(fā)送器輸出。默認(rèn)情況下,當(dāng)使能2048kHz同步接口模式時,DS26303的限流值不正確。要用適當(dāng)?shù)亩搪?a href="http://www.1cnz.cn/tags/電流/" target="_blank">電流值對DS26303進(jìn)行編程,請使用以下軟件配置。

將地址0x1F處的 ADDP 寄存器設(shè)置為 0x04 到 0x0B 之間的值,該值分別通過 LIU8 測試寄存器組選擇 LIU1 測試。

將地址0x05處的TXCMDA寄存器設(shè)置為下面列出的值之一(表1)。這些值應(yīng)與模板選擇 (TS) 寄存器中選擇的值同步。例如,當(dāng)TS寄存器配置為E1 75Ω模式時,將TXCMDA寄存器設(shè)置為0x33值。此外,當(dāng)啟用 G.703 2048kHz 同步接口模式時,TS 寄存器中的發(fā)射阻抗終止設(shè)置不應(yīng)關(guān)閉。請注意,TXCMDA 寄存器位 7:6 應(yīng)始終保持在 0;位 5 控制 SCDC 覆蓋啟用;位 4:0 包含新的短路電流限制值。雖然可以對極限值進(jìn)行調(diào)整,但不建議這樣做,因?yàn)檫x擇這些值是為了防止損壞設(shè)備。

表 1.TXCMDA 寄存器設(shè)置

| TS 模式設(shè)置 | TXCMDA 價值 |

| E1 75Ω | 0x33 |

| E1 120Ω | 0x2F |

完成這兩個配置步驟后,DS26303被正確配置為支持2048kHz同步接口模式。

要為DS26303的一個或多個通道編程,以實(shí)現(xiàn)2048kHz同步接口模式,請使用以下軟件配置。

將地址 0x1F 處的 ADDP 寄存器設(shè)置為 0x01 值,這將選擇單個 LIU 寄存器庫。

將地址0x08處的G703EN寄存器設(shè)置為為相應(yīng)LIU通道啟用2048kHz同步接口模式所需的值。

假設(shè)現(xiàn)在按照前面的建議禁用了 TTIP/TRING 發(fā)射器輸出,請使用以下軟件配置啟用發(fā)射器輸出。

將地址 0x1F 處的 ADDP 寄存器設(shè)置為 0x00 值,這將選擇主寄存器庫。

將地址0x12處的OEB寄存器設(shè)置為為G703EN寄存器中啟用的相同LIU通道啟用TTIP/TRING發(fā)射器輸出所需的值。

結(jié)論

只需對DS26303的默認(rèn)行為稍作改動,器件即可完全支持ITU-T G.703 2048kHz同步接口(T12)規(guī)范。本應(yīng)用筆記描述了需要進(jìn)行哪些更改,提供了有關(guān)這些更改的背景信息,并提供了詳細(xì)的配置過程。這些信息和DS26303數(shù)據(jù)資料允許任何設(shè)計人員將2048kHz同步接口特性集成到BITS或SSU設(shè)計中。

附錄:DS26303 所需寄存器信息

DS26303的寄存器空間跨越地址0x00到0x1F。它使用內(nèi)存庫模型,并包含所有 LIU 通道的配置和狀態(tài)信息。地址0x1F處的ADDP寄存器是一個特殊的寄存器,用作訪問不同寄存器庫的指針。對于每個寄存器庫,此寄存器的功能和值保持不變。但是,對 ADDP 寄存器的更改將更改當(dāng)前寄存器組,從而更改跨越地址0x00到0x1E的寄存器的功能和值。

以下是有關(guān)寄存器的詳細(xì)信息以及啟用ITU-T G.703 2048kHz同步接口(T12)模式所需的每個位的說明。

寄存器名稱:ADDP

寄存器銀行:存在于所有寄存器庫中

寄存器說明:地址指針

寄存器地址:1Fh

| 位# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名字 | ADDP7 | ADDP6 | ADDP5 | ADDP4 | ADDP3 | ADDP2 | ADDP1 | ADDP0 |

| 違約 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 0:地址指針 (ADDP)。

此值用作在主注冊庫、輔助注冊庫、個人 LIU 注冊庫、BERT 注冊庫和任何測試注冊庫之間進(jìn)行選擇和切換的指針。例如,軟件必須將 ADDP 寄存器設(shè)置為 0x00 才能訪問寄存器的主庫;0xAA以訪問二級登記冊庫;0x01訪問個人劉氏登記冊庫;或0x02訪問BERT注冊庫。有關(guān)正確的寄存器庫選擇,請參見

表 2

。

表 2.地址指針寄存器組選擇

| ADDP Register Value | Register Bank Name |

| 0x00 | Primary |

| 0xAA | Secondary |

| 0x01 | Individual LIU |

| 0x02 | BERT |

| 0x03 | Global Test |

| 0x04 | LIU1 Test |

| 0x05 | LIU2 Test |

| 0x06 | LIU3 Test |

| 0x07 | LIU4 Test |

| 0x08 | LIU5 Test |

| 0x09 | LIU6 Test |

| 0x0A | LIU7 Test |

| 0x0B | LIU8 Test |

注冊名稱:

G703EN

注冊銀行:

個人 LIU 注冊銀行 注冊說明

:

ITU-T G.703 2048kHz 同步接口啟用

寄存器地址:

08h

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | G703EN7 | G703EN6 | G703EN5 | G703EN4 | G703EN3 | G703EN2 | G703EN1 | G703EN0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 0:G703 使能 (G703EN)。

當(dāng)清除為 0 時,關(guān)聯(lián) LIU 通道的發(fā)射器和接收器處于正常 T1/E1/J1 模式。設(shè)置為 1 時,相關(guān) LIU 通道的發(fā)射器和接收器將進(jìn)入 ITU-T G.703 2048kHz 同步接口 (T12) 模式。

注意:此功能僅在設(shè)備修訂版 A2 及更高版本中可用。

寄存器名稱: TXCMDA

寄存器名稱: LIU 測試 寄存器組 1 至 8 寄存器說明: 傳輸線驅(qū)動器自定義模式 A

寄存器地址: 05h

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | Reserved | Reserved | SCDCOR | SCC4 | SCC3 | SCC2 | SCC1 | SCC0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 6:保留。

此位應(yīng)保持清除為 0。

位 5:短路檢測電路覆蓋 (SCDCOR)。當(dāng)清除為 0 時,將啟用默認(rèn)線路驅(qū)動器電流限制。設(shè)置為 1 時,默認(rèn)線路驅(qū)動器電流限制將被 SCC[4:0] 設(shè)置的值覆蓋。

位 4 到 0:短路電流 (SCC[4:0])。當(dāng)短路檢測電路覆蓋(SCDCOR)位設(shè)置為1時,這4位的二進(jìn)制加權(quán)值設(shè)置短路檢測電路電流限制。當(dāng)線路驅(qū)動器電流超過此值時,發(fā)射器被禁用,驅(qū)動器故障監(jiān)視器狀態(tài)設(shè)置為1。

注意:此功能僅在設(shè)備修訂版 A2 及更高版本中可用。

寄存器名稱: TXDIG 寄存器名稱: 全局測試 寄存器銀行

寄存器說明: 傳輸數(shù)字測試模式

寄存器地址: 07h

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | Reserved | Reserved | Reserved | CLKS | Reserved | Reserved | Reserved | Reserved |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 5:保留。

此位應(yīng)保持重置為 0。

位 5:時鐘選擇模式 (CLKS)。當(dāng)清除為 0 時,當(dāng) LIU 通道處于以下模式時,每個 LIU 通道的發(fā)射時鐘源是主時鐘:發(fā)送所有 1、自動發(fā)送所有 1、ITU-T G.703 2048kHz 同步接口 (T12) 和出廠測試。當(dāng)設(shè)置為 1 時,當(dāng) LIU 通道處于上述任何模式時,每個 LIU 通道的發(fā)送時鐘源是關(guān)聯(lián)的 TCLK 引腳(如果啟用了遠(yuǎn)程環(huán)回,則恢復(fù)時鐘)。

位 3 到 0:保留。這些位應(yīng)保持清除為 0。

審核編輯:郭婷

-

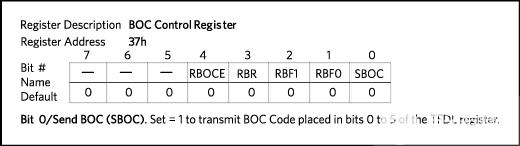

寄存器

+關(guān)注

關(guān)注

31文章

5336瀏覽量

120230 -

接口

+關(guān)注

關(guān)注

33文章

8575瀏覽量

151015

發(fā)布評論請先 登錄

相關(guān)推薦

itu-t g.711標(biāo)準(zhǔn)介紹

ITU-T G.709概述

DS26303中文資料

DS26303.pdf

MSM7581 pdf datasheet (ITU-T G

MSM7580 pdf datasheet (ITU-T G

DS26303 LIU的初始化和配置

DS26303短程線路接口單元與IDT82V2048的比較

DS26303短程線路接口單元與LXT384的比較

G.703通信接口轉(zhuǎn)換器

如何在DS26303 LIU啟用ITU-T G.703 2048kHz同步接口

如何在DS26521和DS2155中發(fā)送/接收SSM

典型的E1接口連接器和實(shí)現(xiàn)

如何在DS26303 LIU上啟用ITU-T G.703 2048kHz同步接口

如何在DS26303 LIU上啟用ITU-T G.703 2048kHz同步接口

評論