MAX9979是完全集成的引腳電子IC,由DCL、PMU和電平設(shè)置器組成。MAX9979的所有模塊均具有箝位、有源負(fù)載、高范圍拉電流和灌電流能力、數(shù)據(jù)反轉(zhuǎn)和差分模式等特性。MAX9979參數(shù)測量單元(PMU)既能施加力,又能測量電流和電壓。設(shè)置電壓和電流鉗位可確保PMU在線性區(qū)域工作。本應(yīng)用筆記簡化了對PMU功能的理解并根據(jù)應(yīng)用調(diào)整鉗位的過程。

介紹

MAX9979中的參數(shù)測量單元(PMU)模塊負(fù)責(zé)強制和測量電流和電壓。可支持 -1.5V 至 6.5V 的電壓范圍和 ±2μA 至 ±50mA 的滿量程電流范圍。MAX9979的電壓和電流箝位特性使PMU在性能方面更加通用,但需要仔細(xì)考慮。

了解 PMU 功能至關(guān)重要,因此此應(yīng)用程序?qū)⑹紫冉榻B PMU 模式和操作范圍。然后,將詳細(xì)介紹PMU鉗具的使用。

PMU 模式和操作范圍

MAX9979 PMU可配置為六種工作模式,如表1所示。

力-電壓/測量-電壓 (FVMV)

力-電壓/測量-電流 (FVMI)

力-電流/測量-電流 (FIMI)

力-電流/測量-電壓 (FIMV)

無強制/測量電壓 (FNMV)

無強制/無測量 (FNMN)

| Digital Input | Serial Interface Bits | PMU Mode | ||

| LLEAKP | HIZFORCE | FMODE | MMODE | |

| 1 | 1 | X | X | FyMy* |

| 1 | 1 | X | X | FyMy* |

| 1 | 0 | 0 | X | FVMy* (calibration) |

| 1 | 0 | 0 | X | FVMy* (calibration) |

| 1 | 0 | 1 | 0 | FNMN |

| 1 | 0 | 1 | 1 | FNMV (calibration) |

| 1 | 0 | 1 | 1 | FNMV (calibration) |

| 0 | X | X | 0 | FNMN |

| 0 | X | X | 1 | FNMV (calibration) |

| 0 | X | X | 1 | FNMV (calibration) |

| *y = V 或 I | ||||

基于滿量程電流范圍選擇,PMU力-電流和測量-電流可以通過三位控制字(RS2、RS1和RS0)在不同的電流范圍內(nèi)工作或控制,如表2所示。

| Digital Input | Serial Interface Bits |

PMU Range (IRANGE, RRANGE) |

|||

| LLEAKP | HIZFORCE | RS2 | RS1 | RS0 | |

| X | X | 0 | 0 | 0 | E(±2μA, 500kO) |

| X | X | 0 | 0 | 1 | D(±20μA, 50kO) |

| X | X | 0 | 1 | 0 | C(±200μA, 5kO) |

| X | X | 0 | 1 | 1 | B(±2mA, 500O) |

| X | 0 | 1 | X | X | B* |

| 0 | 1 | 1 | X | X | B* |

| 1 | 1 | 1 | X | X | A(±50mA, 20O) |

| * PMU 高阻抗模式不允許范圍 A 操作 — PMU 默認(rèn)為范圍 B。 | |||||

PMU 電壓/電流鉗

PMU電壓或電流鉗確保DUT_電壓或電流分別不能超過鉗位電壓或電流。PMU 電壓箝位在 FI 工作模式下可用,而電流箝位在 FV 模式下可用。當(dāng)PMU電壓/電流箝位處于活動狀態(tài)時,在其限值內(nèi),MV和MI功能仍然有效。

設(shè)置CLAMPHI_和CLAMPLO_數(shù)模轉(zhuǎn)換器(DAC)設(shè)置高鉗位電壓(VCLAMPHI) 和低鉗位電壓 (VCLAMPLO)分別。在FI模式下,用戶可以使用CLAMPHI_和CLAMPLO_DAC直接設(shè)置電壓箝位。對于電流鉗 IIOSDAC (VIIOS) 需要與 CLAMPHI_ 和CLAMPLO_ DAC 一起設(shè)置。鉗位大電流(ICLAMPHI)和鉗位低電流(ICLAMPLO) 方程給出如下。

ICLAMPHI = (VCLAMPHI - VIIOS)/RRANGE

VCLAMPHI = (ICLAMPHI × RRANGE) + VIIOS

示例 1:

考慮 FVMI 模式下的 PMU 和范圍 B 操作。

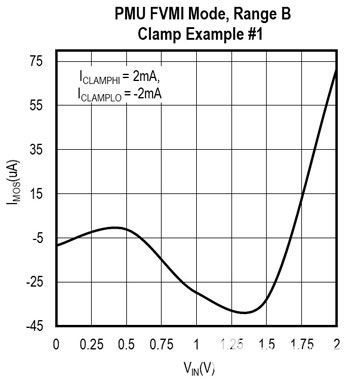

考慮 VIIOS DAC電壓是2.5V,1K?是 DUT 負(fù)載。ICLAMPHI為 2mA 和 ICLAMPLO為-2mA。開始 VIN_從 2V 逐漸降低。公式1和2用于下表3中的計算。

| VIN (V) | VIIOS (V) | ICLAMPHI (mA) | ICLAMPLO (mA) | CLAMPHI DAC Voltage (V) | CLAMPLO DAC Voltage(V) | VDUT (V) | IDUT (mA) | IMOS (uA) |

| 2 | 2.5 | +2 | -2 | 3.5 | 1.5 | 1.86598 | 1.92857 | 71.43 |

| 1.5 | 2.5 | +2 | -2 | 3.5 | 1.5 | 1.4969 | 1.5329 | -32.9 |

| 1 | 2.5 | +2 | -2 | 3.5 | 1.5 | 0.9996 | 1.0299 | -29.9 |

| 0.5 | 2.5 | +2 | -2 | 3.5 | 1.5 | 0.4992 | 0.5012 | -1.2 |

| 0 | 2.5 | +2 | -2 | 3.5 | 1.5 | 0.0082 | 0.0085 | -8.5 |

作為 VIN_ 逐漸減少,VDUT_ 和IDUT也減少。MAX9979 PMU具有測量電流失調(diào)(IMOS) 的 ±1 % FSR(如數(shù)據(jù)手冊的 EC 表所述)。由于PMU處于B工作范圍(FSR = 4mA),因此預(yù)期的最大電流失調(diào)為±40μA。如果 IDU失調(diào)超過 ±40μA,則不需要輸出。在表 3 中,藍(lán)綠色讀數(shù)是理想的,橙色讀數(shù)是不可取的。對于PMU,需要滿足兩個條件。

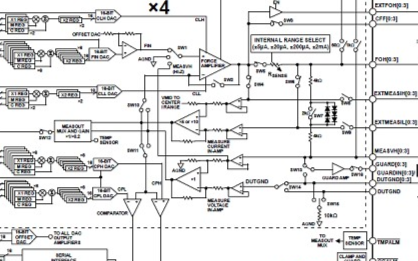

圖1.PMU FVMI 模式,范圍 B 箝位,示例 1。

為了在FI模式下保持線性度:

(VCLAMPLO + 0.5V) = VDUT = (VCLAMPHI – 0.5V)

為了在FV模式下保持線性度:

(ICLAMPLO + 10% FSR) = IDUT = (ICLAMPHI – 10%FSR)

示例 2:

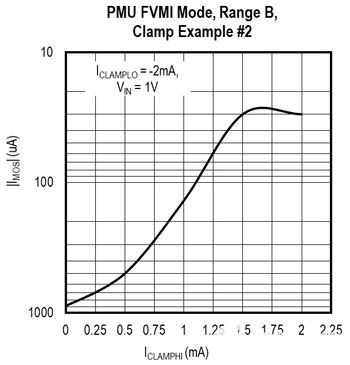

考慮 FVMI 模式下的 PMU 和范圍 B 操作。

FMODE = 0, MMODE = 0, RRANGE = 500?, FSR = 4mA

考慮 VIIOS DAC電壓是2.5V,1K?是DUT_負(fù)載。修復(fù) V在_ DAC電壓為1V。將箝位電流從2mA更改為0mA。公式1和2用于下面表4中的計算。

Expected IDUT = VDUT/RLOAD = 1V/1K? = ±1mA

注意:±符號表示MAX9979器件可以供應(yīng)或吸收電流。

在范圍 B 工作時:10% FSR = 10% 的 4mA = 0.4mA

根據(jù)公式 4,假設(shè)設(shè)備如下:

IDUT = (ICLAMPHI – 10% FSR)

IDUT + 10% FSR = ICLAMPHI

ICLAMPHI = 1mA + 0.4mA = 1.4mA

Similarly, ICLAMPLO = -1.4mA

| VIN (V) | VIIOS (V) | ICLAMPHI (mA) | ICLAMPLO (mA) | CLAMPHI DAC Voltage (V) | CLAMPLO DAC Voltage(V) | VDUT (V) | IDUT (mA) | IMOS (uA) |

| 1 | 2.5 | 2 | -2 | 3.5 | 1.5 | 0.9996 | 1.0299 | 29.9 |

| 1 | 2.5 | 1.5 | -2 | 3.25 | 1.5 | 0.9996 | 1.0299 | 29.9 |

| 1 | 2.5 | 1 | -2 | 3 | 1.5 | 0.8642 | 0.8623 | -137.7 |

| 1 | 2.5 | 0.5 | -2 | 2.75 | 1.5 | 0.4911 | 0.5018 | -498.2 |

| 1 | 2.5 | 0 | -2 | 2.5 | 1.5 | 0.1117 | 0.1155 | -884.5 |

VIN在 1V。在 FVMI 模式下,我們期望 VDUT= 1V。因此IDUT= DUT/RDUT = 1V/1K? = +1mA。在橙色行中觀察,當(dāng)ICLAMPH小于1.4mA,VDUT和IDUT讀數(shù)不是預(yù)期值。在這種情況下,IDUT失調(diào)誤差大于±40uA。

圖2.PMU FVMI 模式,范圍 B 箝位示例 2。

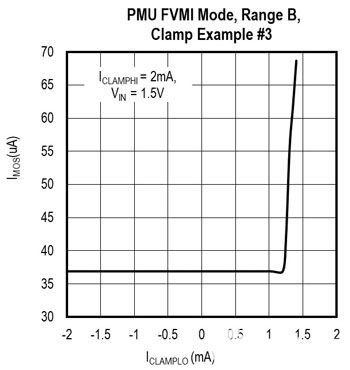

示例 3:

考慮 FVMI 模式下的 PMU 和范圍 B 操作。

FMODE = 0, MMODE = 0, RRANGE = 500?, FSR = 4mA

考慮 VIIOS DAC電壓是2.5V,1K?是DUT_負(fù)載。將VIN_DAC電壓固定為1.5V,I夾子作為2mA。更改 ICLAMPLO從-2mA到1.4mA。公式1和2用于下面表5中的計算。

| VIN (V) | VIIOS (V) | ICLAMPHI (mA) | ICLAMPLO (mA) | CLAMPHI DAC Voltage (V) | CLAMPLO DAC Voltage(V) | VDUT (V) | IDUT (mA) | IMOS (uA) |

| 1.5 | 2.5 | 2 | -2 | 3.5 | 1.5 | 1.4912 | 1.5369 | 36.9 |

| 1.5 | 2.5 | 2 | -1 | 3.5 | 2 | 1.4912 | 1.5369 | 36.9 |

| 1.5 | 2.5 | 2 | 0 | 3.5 | 2.5 | 1.4912 | 1.5369 | 36.9 |

| 1.5 | 2.5 | 2 | 1 | 3.5 | 3 | 1.4912 | 1.5369 | 36.9 |

| 1.5 | 2.5 | 2 | 1.2 | 3.5 | 3.1 | 1.4912 | 1.5369 | 36.9 |

| 1.5 | 2.5 | 2 | 1.4 | 3.5 | 3.2 | 1.5174 | 1.5687 | 68.7 |

從等式4,

(ICLAMPLO + 10% FSR) = IDUT = (ICLAMPHI – 10% FSR)

(ICLAMPLO + 10% FSR) = (ICLAMPHI – 10% FSR)

ICLAMPHI – ICLAMPLO = 20% FSR

VCLAMPHI – VCLAMPLO = (20% FSR) × RRANGE;從等式 1 和 2 開始。

圖3.PMU FVMI 模式,范圍 B 箝位示例 3。

示例 4:

考慮 FIMV 模式下的 PMU 和范圍 B 操作。

FMODE = 1, MMODE = 1, R范圍= 500?, FSR = 4mA

考慮 VIIOS DAC電壓是2.5V,1K?是DUT_負(fù)載。修復(fù)VIN DAC電壓為5.5V。將箝位電壓從 ±2.5V 更改為 ±1.5V。

當(dāng)PMU處于FI模式時,電壓箝位就會出現(xiàn)。從等式3,

(VCLAMPLO + 0.5V) = VDUT = (VCLAMPHI – 0.5V).

在FI模式出DUT的電流按照下面的公式5計算。

DUT = (VIN – VIIOS)/(4 × RRANGE)

其中;

IDUT = (5.5 – 2.5)/(4 × 500)

IDUT = 1.5mA

VDUT = IDUT × RLOAD = 1.5mA × 1K? = 1.5V

| VIN (V) | VIIOS (V) | VCLAMPHI (V) | VCLAMPLO (V) | VDUT (V) | IDUT (mA) | VMOS (uA) |

| 5.5 | 2.5 | 2.5 | -2.5 | 1.487 | 1.498 | -13 |

| 5.5 | 2.5 | 2 | -2 | 1.487 | 1.498 | -13 |

| 5.5 | 2.5 | 1.5 | -1.5 | 1.393 | 1.441 | -107 |

預(yù)期的DUT電壓為1.5V,箝位電壓應(yīng)比預(yù)期的DUT電壓高0.5V。當(dāng)箝位電壓與DUT電壓相同時,DUT電壓開始降低(參見圖表中的橙色行)。電壓偏移的測量(VMOS) 增加超過 25mV。

總結(jié)

本應(yīng)用筆記為用戶提供了在線性區(qū)域操作PMU的指南。這很簡單,有兩個等式:

(VCLAMPLO + 0.5V) = VDUT = (VCLAMPHI – 0.5V)

To maintain linearity in FV mode:

(ICLAMPLO + 10% FSR) = IDUT = (ICLAMPHI – 10% FSR)

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8694瀏覽量

147085 -

dac

+關(guān)注

關(guān)注

43文章

2291瀏覽量

190976 -

PMU

+關(guān)注

關(guān)注

1文章

108瀏覽量

21592

發(fā)布評論請先 登錄

相關(guān)推薦

MAX5974寬輸入電壓范圍、有源鉗位、電流模式PWM控制器

基于ADI AD522集成16位單元方案設(shè)置DAC四參數(shù)測量

如何設(shè)置PMU電壓和電流鉗位

如何設(shè)置PMU電壓和電流鉗位

評論