從微控制器單元 (MCU) 到現(xiàn)場(chǎng)可編程門陣列 (FPGA) 的各種設(shè)備滲透到我們互聯(lián)的世界中。為了正常運(yùn)行,此類設(shè)備需要時(shí)鐘來(lái)同步它們處理、傳輸和接收的數(shù)據(jù)。

體聲波 (BAW) 技術(shù)能夠制造出具有可編程頻率的緊湊、精確、可靠的時(shí)鐘,無(wú)需儲(chǔ)備多個(gè)以不同固定頻率運(yùn)行的晶體。BAW 諧振器在確保移動(dòng)和物聯(lián)網(wǎng) (IoT) 設(shè)備與云計(jì)算資源之間的無(wú)縫通信方面發(fā)揮著關(guān)鍵且日益重要的作用。

基于 MEMS 的諧振器

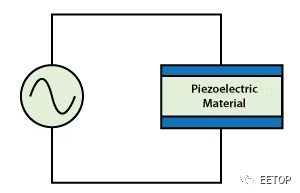

1. 體聲波諧振器包括夾在兩個(gè)電極之間的壓電材料。

體聲波諧振器是一種微機(jī)電系統(tǒng)(MEMS),由夾在兩個(gè)電極之間的壓電材料組成(圖 1)。這種材料可以將電能轉(zhuǎn)化為機(jī)械聲能,產(chǎn)生可靠的振蕩,從而實(shí)現(xiàn)高頻時(shí)鐘輸出。

比如BAW 諧振器使德州儀器的CC2652RBSimpleLink MCU 能夠在沒(méi)有外部晶體振蕩器的情況下運(yùn)行。

MCU 的集成諧振器在不影響延遲的情況下減少了占據(jù)PCB的面積并最大限度地降低了物料清單 (BOM) 成本,并且它在整個(gè)工作溫度和工作電壓范圍內(nèi)提供 ±40 ppm 的頻率穩(wěn)定性。此外,2.4-GHz 多協(xié)議 MCU 提供超低抖動(dòng)和相位噪聲以滿足各種無(wú)線通信標(biāo)準(zhǔn)的時(shí)鐘要求。

TI 還將 BAW 技術(shù)集成到其 LMK6C 低抖動(dòng)、高性能、固定頻率振蕩器中。它在振動(dòng)、沖擊、溫度穩(wěn)定性和可靠性方面提供增強(qiáng)的抖動(dòng)性能和改進(jìn)的可靠性。

最重要的是,該技術(shù)還用于 TI 的 LMK05318 高性能網(wǎng)絡(luò)同步器時(shí)鐘設(shè)備,該設(shè)備提供抖動(dòng)清除、時(shí)鐘生成和高級(jí)時(shí)鐘監(jiān)控,以滿足通信基礎(chǔ)設(shè)施和工業(yè)應(yīng)用的定時(shí)要求。該器件的超低抖動(dòng)和高電源噪聲抑制 (PSNR) 可以降低貫穿互聯(lián)世界的高速串行鏈路中的誤碼率 (BER)。

BAW 與石英

新的 BAW 技術(shù)與古老的石英晶體振蕩器競(jìng)爭(zhēng),石英晶體振蕩器在計(jì)時(shí)參考市場(chǎng)占據(jù)主導(dǎo)地位超過(guò)一個(gè)世紀(jì)。但 BAW 具有顯著優(yōu)勢(shì):它消耗的功率更少,允許更小的系統(tǒng)設(shè)計(jì),并簡(jiǎn)化系統(tǒng)集成,同時(shí)提供與石英類似或更好的性能。

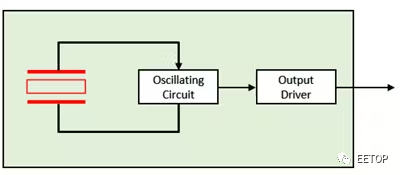

與 BAW 實(shí)施相比,對(duì)石英諧振器的回顧有助于說(shuō)明它們的一些缺點(diǎn)。圖 2說(shuō)明了一種實(shí)現(xiàn)石英振蕩器的方法——結(jié)合石英晶體、振蕩電路和輸出驅(qū)動(dòng)器。

2. 一個(gè)簡(jiǎn)單的石英振蕩器的輸出頻率取決于晶體(紅色)的選擇。

設(shè)置簡(jiǎn)單,啟動(dòng)時(shí)間快,但其頻率完全取決于所選晶體——改變頻率需要更換晶體,因此您需要為每個(gè)感興趣的頻率儲(chǔ)備不同批次的晶體。此外,這種振蕩器很少在超過(guò)大約 50 MHz 的基頻下工作,因?yàn)楦哳l率的晶體難以制造。

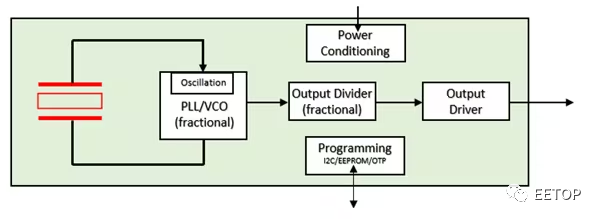

圖 3中所示的方法克服了其中的一些缺點(diǎn)。在這里,晶體用作鎖相環(huán) (PLL) 的參考,它可以產(chǎn)生G赫茲范圍內(nèi)的頻率。小數(shù)輸出分頻器可通過(guò)內(nèi)部集成電路 (I2C)接口進(jìn)行編程,編程信息存儲(chǔ)在電可擦可編程只讀存儲(chǔ)器 (EEPROM) 中,生成所需的頻率。

3. 小數(shù)輸出分頻器可對(duì)輸出頻率進(jìn)行編程。

然而,這種方法比圖 2中的方法需要更多的核心塊,從而導(dǎo)致更大的封裝尺寸和更高的功耗。此外,啟動(dòng)時(shí)間很慢,因?yàn)?PLL 需要 10 ms 或更長(zhǎng)的時(shí)間來(lái)校準(zhǔn)和鎖定。

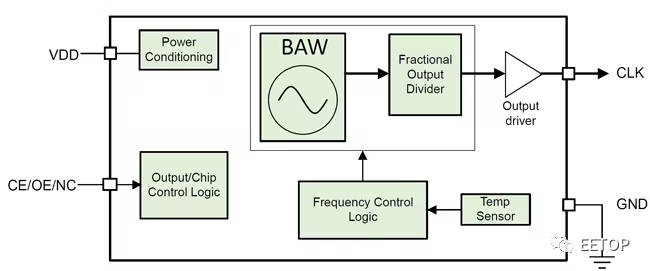

圖 4顯示了一個(gè)帶有集成 BAW 諧振器的振蕩器,該諧振器取代了外部晶體。與圖 3的電路一樣,小數(shù)輸出分頻器根據(jù)存儲(chǔ)在存儲(chǔ)器中的編程值生成所需的頻率。TI可以采用四引腳或六引腳封裝(分別用于單端和差分輸出)制造此類設(shè)備。

4. 具有單端輸出的 BAW 振蕩器適合四引腳工業(yè)標(biāo)準(zhǔn)封裝。

每個(gè)這樣的設(shè)備都將其電路集成在采用深亞微米工藝技術(shù)設(shè)計(jì)的基礎(chǔ)芯片上。位于同一位置的傳感器持續(xù)監(jiān)控溫度變化,信號(hào)處理算法使用存儲(chǔ)在非易失性存儲(chǔ)器中的校準(zhǔn)系數(shù)將頻率保持在 ±10 ppm 預(yù)算范圍內(nèi)。低抖動(dòng)低功耗小數(shù)輸出分頻器可實(shí)現(xiàn)溫度補(bǔ)償,同時(shí)對(duì)相位抖動(dòng)的影響極小。除了溫度穩(wěn)定性外,該器件還提供良好的相位噪聲性能,差分輸出版本將抖動(dòng)限制在 125 fs。

基于 BAW 的設(shè)備包括內(nèi)部低壓差穩(wěn)壓器 (LDO),以提供改進(jìn)的 PSNR。它還符合 MIL-STD-2007 Condition A 和 MIL-STD-2002Condition A 對(duì)沖擊和振動(dòng)的要求,振動(dòng)引起的頻率偏差限制在 1 ppb/g 左右。與石英振蕩器相比,這幾乎是一個(gè)數(shù)量級(jí)的改進(jìn)。

FPGA 的時(shí)鐘生成

FPGA 設(shè)計(jì)通常需要靈活的高性能振蕩器或時(shí)鐘發(fā)生器 IC 來(lái)提供一個(gè)或多個(gè)時(shí)鐘輸入。FPGA 的串行器/解串器 (SERDES) 收發(fā)器通常依賴具有低集成均方根 (RMS) 抖動(dòng)的外部參考時(shí)鐘來(lái)最大限度地減少收發(fā)器位錯(cuò)誤。BAW 諧振器可以輕松生成 FPGA 設(shè)計(jì)所需的頻率。

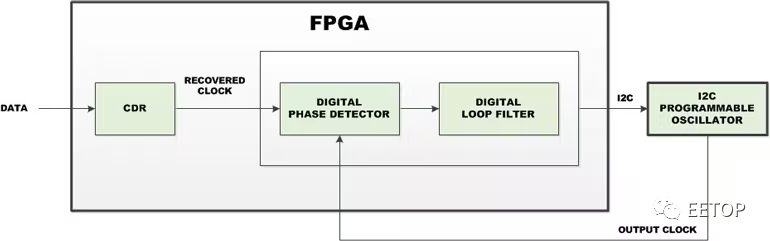

對(duì)于需要從串行數(shù)據(jù)流中恢復(fù)時(shí)鐘信號(hào)的應(yīng)用,串行可編程諧振器可以用作基于 FPGA 的時(shí)鐘數(shù)據(jù)恢復(fù) (CDR) 電路中的數(shù)控振蕩器。

如圖 5所示,F(xiàn)PGA 邏輯實(shí)現(xiàn)了數(shù)字鑒相器和數(shù)字環(huán)路濾波器。后者通過(guò)I2C接口將控制字寫入可編程振蕩器寄存器。然后振蕩器根據(jù)這個(gè)環(huán)路濾波器控制字調(diào)整它的輸出頻率。跟蹤恢復(fù)時(shí)鐘所需的頻率調(diào)整通常以百萬(wàn)分之一來(lái)衡量(例如,小于標(biāo)稱值的 ±50 ppm)。

5.數(shù)控可編程振蕩器服務(wù)于FPGA中實(shí)現(xiàn)的CDR電路。

結(jié)論

BAW 諧振器提供了擴(kuò)展應(yīng)用的靈活性,從包含 MCU 的物聯(lián)網(wǎng)邊緣設(shè)備到采用 FPGA 的高性能系統(tǒng)。帶有串行編程接口和板載 EEPROM 的版本提供了支持多種頻率和簡(jiǎn)化整個(gè)產(chǎn)品生命周期的靈活性。與基于石英晶體的諧振器相比,體聲波諧振器將高性能、可靠性和可用性與較短的交貨時(shí)間和簡(jiǎn)化的供應(yīng)鏈管理相結(jié)合。

審核編輯:劉清

-

微控制器

+關(guān)注

關(guān)注

48文章

7565瀏覽量

151577 -

振蕩器

+關(guān)注

關(guān)注

28文章

3833瀏覽量

139153 -

諧振器

+關(guān)注

關(guān)注

4文章

1132瀏覽量

65946 -

BAW

+關(guān)注

關(guān)注

3文章

121瀏覽量

18707

原文標(biāo)題:BAW(體聲波)技術(shù)及應(yīng)用

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TI基于體身波諧振器技術(shù)的微型計(jì)時(shí)器產(chǎn)品

TI BAW的5項(xiàng)技術(shù)要點(diǎn)

基于TI BAW技術(shù)的產(chǎn)品可為設(shè)計(jì)工程師提供哪些優(yōu)勢(shì)?

使用MEMS振蕩器代替晶體諧振器的 8 大理由(一)

使用MEMS振蕩器代替晶體諧振器的 8 大理由(二)

使用MEMS振蕩器代替晶體諧振器的 8 大理由(三)

BAW諧振器技術(shù)的優(yōu)勢(shì)

PCMR體聲波諧振器多物理場(chǎng)仿真及芯片制作

介紹村田MEMS諧振器的3大特征

剖析Murata MEMS表面貼裝諧振器

SiTime MEMS諧振器制造工藝

基于MEMS的BAW諧振器技術(shù)及應(yīng)用

基于MEMS的BAW諧振器技術(shù)及應(yīng)用

評(píng)論