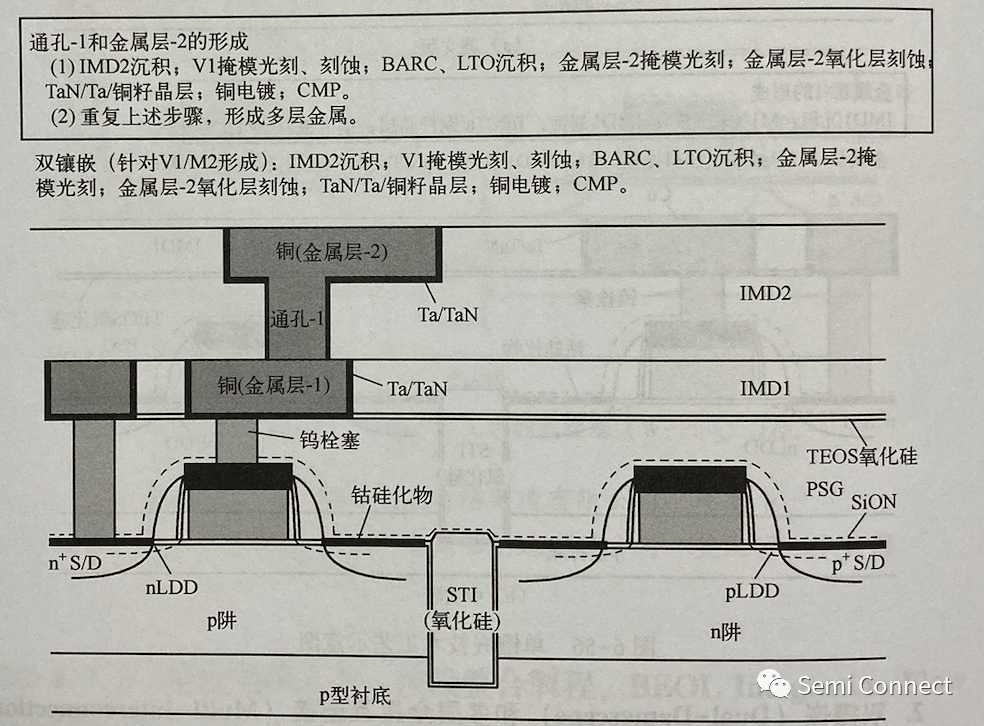

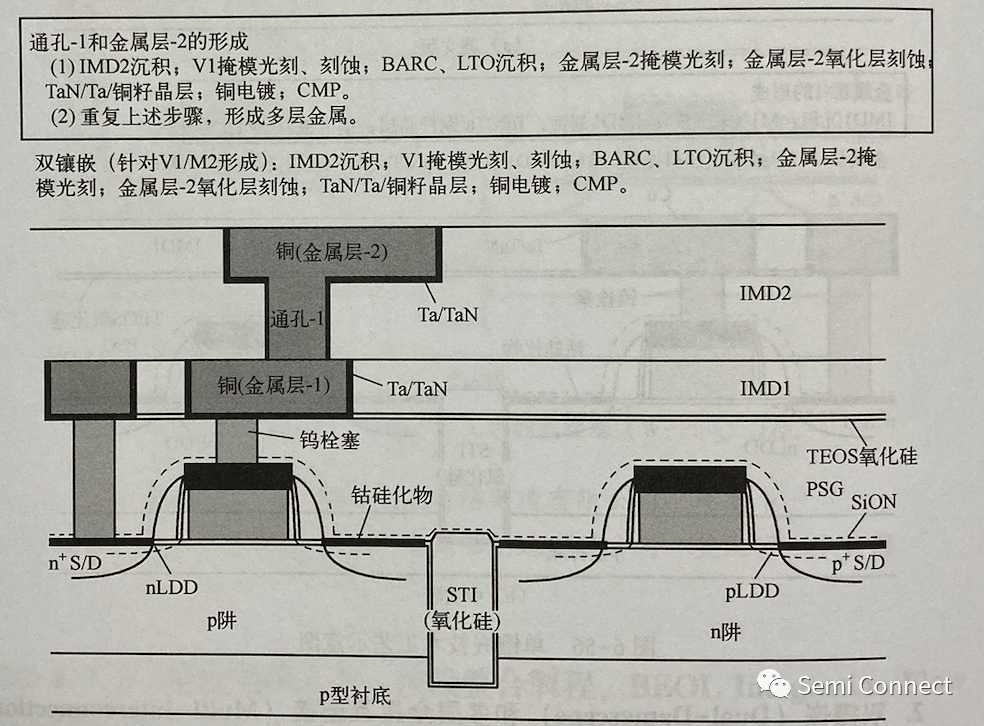

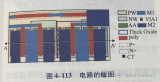

雙鑲嵌 (Dual-Damascene)和多層金屬互連接 (Multi-Interconnection)通孔-1(V1)和金屬-2 (M2)互連的形成是通過(guò)雙鑲嵌 (Dual -Damascene)工藝實(shí)現(xiàn)的,如圖所示。

雙鑲嵌工藝分為先通孔 (Via-First) 和先溝槽(Trench-First)兩種技術(shù)。以先通孔技術(shù)為例,首先沉積IMD2層(如 SiCN層,厚度約為 50nm,含碳低kPECVD 氧化硅黑金剛石層厚度約為 600nm),然后形成V1的圖形并進(jìn)行刻蝕。多層IMD1 的主要作用是提供良好的密封和覆蓋更加多孔的低k介質(zhì)。 為了平坦化,需要在通孔中填充底部抗反射涂層 (Bottom-Ani-Rellective Coatings, BARC),并沉積一層 LTO (Low Temperature Oxide)。隨后形成M2 的圖形并刻蝕氧化物,去除 BARC 并清洗后,沉積 Ta / TaN 阻擋層和 Cu 籽晶層,隨后進(jìn)行 Cu 填充(使用 ECP 法),并進(jìn)行 CMP 平坦化,這樣 M2 互連就形成了。 通過(guò)重復(fù)上述步驟,可以實(shí)現(xiàn)多層銅互連。相應(yīng)的,先溝槽技術(shù)的雙鑲嵌工藝就是先實(shí)施 M2 溝槽制備再形成 V1 的圖形并刻蝕氧化物,然后沉積阻擋層和籽晶層,最后進(jìn)行 Cu 填充和 CMP 平坦化。

審核編輯 :李倩

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

原文標(biāo)題:后段集成工藝(BEOL Integration Flow)- 2

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

相關(guān)推薦

后段刻蝕工藝(Back-End of Line ETCH,簡(jiǎn)稱(chēng)BEOL ETCH)作為集成電路制造的重要環(huán)節(jié),其復(fù)雜性與重要性毋庸置疑。 ? ? 什么是

![的頭像]() 發(fā)表于

發(fā)表于 12-31 09:44

?161次閱讀

芯片制造可分為前段(FEOL)晶體管制造和后段(BEOL)金屬互連制造。后段工藝是制備導(dǎo)線將前段制造出的各個(gè)元器件串連起來(lái)連接各晶體管,并分配時(shí)鐘和其他信號(hào),也為各種電子系統(tǒng)組件提供電

![的頭像]() 發(fā)表于

發(fā)表于 12-04 14:10

?1138次閱讀

AMD Alveo 加速卡使用有兩種流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比較常見(jiàn)的是 Vitis

![的頭像]() 發(fā)表于

發(fā)表于 11-13 10:14

?205次閱讀

IMD2 工藝與 IMD1工藝類(lèi)似。IMD2 工藝是指在第二層金屬與第三層金屬之間形成的介質(zhì)材料,形成電性隔離。

![的頭像]() 發(fā)表于

發(fā)表于 10-25 14:49

?196次閱讀

金屬層2(M2)工藝與金屬層1工藝類(lèi)似。金屬層2工藝是指形成第二層金屬互連線,金屬互連線的目的是

![的頭像]() 發(fā)表于

發(fā)表于 10-24 16:02

?287次閱讀

請(qǐng)問(wèn)TAS5754m在使用ROM flow時(shí),I2S可以支持到96KHz嗎?

發(fā)表于 10-22 08:28

近日,晶合集成在新工藝研發(fā)領(lǐng)域取得了重要突破。在2024年第三季度,晶合集成成功通過(guò)了28納米邏輯芯片的功能性驗(yàn)證,并順利點(diǎn)亮了TV,標(biāo)志著其28納米制程技術(shù)又邁出了堅(jiān)實(shí)的一步。

![的頭像]() 發(fā)表于

發(fā)表于 10-10 17:10

?541次閱讀

集成電路(IC)作為現(xiàn)代電子技術(shù)的核心,其制造工藝的復(fù)雜性和先進(jìn)性直接決定了電子產(chǎn)品的性能和質(zhì)量。對(duì)于有志于進(jìn)入集成電路行業(yè)的學(xué)習(xí)者來(lái)說(shuō),掌握一系列基礎(chǔ)知識(shí)是至關(guān)重要的。本文將從半導(dǎo)體物理與器件

![的頭像]() 發(fā)表于

發(fā)表于 09-20 13:46

?754次閱讀

的配置(我將附上 ErayDemo 和我的項(xiàng)目)。

通過(guò)調(diào)試,我得出結(jié)論:兩個(gè)模塊都卡在 INTEGRATION_LISTEN 狀態(tài)。

電氣連接圖片:

發(fā)表于 07-24 06:54

說(shuō)到數(shù)據(jù)集成(Data Integration),簡(jiǎn)單地將所有數(shù)據(jù)倒入數(shù)據(jù)湖并不是解決辦法。 在這篇文章中,我們將介紹如何輕松集成數(shù)據(jù)、鏈接不同來(lái)源的數(shù)據(jù)、將其置于合適的環(huán)境中,使其具有相關(guān)性并易于

![的頭像]() 發(fā)表于

發(fā)表于 04-22 17:59

?752次閱讀

虛擬半導(dǎo)體工藝建模是研究金屬線設(shè)計(jì)選擇更為經(jīng)濟(jì)、快捷的方法 作者:泛林集團(tuán) Semiverse Solutions 部門(mén)半導(dǎo)體工藝與整合部高級(jí)經(jīng)理 Daebin Yim l 由于阻擋層相對(duì)尺寸

![的頭像]() 發(fā)表于

發(fā)表于 04-09 17:11

?428次閱讀

鍺(Ge)探測(cè)器是硅基光電子芯片中實(shí)現(xiàn)光電信號(hào)轉(zhuǎn)化的核心器件。在硅基光電子芯片工藝中實(shí)現(xiàn)異質(zhì)單片集成高性能Ge探測(cè)器工藝,是光模塊等硅基光電子產(chǎn)品實(shí)現(xiàn)小體積、低成本和易制造的優(yōu)先選擇。

![的頭像]() 發(fā)表于

發(fā)表于 04-07 09:16

?1037次閱讀

近日,半導(dǎo)體封測(cè)領(lǐng)域的領(lǐng)軍企業(yè)日月光投控與知名芯片制造商英飛凌共同宣布,雙方已正式簽署收購(gòu)協(xié)議。根據(jù)該協(xié)議,日月光投控將以6258.9萬(wàn)歐元的價(jià)格,收購(gòu)英飛凌位于菲律賓甲美地市及韓國(guó)天安市的兩座后段封測(cè)廠。

![的頭像]() 發(fā)表于

發(fā)表于 02-25 11:11

?768次閱讀

近日,上海發(fā)布了《2023年上海科技進(jìn)步報(bào)告》,來(lái)自上海工研院的MEMS標(biāo)準(zhǔn)工藝模塊及90納米硅光集成工藝2項(xiàng)國(guó)際先進(jìn)水平技術(shù)成果入選。

![的頭像]() 發(fā)表于

發(fā)表于 02-22 09:42

?929次閱讀

HIM模塊,即Heterogeneous

Integration Module (HIM)異構(gòu)

集成模塊,將分開(kāi)制造的不同元件

集成到更高級(jí)別的組件中,可以增強(qiáng)功能并改進(jìn)工作特性,因此KOOM能夠?qū)⒉捎貌煌圃?/div>

![的頭像]() 發(fā)表于

發(fā)表于 01-08 14:55

?456次閱讀

后段集成工藝(BEOL Integration Flow)- 2

后段集成工藝(BEOL Integration Flow)- 2

評(píng)論