建筑集成定時電源(BITS)是網絡同步中廣泛使用的一種時鐘。它是需要同步的網絡內所有已部署設備的主定時電源。DS26504是BITS時鐘恢復元件,可用于這些應用。該器件的接收器部分可以從 T1、E1、64kHz 復合時鐘 (64KCC) 和 6312kHz 同步定時接口恢復時鐘。

DS26504的一個重要模塊是其抖動衰減器,它無需專用晶振即可工作,并使用MCLK工作。DS26504內置無晶振抖動衰減器,具有旁路模式,用于T1和E1工作。

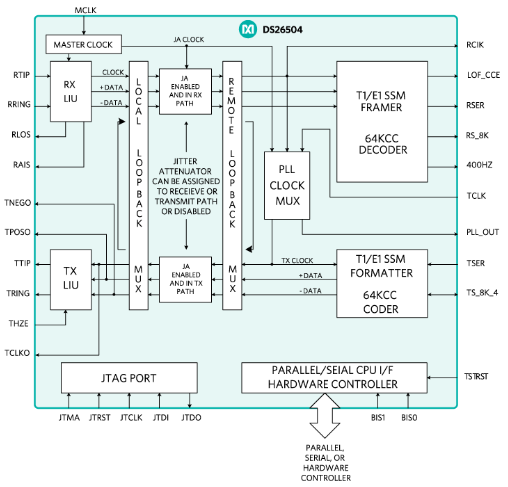

圖1所示的抖動衰減器可以插入發射或接收路徑。

圖1.DS26504原理框圖

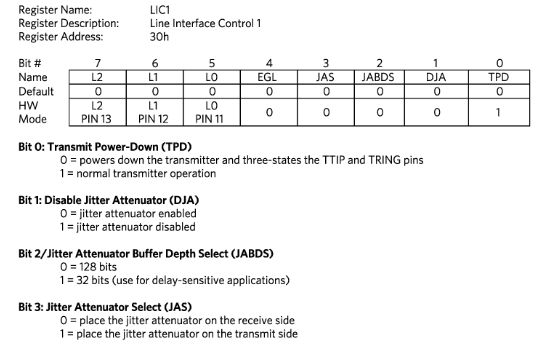

寄存器線路接口控制1(LIC1)(圖2)允許客戶選擇抖動衰減器的位置(在Rx或Tx路徑中),并打開或關閉抖動衰減器。此外,抖動衰減器可以通過JABDS位(LIC1.2)設置為32位或128位的深度。128 位模式用于預計會出現較大漂移偏移的應用程序。32 位模式用于延遲敏感型應用。

圖2.寄存器線接口控制 1 說明。

請注意,圖2中分層數字接口的物理和電氣特性在G.703 ITU同步標準中定義。

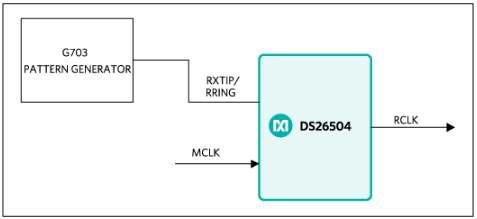

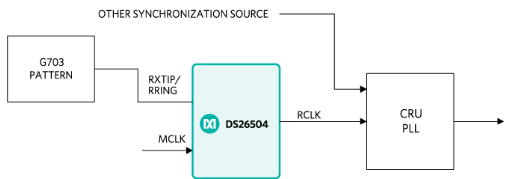

在本應用筆記中,如圖3所示,DS26504輸入信號表示為G.703,DS26504的主時鐘表示為MCLK,從輸入信號中恢復的時鐘命名為RCLK。

圖3.DS26504系統框圖

抖動衰減器操作

DS26504內部的抖動衰減器采用恒定平均延遲架構。這意味著輸入時鐘和主時鐘(MCLK)之間的頻率差會導致抖動衰減器為輸出時鐘選擇離散延遲。輸出時鐘延遲以 1 個 UI 步長發生,每 2ppm 的頻率差就會發生。由于主時鐘輸入通常來自晶體振蕩器(XO),因此主時鐘頻率隨溫度變化而變化。如果溫度變化足夠大,則頻率差達到輸出時鐘 (RCLK) 偏移 1 UI 的點。

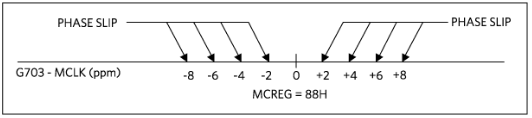

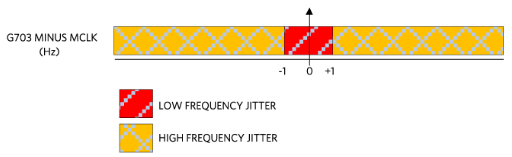

在這種情況下,如圖4所示,恢復時鐘(RCLK)每2ppm的頻率差就會解鎖并再次鎖定,這可以稱為“相位滑移”。如果主時鐘頻率穩定且輸入信號的頻率發生變化,則會出現相同的現象。

圖4.G.703 和 MCLK 之間的頻率差會在 RCLK 上產生相位滑移。

在諸如電信設備的定時單元等應用中,系統可以同步到輸入的G.703信號,當發生相位滑移并在數據通信中引入錯誤時,BITS輸入可能會被取消資格。

此外,如果在最大時間間隔誤差 (MTIE) 和時間偏差 (t開發) 使用長達 20 分鐘的觀察時間的測量,測試失敗。

因此,考慮到抖動清除可以從BITS之后的第二個PLL進行管理,建議在定時單元應用中保持抖動衰減器關閉,該PLL通常用于管理其他同步源(見圖5)。

圖5.DS26504在典型定時單元應用中的應用。

不使用抖動衰減器時,由于輸入信號采樣,恢復的信號會受到62.4ns范圍內的高頻抖動的影響(見圖6)。

圖6.當 G.703 和 MCLK 之間的頻率差大于 1Hz 時,恢復時鐘 (RCLK) 上的高頻抖動。

如圖7所示,G.703和MCLK之間的頻率差異非常小,在1Hz(0.5ppm)范圍內,會在RCLK上引入漂移(低頻抖動)。

圖7.抖動類型根據 G.703 和 MCLK 之間的頻率差異而變化。

雖然高頻抖動可以很容易地從后續PLL中消除,但其帶寬不足以消除漂移。

在此拐角條件下,影響RCLK的漂移會在最大時間間隔誤差(MTIE)和時間偏差(t開發) 測試。

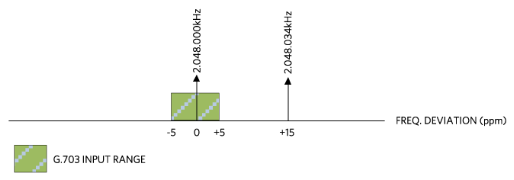

通過選擇頻率高于預期輸入信號范圍的信號作為主時鐘(MCLK),可以避免這種情況。例如,如圖8所示,假設輸入信號為2.048MHz±5ppm,為了避免漂移,主時鐘可以選擇為2.048MHz + 15ppm。

圖8.根據輸入信號范圍選擇MCLK頻率可以避免RCLK上的漂移。

通過這種安排,RCLK會受到高頻抖動的影響,而高頻抖動可以很容易地從PLL跟隨位中消除。

結論

在定時單元應用中,建議保持抖動衰減器關閉,以避免上述相位滑移。

為避免漂移,在抖動衰減器關閉的情況下,G.703信號和主時鐘(MCLK)之間的頻率差必須大于1Hz。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17706瀏覽量

249998 -

振蕩器

+關注

關注

28文章

3832瀏覽量

139049 -

寄存器

+關注

關注

31文章

5336瀏覽量

120260

發布評論請先 登錄

相關推薦

DS26504 pdf datasheet(時鐘恢復器件芯片

光衰減器,光衰減器的工作原理是什么?

光衰減器分類方式_光衰減器類型_光衰減器的原理

使用DS26504抖動衰減器的設計考慮

使用DS26504抖動衰減器的設計考慮

評論