第1節(jié) 什么是 FPGA

FPGA 的全稱為Field-Programmable Gate Array,即現(xiàn)場可編程門陣列。FPGA 是在 PAL、 GAL、 CPLD 等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物, 是作為專用集成電路( ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。簡而言之,FPGA 就是一個(gè)可以通過編程來改變內(nèi)部結(jié)構(gòu)的芯片。FPGA 功能實(shí)現(xiàn):需要通過編程即設(shè)計(jì)硬件描述語言,經(jīng)過 EDA 工具編譯、綜合、布局布線成后轉(zhuǎn)換為可燒錄的文件,最終加載到 FPGA 器件中去,改變 FPGA 內(nèi)部的連線,最終完成所實(shí)現(xiàn)的功能。FPGA 性能對(duì)比:FPGA 相比于單片機(jī)、 CPU 等集成電路芯片擁有效率更高、功耗更低的特點(diǎn),但是易于開發(fā)程度遠(yuǎn)遠(yuǎn)不如單片機(jī)、 CPU;在數(shù)字芯片設(shè)計(jì)領(lǐng)域, FPGA 雖然相比 ASIC 具有更短的開發(fā)周期與開發(fā)難度, 但是其存在著成本過高、性能較差并且在資源的利用率上遠(yuǎn)不及 ASIC 等問題,不能真正的替代 ASIC。

第2節(jié) FPGA 的基本結(jié)構(gòu)

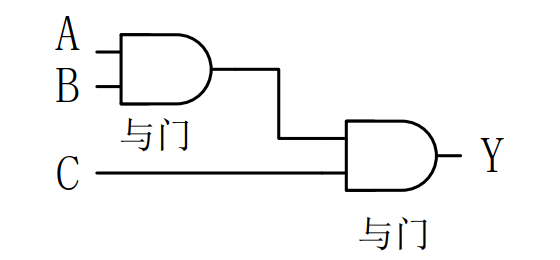

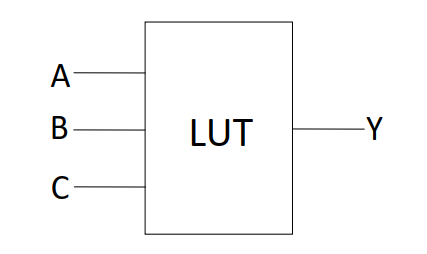

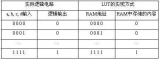

FPGA 可編程的特性決定了其實(shí)現(xiàn)數(shù)字邏輯的結(jié)構(gòu)不能像專用 ASIC 那樣通過固定的邏輯門電路來完成,而只能采用一種可以重復(fù)配置的結(jié)構(gòu)來實(shí)現(xiàn), 而查找表(LUT)可以很好地滿足這一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工藝的查找表結(jié)構(gòu)。FPGA 芯片參數(shù)指標(biāo):包含可編程邏輯模塊的數(shù)量、固定功能邏輯模塊(如乘法器)的數(shù)目及存儲(chǔ)器資源(如嵌入式 RAM)的大小。 在最底層的可配置邏輯模塊(如片上的邏輯單元) 上,存在著基本的兩種部件:觸發(fā)器和查找表( LUT), 而觸發(fā)器和查找表的組合方式不同,是各個(gè) FPGA 家族之間區(qū)別的重要依據(jù), 并且查找表本身的結(jié)構(gòu)也可能各不相同( 有 4 輸入或 6 輸入或其他)。 查找表( Look-Up-Table)簡稱為 LUT, 其本質(zhì)上就是一個(gè) RAM。目前 FPGA 內(nèi)部中多使用 4輸入的 LUT,每一個(gè) LUT 可以看成一個(gè)有4 位地址線的 RAM。 當(dāng)用戶在 EDA 工具上通過原理圖或 硬件描述語言設(shè)計(jì)了一個(gè)邏輯電路以后, FPGA 開發(fā)軟件會(huì)自動(dòng)計(jì)算邏輯電路的所有可能結(jié)果,并把真值表(即結(jié)果)事先寫入 RAM 中。這樣,每輸入一個(gè)信號(hào)進(jìn)行邏輯運(yùn)算就等于輸入一個(gè)地址進(jìn)行查找表操作, 通過地址找到對(duì)應(yīng)的 RAM 中的結(jié)果, 最后將其輸出。以實(shí)現(xiàn)數(shù)字邏輯 Y=A&B&C 的功能為例。如果是在專用 ASIC 中,為了實(shí)現(xiàn)該邏輯,邏輯門都已經(jīng)事先確定好, Y 的輸出值為兩個(gè)邏輯與運(yùn)算后的結(jié)果,其基本的實(shí)現(xiàn)結(jié)構(gòu)如下圖所示: 與門示意圖

對(duì)Y=A&B&C 的 利用FPGA 實(shí)現(xiàn)基本結(jié)構(gòu) :

與門示意圖

對(duì)Y=A&B&C 的 利用FPGA 實(shí)現(xiàn)基本結(jié)構(gòu) : 示意圖

示意圖第3節(jié) 更為復(fù)雜的 FPGA 架構(gòu)

隨著技術(shù)的發(fā)展和工藝節(jié)點(diǎn)的進(jìn)步, FPGA 的容量和性能在不斷提高的同時(shí), 其功耗卻不斷的優(yōu)化減少。2006 年以前四輸入查找表一直被廣泛使用, 在一些高端器件可能會(huì)用上六輸入、八輸入或更多輸入端口的查找表。而一個(gè)多輸入的查找表又可以分解成較小輸入的查找表, 即能夠分裂成許多更小的功能。例如一個(gè)八輸入的查找表可以分解成兩個(gè)四輸入的查找表或分解成一個(gè)三輸入加一個(gè)五輸入的查找表。在實(shí)際的高端器件中,這種可編程構(gòu)造可以描述相當(dāng)于百萬級(jí)(有時(shí)甚至千萬級(jí))的原始邏輯門。 在 FPGA 內(nèi)部,利用 FPGA 的可編程性在芯片內(nèi)部構(gòu)造實(shí)現(xiàn)了一個(gè)計(jì)數(shù)器邏輯,有著“軟內(nèi)核”與“硬內(nèi)核”之分。軟內(nèi)核(軟功能):在構(gòu)造計(jì)數(shù)器邏輯過程中使用到的功能便可以被稱為軟功能。硬內(nèi)核(硬功能):功能若是直接利用芯片實(shí)現(xiàn)的,則是利用了芯片內(nèi)部的硬功能。 軟內(nèi)核與硬內(nèi)核之間優(yōu)勢互補(bǔ),軟內(nèi)核的優(yōu)勢在于可以在利用芯片資源的基礎(chǔ)上利用編程設(shè)計(jì)讓其完成需要實(shí)現(xiàn)的任何功能(注意是數(shù)字功能,不包括模擬功能)。而硬內(nèi)核由于是實(shí)現(xiàn)固定功能的器件,因此其優(yōu)勢在于資源利用率高且功耗較低, 占用硅片的面積也較小, 并具有較高的性能。最重要的區(qū)別在于:與軟內(nèi)核相比硬內(nèi)核可用于實(shí)現(xiàn)模擬功能, 例如鎖相環(huán)的倍頻功能,這個(gè)功能需要在模擬電路下實(shí)現(xiàn),所以這一部分是在 FPGA 內(nèi)部用硬件來實(shí)現(xiàn)的 。第4節(jié) 帶嵌入式處理器的 FPGA

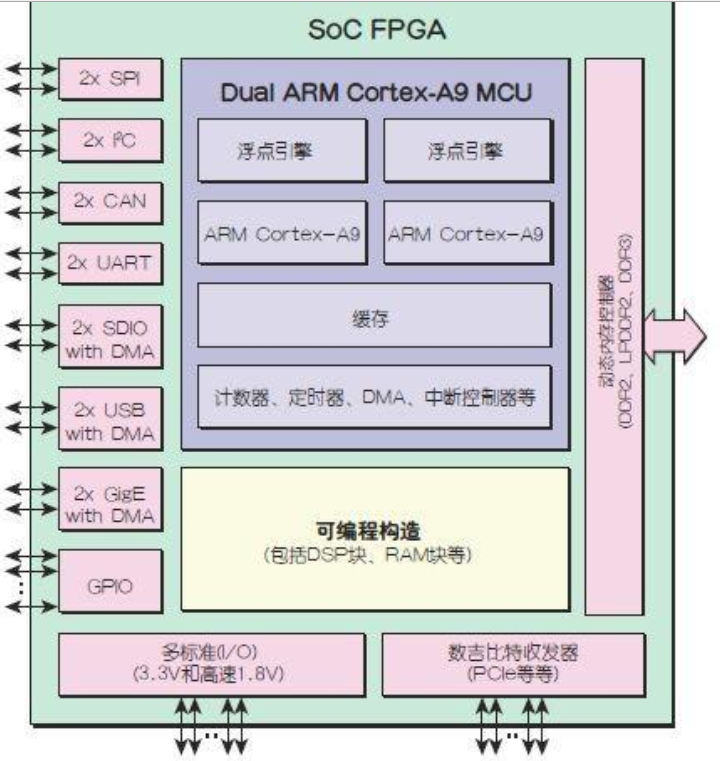

利用 FPGA 的可編程構(gòu)造實(shí)現(xiàn)的事情之一即為使用其中的一部分?jǐn)?shù)字邏輯資源制作一個(gè)或多個(gè)軟處理器內(nèi)核, 當(dāng)然, 也可以實(shí)現(xiàn)不同規(guī)模的處理器。 image-20211026193942002

這個(gè)芯片是一種新的SoC(System on Chip,系統(tǒng)級(jí)芯片) FPGA,完全以硬內(nèi)核方式實(shí)現(xiàn)的雙路 ARM Cortex-A9 微控制器子系統(tǒng)(運(yùn)行時(shí)鐘高達(dá) 1GHz,包含浮點(diǎn)引擎,片上緩存,計(jì)數(shù)器,定時(shí)器等)以及種類廣泛的硬內(nèi)核接口功能( SPI, I2C, CAN等),還有一個(gè)硬內(nèi)核的動(dòng)態(tài)內(nèi)存控制器,所有這些組件都利用大量傳統(tǒng)的可編程構(gòu)造和大量的通用輸入輸出( GPIO)引腳進(jìn)行了性能增強(qiáng)。

image-20211026193942002

這個(gè)芯片是一種新的SoC(System on Chip,系統(tǒng)級(jí)芯片) FPGA,完全以硬內(nèi)核方式實(shí)現(xiàn)的雙路 ARM Cortex-A9 微控制器子系統(tǒng)(運(yùn)行時(shí)鐘高達(dá) 1GHz,包含浮點(diǎn)引擎,片上緩存,計(jì)數(shù)器,定時(shí)器等)以及種類廣泛的硬內(nèi)核接口功能( SPI, I2C, CAN等),還有一個(gè)硬內(nèi)核的動(dòng)態(tài)內(nèi)存控制器,所有這些組件都利用大量傳統(tǒng)的可編程構(gòu)造和大量的通用輸入輸出( GPIO)引腳進(jìn)行了性能增強(qiáng)。第5節(jié) 數(shù)據(jù)存儲(chǔ)以及配置方式

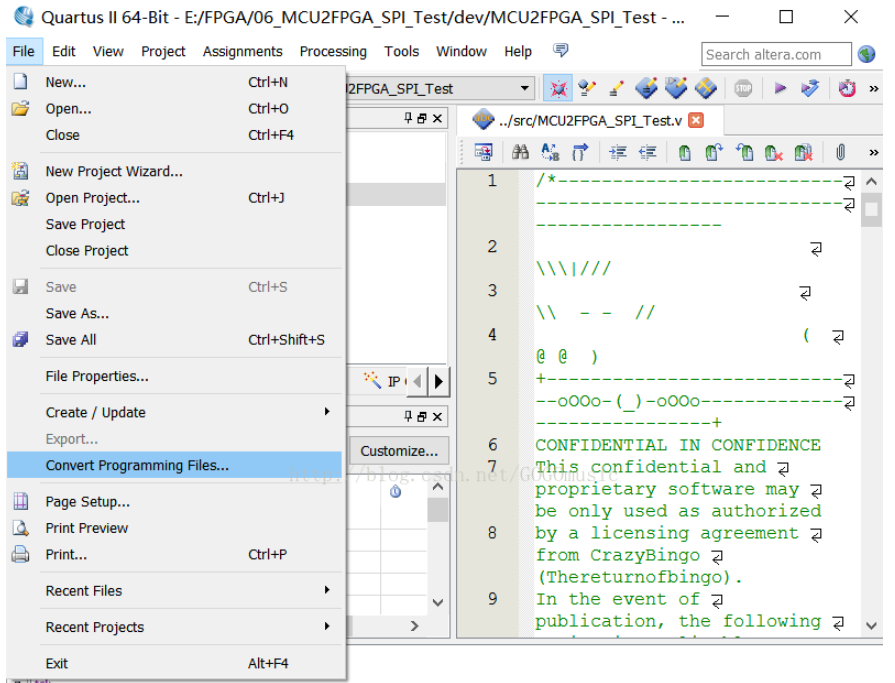

在 FPGA 內(nèi)部存在著存儲(chǔ)單元片內(nèi) RAM 塊,數(shù)據(jù)是存放在 RAM 中并由其來設(shè)置工作狀態(tài)的,若想要 FPGA 進(jìn)行工作,就需要對(duì)片內(nèi) RAM 進(jìn)行編程。而如果外部有大量數(shù)據(jù)交互時(shí),就要通過增加外設(shè)來對(duì)數(shù)據(jù)進(jìn)行暫時(shí)性的存儲(chǔ),如 SDRAM 存儲(chǔ)器或者 DDR3 存儲(chǔ)器,暫存在外設(shè)中的數(shù)據(jù)最終也是要通過 FPGA 內(nèi)部的 RAM 進(jìn)行存儲(chǔ)與處理。當(dāng)在 EDA 工具上將程序設(shè)計(jì)完成之后,便需要將軟件上的程序燒錄進(jìn) FPGA 內(nèi)部。通過不同的配置模式, FPGA 便會(huì)有不同的編程方式。常用的幾種配置模式:- 并行模式:通過并行 PROM(Programmable read-only memory,可編程只讀存儲(chǔ)器)、 Flash (Macromedia Flash。多媒體軟件平臺(tái))配置 FPGA;

- 主從模式:使用一片 PROM 配置多片 FPGA;

- 串行模式:串行 PROM 配置 FPGA;

- 外設(shè)模式:將 FPGA 作為微處理器的外設(shè),由微處理器對(duì)其編程。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603046 -

可編程門陣列

+關(guān)注

關(guān)注

0文章

18瀏覽量

7772

原文標(biāo)題:什么是FPGA?

文章出處:【微信號(hào):南山掃地僧,微信公眾號(hào):南山掃地僧】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文讀懂FPGA與CPLD的區(qū)別

特定的電路結(jié)構(gòu),完成一定的功能。

2.FPGA:FPGA通常包含三類可編程資源:可編程邏輯功能塊、可編程I/O塊和可編程互連。

發(fā)表于 09-26 16:38

?9w次閱讀

一文讀懂FPGA固化

在Configuration d e vi ce 下拉列表框中根據(jù)實(shí)際設(shè)計(jì)選擇被編程目標(biāo)器件,對(duì)于EP3C8 選擇EPCS16 。這個(gè)型號(hào)根據(jù)板子上的型號(hào)選擇。

發(fā)表于 04-27 16:52

?5286次閱讀

一文讀懂FPGA中的除法運(yùn)算及初識(shí)AXI總線

FPGA中的硬件邏輯與軟件程序的區(qū)別,相信大家在做除法運(yùn)算時(shí)會(huì)有深入體會(huì)。若其中一個(gè)操作數(shù)為常數(shù),可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運(yùn)算會(huì)占用較多的資源,電路結(jié)構(gòu)復(fù)雜,且

發(fā)表于 05-18 01:15

?4735次閱讀

一文讀懂FPGA

一文讀懂FPGA

評(píng)論