國產(chǎn)封測廠商正在Chiplet(小芯粒)技術(shù)方向上加速奔跑。

1月5日,長電科技(600584.SH)在其公眾號上宣布,公司XDFOIChiplet高密度多維異構(gòu)集成系列工藝已按計劃進(jìn)入穩(wěn)定量產(chǎn)階段,同步實(shí)現(xiàn)國際客戶4nm節(jié)點(diǎn)多芯片系統(tǒng)集成封裝產(chǎn)品出貨,最大封裝體面積約為1500mm2的系統(tǒng)級封裝。而早在一年之前,另一家國產(chǎn)封測巨頭通富微電就已經(jīng)在2021年年報中宣布,公司已大規(guī)模生產(chǎn)Chiplet產(chǎn)品,7nm產(chǎn)品已大規(guī)模量產(chǎn),5nm產(chǎn)品已完成研發(fā)即將量產(chǎn)。

在摩爾定律已接近極致的當(dāng)下,Chiplet技術(shù)由于可以有效的平衡芯片效能、成本以及良率之間的關(guān)系,近年來深受人們關(guān)注。尤其是在***遭遇種種技術(shù)封鎖的背景下,人們對于***通過Chiplet技術(shù)繞開先進(jìn)制程領(lǐng)域遭到的封鎖飽含期待。

不過,記者在采訪中了解到,先進(jìn)封裝并不能完全取代先進(jìn)制程的作用,但確實(shí)能夠在一定程度上突破封鎖。“相比SoC,小芯粒具有以下特點(diǎn):可以重復(fù)使用的IP,異構(gòu)集成,高良率。這些特點(diǎn)可以降低傳統(tǒng)封裝的成本,在某種條件下可以降低對先進(jìn)制程的依賴程度,但依然對先進(jìn)工藝有較高要求。”深度科技研究院院長張孝榮對《華夏時報》記者表示。

國產(chǎn)封測企業(yè)競速Chiplet

1月5日,長電科技宣布,公司XDFOI Chiplet高密度多維異構(gòu)集成系列工藝已按計劃進(jìn)入穩(wěn)定量產(chǎn)階段,同步實(shí)現(xiàn)國際客戶4nm節(jié)點(diǎn)多芯片系統(tǒng)集成封裝產(chǎn)品出貨,最大封裝體面積約為1500mm2的系統(tǒng)級封裝。

所謂Chiplet,通常被翻譯為“粒芯”或“小芯片”,單從字面意義上可以理解為“粒度更小的芯片”。它是一種在先進(jìn)制程下提升芯片的集成度,在不改變制程的前提下提升算力,并保證芯片制造良品率的一種手段。在當(dāng)下,Chiplet技術(shù)被認(rèn)為是在摩爾定律接近極致的情況下繼續(xù)提高芯片性能的希望所在。

傳統(tǒng)的系統(tǒng)級單芯片(SoC)將多個負(fù)責(zé)不同類型計算任務(wù)的計算單元,通過光刻的形式制作到同一塊晶圓上。隨著先進(jìn)工藝節(jié)點(diǎn)不斷演進(jìn),單顆芯片上可容納的晶體管數(shù)量及單位面積性能不斷提升。以 80mm面積的芯片裸片為例,在16nm工藝節(jié)點(diǎn)下,單顆裸片可容納的晶體管數(shù)量為21.12 億個;在7nm工藝節(jié)點(diǎn)下,該晶體管數(shù)量可增長到69.68億個。然而隨著半導(dǎo)體工藝的進(jìn)步,在同等面積大小的區(qū)域里,擠進(jìn)越來越多的硅電路,漏電流增加、散熱問題大、時鐘頻率增長減慢等問題難以解決,芯片設(shè)計的難度和復(fù)雜度也在進(jìn)一步增加。隨著半導(dǎo)體工藝節(jié)點(diǎn)越來越接近物理極限,每一代半導(dǎo)體工藝節(jié)點(diǎn)提升對于芯片性能帶來的收益也越來越小。

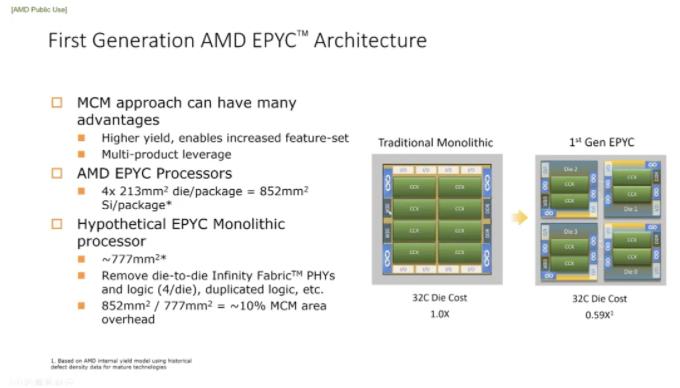

而Chiplet技術(shù),在封裝系統(tǒng)里面不再使用少量的大芯片做集成,而是改用數(shù)量更多但是尺寸更小的芯片粒(Chiplet)作為基本單位。其實(shí)現(xiàn)原理如同搭積木一樣,把一些預(yù)先在工藝線上生產(chǎn)好的實(shí)現(xiàn)特定功能的芯片裸片,再將這些模塊化的小芯片(裸片)互連起來,通 過先進(jìn)的集成技術(shù)(如3D集成等)集成封裝在一起,從而形成一個異構(gòu)集成系統(tǒng)芯片。

“Chiplet 封裝帶來的是對傳統(tǒng)片上系統(tǒng)集成模式的革新,主要表現(xiàn)在:1,良率提升:降低單片晶圓集成工藝良率風(fēng)險,達(dá)到成本可控,有設(shè)計彈性,可實(shí)現(xiàn)芯片定制化;2,Chiplet將大尺寸的多核心的設(shè)計,分散到較小的小芯片,更能滿足現(xiàn)今高效能運(yùn)算處理器的需求;3,彈性的設(shè)計方式不僅提升靈活性,且可實(shí)現(xiàn)包括模塊組裝、芯片網(wǎng)絡(luò)、異構(gòu)系統(tǒng)與元件集成四個方面的功能,從而進(jìn)一步降低成本(例如某些對于邏輯性能需求不高的模組可以使用成熟工藝)并提升性能。”長江證券分析師楊洋指出,基于小芯片的面積優(yōu)勢,Chiplet 可以大幅提高大型芯片的良率。目前在高性能計算、AI等方面的巨大運(yùn)算需求,推動了邏輯芯片內(nèi)的運(yùn)算核心數(shù)量快速上升,與此同時,配套的SRAM容量、I/O數(shù)量也在大幅提升,使得整個芯片不僅晶體管數(shù)量暴漲,芯片的面積也不斷增大。通過Chiplet設(shè)計將大芯片分成更小的芯片可以有效改善良率,同時也能夠降低因?yàn)椴涣悸识鴮?dǎo)致的成本增加,多芯片集成在越先進(jìn)工藝下(如5nm)越具有顯著的優(yōu)勢,因?yàn)樵?00mm面積的單片系統(tǒng)中,硅片缺陷導(dǎo)致的額外成本占總制造成本的50%以上。

在Chiplet(小芯粒)技術(shù)方向上投入心血的不只是長電科技。另一家國產(chǎn)封測巨頭通富微電早在2021年年報時就宣布,公司已大規(guī)模生產(chǎn)Chiplet產(chǎn)品,7nm產(chǎn)品已大規(guī)模量產(chǎn),5nm產(chǎn)品已完成研發(fā)即將量產(chǎn)。“公司技術(shù)實(shí)力上升到一個前所未有的高度。”通富微電當(dāng)時如是表示。對于其目前的進(jìn)展,通富微電相關(guān)人士表示較2021年年報時已有提升,但目前還沒到發(fā)布的時候。

能否突破技術(shù)封鎖?

對于中國芯片行業(yè)來說,Chiplet的意義不只在于提升芯片性能,更承載了突破技術(shù)封鎖的希望。

近年來,美國對我國的芯片限制不斷收緊。2022年8月,美國限制3納米以下芯片設(shè)計EDA軟件出口;9月,要求英偉達(dá)和AMD段斷供高性能GPU芯片;10月,全方位限制先進(jìn)芯片技術(shù)和設(shè)備的出口,被稱為歷史最嚴(yán)出口管制新規(guī)。在這一背景下,Chiplet意味著彎道超車的希望。

“先進(jìn)封裝的出現(xiàn)讓業(yè)界看到了通過封裝技術(shù)推動芯片高密度集成、性能提升、體積微型化和成本下降的巨大潛力,成為推動集成電路產(chǎn)業(yè)發(fā)展的關(guān)鍵力量之一。”長電科技董事、首席執(zhí)行長鄭力如是表示。

2022年12月16日舉辦的“第二屆中國互連技術(shù)與產(chǎn)業(yè)大會”上,首個由中國集成電路領(lǐng)域相關(guān)企業(yè)和專家共同主導(dǎo)制定的《小芯片接口總線技術(shù)要求》團(tuán)體標(biāo)準(zhǔn),正式通過工信部中國電子工業(yè)標(biāo)準(zhǔn)化技術(shù)協(xié)會的審定并發(fā)布。上述標(biāo)準(zhǔn)的制定,旨在為中國半導(dǎo)體廠商在chiplet領(lǐng)域的發(fā)展制定相對統(tǒng)一的標(biāo)準(zhǔn),提高來自不同制造商的小芯片之間的互操作性。這是中國首個原生Chiplet技術(shù)標(biāo)準(zhǔn),對于中國集成電路產(chǎn)業(yè)延續(xù)“摩爾定律”,突破先進(jìn)制程工藝限制具有重要意義。

“未來Chiplet產(chǎn)業(yè)會逐漸成熟,形成包括互聯(lián)接口、架構(gòu)設(shè)計、制造、先進(jìn)封裝、基板等完整產(chǎn)業(yè)鏈,中國廠商面臨巨大發(fā)展機(jī)遇。短期內(nèi),各Chiplet廠商會通過自重用和自迭代利用這項技術(shù)的多項優(yōu)勢,而在接口、協(xié)議、工藝都更加開放和成熟的未來,產(chǎn)業(yè)鏈的各環(huán)節(jié)都將迎來換血。我們看好由Chiplet帶動的后摩爾時代下產(chǎn)業(yè)鏈整合機(jī)會,將體現(xiàn)在需求端創(chuàng)新及商業(yè)模式升級下的重估,封裝測試、封測設(shè)備、IC載板、IP/EDA企業(yè)都將迎來新的增長機(jī)遇。”楊洋認(rèn)為。

不過,記者在采訪中了解到,Chiple并不能完全替代先進(jìn)制程的作用。“Chiple的意義我覺得在于兩點(diǎn):一是,并不是所有IP模塊都需要先進(jìn)制程,某些模塊用成熟制程就可以支撐,Chiple可以把先進(jìn)制程與成熟制程封裝在一起,降低芯片的成本;二是,Chiple可以把相對較高nm數(shù)的芯片封裝出低nm數(shù)芯片的性能,但是在功耗上與先進(jìn)制程相比還是不足。在某些領(lǐng)域,對功耗、散熱要求不高的時候,Chiple作用更大。但在消費(fèi)芯片領(lǐng)域,比如手機(jī)用的芯片,Chiple技術(shù)暫時還不能實(shí)現(xiàn)較高nm數(shù)的芯片對低nm數(shù)芯片的替代。”一位半導(dǎo)體行業(yè)的從業(yè)者對《華夏時報》記者表示,中國半導(dǎo)體在大力拓展先進(jìn)封裝技術(shù)的同時,也需要在先進(jìn)制造方面努力發(fā)展,從而才能真正實(shí)現(xiàn)大的跨越。

“小芯粒技術(shù)是芯片封裝技術(shù),不是制造工藝。芯片生產(chǎn)可以分成設(shè)計制造和封測三個環(huán)節(jié),小芯粒是相對過去廠商普遍采用的SoC方式發(fā)展起來的一種可降低成本的封裝技術(shù)。相比SoC,小芯粒具有以下特點(diǎn):可以重復(fù)使用的IP,異構(gòu)集成,高良率。這些特點(diǎn)可以降低傳統(tǒng)封裝的成本,在某種條件下可以降低對先進(jìn)制程的依賴程度,但依然對先進(jìn)工藝有較高要求。”張孝榮表示。

審核編輯 :李倩

-

摩爾定律

+關(guān)注

關(guān)注

4文章

634瀏覽量

79003 -

芯片技術(shù)

+關(guān)注

關(guān)注

1文章

159瀏覽量

17511 -

chiplet

+關(guān)注

關(guān)注

6文章

431瀏覽量

12587

原文標(biāo)題:國產(chǎn)封測廠商競速Chiplet,能否突破芯片技術(shù)封鎖?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Cadence推出基于Arm的系統(tǒng)Chiplet

Chiplet技術(shù)有哪些優(yōu)勢

芯和半導(dǎo)體將出席SiP及先進(jìn)半導(dǎo)體封測技術(shù)論壇

最新Chiplet互聯(lián)案例解析 UCIe 2.0最新標(biāo)準(zhǔn)解讀

IMEC組建汽車Chiplet聯(lián)盟

國產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車”!

突破與解耦:Chiplet技術(shù)讓AMD實(shí)現(xiàn)高性能計算與服務(wù)器領(lǐng)域復(fù)興

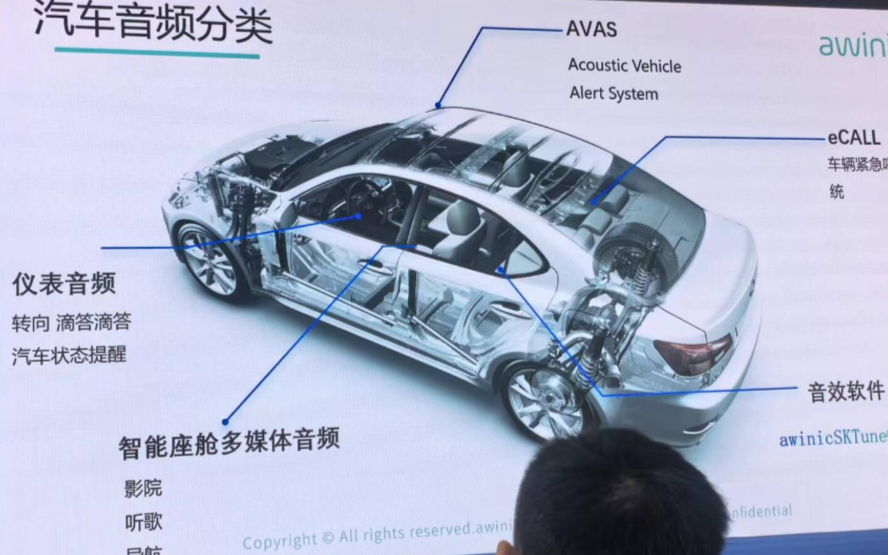

車載功放國產(chǎn)化率沒到2%!車載音頻市場高達(dá)900億,國產(chǎn)廠商如何破局

什么是Chiplet技術(shù)?

Chiplet技術(shù)對英特爾和臺積電有哪些影響呢?

深入分析評估GPU算力需求

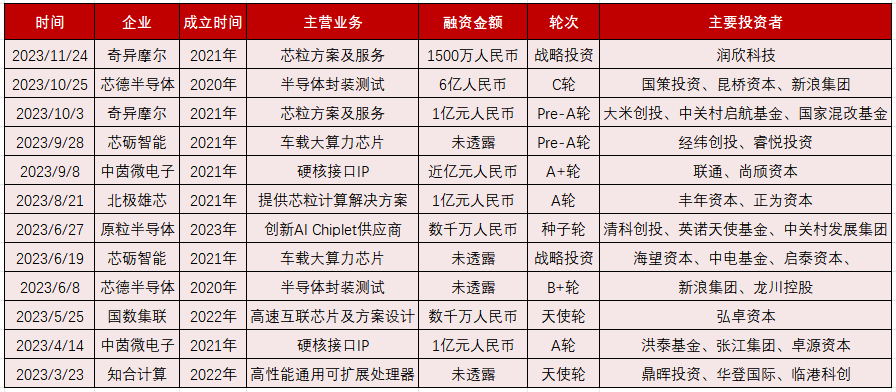

2023年Chiplet發(fā)展進(jìn)入新階段,半導(dǎo)體封測、IP企業(yè)多次融資

國產(chǎn)封測廠商競速Chiplet,能否突破芯片技術(shù)封鎖?

國產(chǎn)封測廠商競速Chiplet,能否突破芯片技術(shù)封鎖?

評論