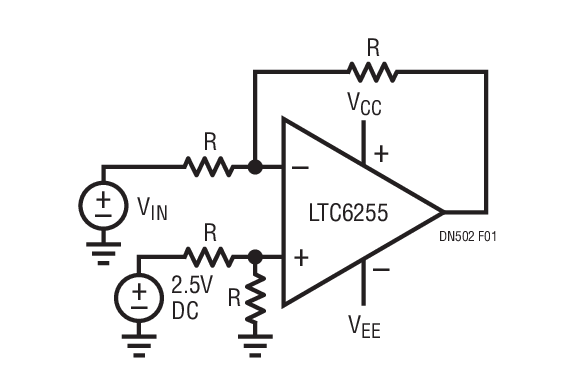

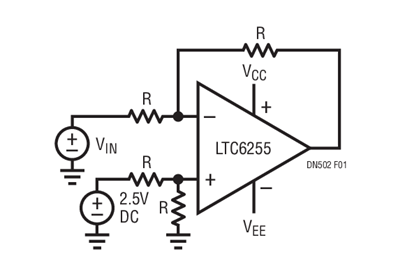

一些理想的運算放大器配置假設反饋電阻表現出完美匹配。實際上,電阻非理想性會影響各種電路參數,例如共模抑制比(CMRR)、諧波失真和穩定性。例如,如圖1所示,配置為將以地為參考信號電平轉換至2.5V共模的單端放大器需要良好的CMRR。假設CMRR為34dB且無輸入信號,這款2.5V電平轉換器的輸出失調為50mV,甚至會壓倒12位ADC和驅動器的LSB和失調誤差。

圖1.用作電平轉換器的單端運算放大器

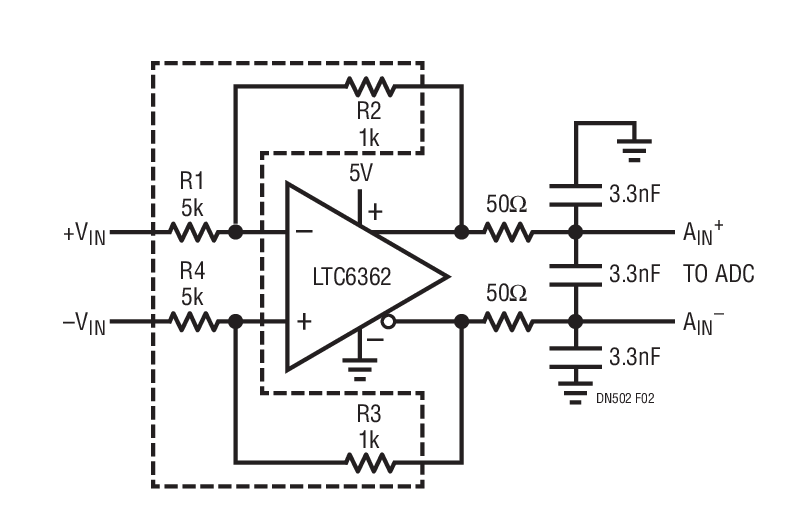

對于運算放大器,34dB的CMRR不太理想。但是,無論運算放大器的能力如何,1%容差電阻的反饋網絡都會將CMRR限制在34dB。高度匹配的電阻器(例如 LT5400 提供的電阻器)提供 0.01%、0.025% 和 0.05% 匹配,確保設計人員能夠接近或滿足放大器數據手冊的規格。本設計筆記比較了 LT5400 與厚膜、0402、1% 容差的表面貼裝電阻器。這些電阻器考慮了CMRR、諧波失真和穩定性,以提供LTC6362運放周圍的反饋,如圖2所示。

圖2.全差分運算放大器配置為V電壓外/V在= 0.2

共模抑制比

為了在存在共模噪聲的情況下獲得精確的測量結果,高CMRR非常重要。輸入CMRR定義為差分增益之比(V輸出(差異)/V在(差異)) 到輸入共模到差分轉換 (V輸出(差異)/V英寸(厘米)).

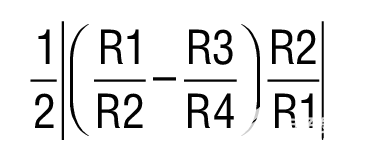

在理想的單端和全差分放大器中,只有輸入差分電平會影響輸出電壓。然而,在實際電路中,電阻失配限制了可用的CMRR。考慮將此電路配置為將±10V信號衰減為±2V信號。使用匹配度為2%(容差為1%)的典型表面貼裝電阻器,電阻器在最差情況下的CMRR貢獻為30dB。在0.01%容差和0.02%匹配的情況下,電阻的最差情況下CMRR貢獻為70dB。CMRR方程中的限制因素是:

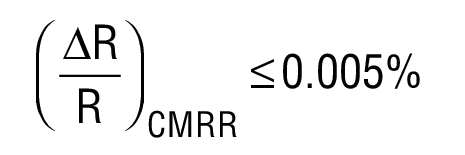

此表達式簡化為典型電阻器的電阻匹配比,但 LT5400 采取了一個額外的步驟,通過限制電阻對 R1/R2 和 R4/R3 之間的匹配來提供改進的 CMRR。通過將這個公式定義為 CMRR 的匹配,LT5400 提供了優于電阻器匹配比的準確度。例如,LT5400A 保證:

將最壞情況下的CMRR提高到82dB。

該電路的臺架測試得出了 50.7dB (高度電阻匹配限制) (采用 1% 容差電阻器)和 86.6dB (采用 LT5400)。在這種情況下,一個 2.5V 共模輸入將產生一個 1.5mV 的失調(采用 1% 厚膜電阻器)和一個 23μV 的失調(采用 LT5400)時,因而適合于直流準確度至關重要的 18 位 ADC 應用。

諧波失真

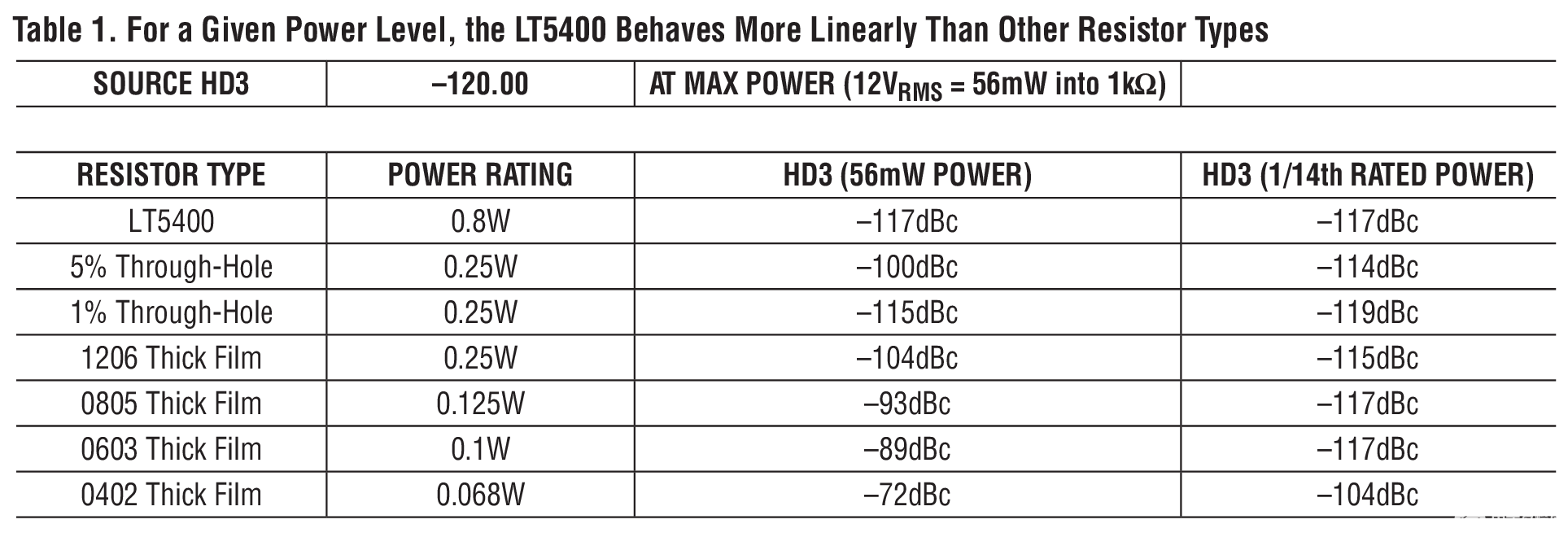

在為精密應用選擇電阻器時,諧波失真也很重要。電阻器兩端的大信號電壓可能會顯著改變電阻,具體取決于尺寸和材料。這個問題出現在許多基于芯片的電阻器中,并且隨著電阻器功率電平的增加而自然變得更加嚴重。表 1 比較了基于高功率驅動和類似功率驅動的厚膜、通孔和 LT5400 電阻器的失真。結果表明,對于給定信號,LT5400 對信號的失真遠小于其他電阻器類型。

穩定性

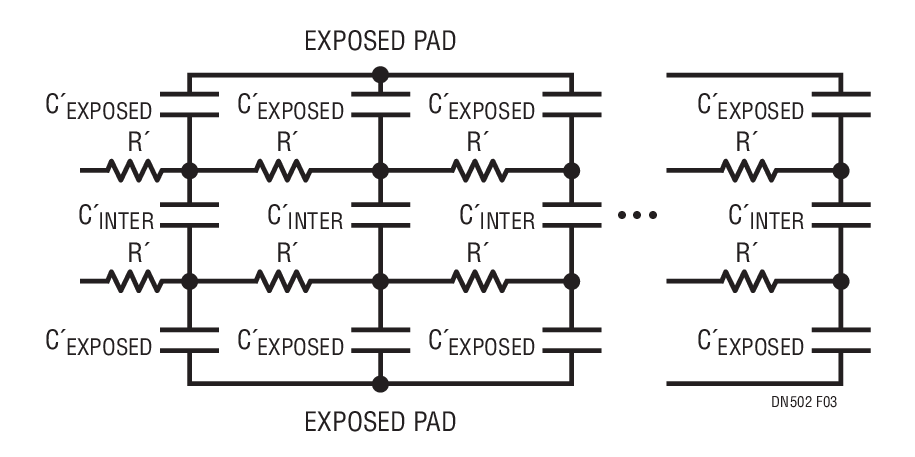

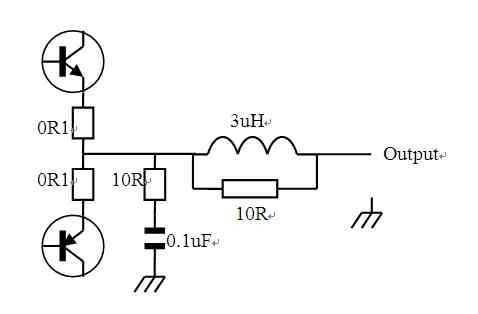

圖 3 示出了 LT5400 中電阻器之間的分布電容模型。為了實現 LT5400 中的高精度匹配和跟蹤,許多小型 SiCr 電阻器都采用串聯和并聯方式。由于復雜的叉,LT5400 電阻器可建模為一系列無窮小電阻器,在相鄰段之間以及各個段與裸露焊盤之間具有寄生電容。相比之下,典型的表面貼裝電阻器,如果沒有緊湊的布局,通常寄生電容明顯較低。

圖3.匹配電阻IC中分布電容的簡單模型。R′ 分量的總和產生一個等效的單個電阻器。C′的凈效應國米為1.4pF和C'的凈效應暴露為 5.5pF

當裸露焊盤接地時,電阻間電容的影響可以減輕。然而,即使在將裸露焊盤接地后,該電容仍然會通過形成總電阻乘以總電容的寄生極來影響電路穩定性。

由于過沖與相位裕量成反比,因此最小化階躍響應過沖是確保電路穩定性的好方法。與0402配置的17%相比,未補償的LT5400配置表現出27%的過沖。然而,實現 8% 過沖所需的補償電容器在兩種配置中大致相同:LT5400 為 18pF;15pF,帶 0402 電阻。在幾乎相同的補償下,兩個電路表現出相似的穩定性特性。

結論

精密放大器和ADC的實際性能通常難以實現,因為數據手冊規格假定是理想元件。精心匹配的電阻網絡(例如 LT5400 提供的電阻網絡)可實現比分立元件高出幾個數量級的精密匹配,從而確保滿足精準 IC 的數據手冊規格。

審核編輯:郭婷

-

放大器

+關注

關注

144文章

13720瀏覽量

214747 -

驅動器

+關注

關注

54文章

8365瀏覽量

147587 -

adc

+關注

關注

99文章

6565瀏覽量

546606

發布評論請先 登錄

相關推薦

超精密電阻在運算放大器電路中的應用

差動放大器:良好匹配電阻器不可或缺的器件

超精密電阻在運算放大器電路中的應用

超精密電阻在運算放大器電路中的應用

應用于運算放大器中的精密匹配電阻網絡

用于精密放大器應用的匹配電阻網絡

用于精密放大器應用的匹配電阻網絡

評論