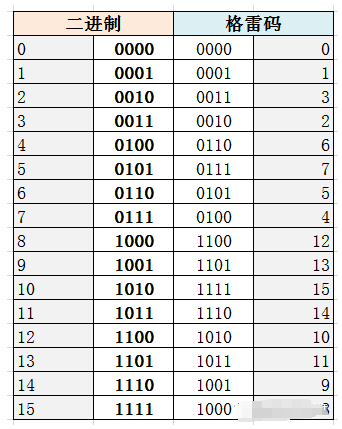

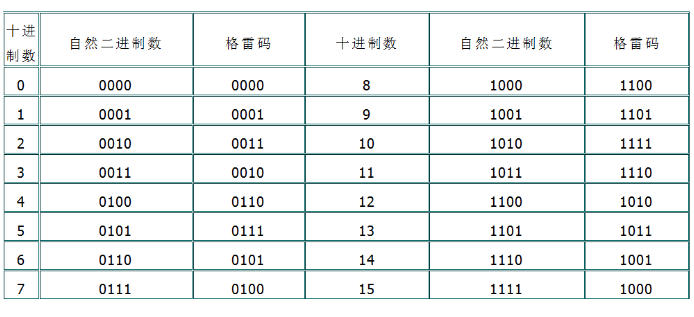

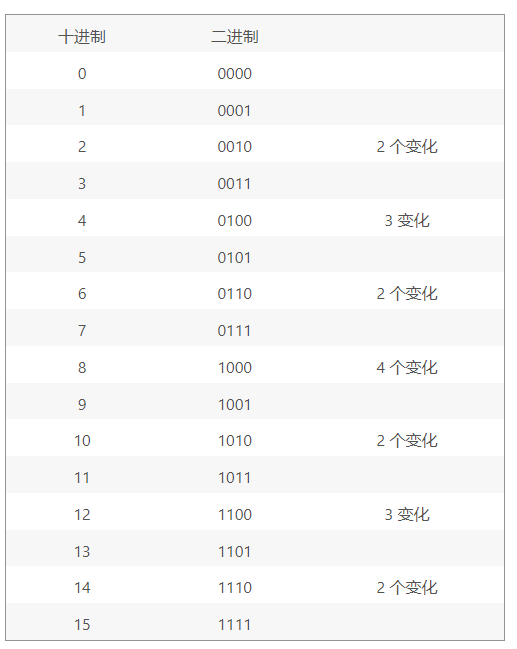

格雷碼是一種循環二進制編碼,特點是相鄰數變化時只有一位數據跳變。

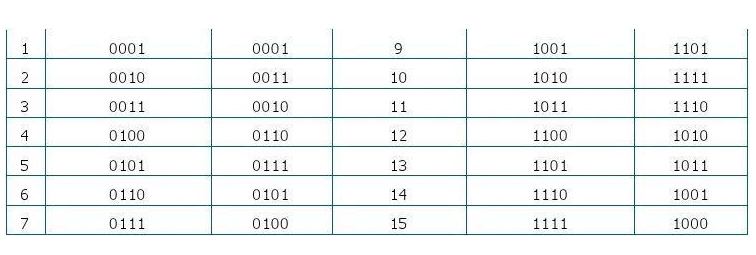

- 4位二進制和格雷碼對應如下:

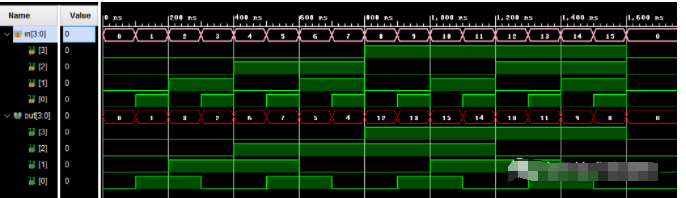

1、二進制到格雷碼轉換

- Verilog實現

1module bin_to_gray

2#(

3 parameter WIDTH = 4

4)

5(

6 input [WIDTH-1:0] in,

7 output [WIDTH-1:0] out

8);

9

10assign out = in ^ (in >> 1);

11

12endmodule

- 仿真波形:

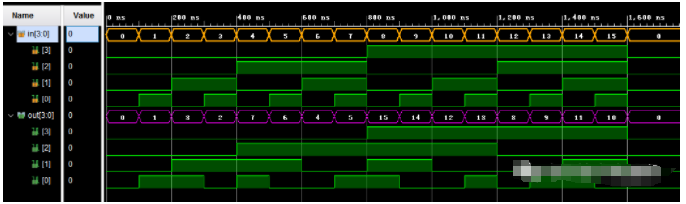

2、格雷碼轉二進制

- Verilog實現:

1module gray_to_bin

2#(

3 parameter WIDTH = 4

4)

5(

6 input [WIDTH-1:0] in,

7 output [WIDTH-1:0] out

8);

9

10// assign out[0] = ^in[3:0];

11// assign out[1] = ^in[3:1];

12// assign out[2] = ^in[3:2];

13// assign out[3] = in[3];

14

15genvar i;

16generate

17 assign out[WIDTH-1] = in[WIDTH-1];

18 for(i=0; i1; i=i+1) begin

19 assign out[i] = ^in[WIDTH-1:i];

20 end

21endgenerate

- 仿真波形:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

二進制

+關注

關注

2文章

807瀏覽量

42352 -

仿真

+關注

關注

52文章

4297瀏覽量

135994 -

Verilog

+關注

關注

29文章

1367瀏覽量

112365 -

格雷碼

+關注

關注

2文章

34瀏覽量

13410 -

二進制編碼

+關注

關注

0文章

8瀏覽量

3252

發布評論請先 登錄

相關推薦

熱點推薦

二進制格雷碼與自然二進制碼的互換分析

其中采用循環二進制編碼的絕對式編碼器,其輸出信號是一種數字排序,不是權重碼,每一位沒有確定的大小,不能直接進行比較大小和算術運算,也不能直接轉換成其他信號,要經過一次碼變換,變成自然二進制碼

二進制碼詳解

的權為21=2,b2位的權為22=4,b3位的權為23=8,例: 0111= 0×8 + 1×4 + 1×2 + 1×1=7 一般情況下,十進制碼與二進制碼之間的關系可表示為:(N)D= b3 W3 + b2 W2 + b1

發表于 04-06 23:55

二進制到格雷碼轉換的Verilog HDL源代碼

電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中二進制到格雷碼轉換的功能實現源代碼。注意:程序運行在不同

發表于 10-15 11:52

?3868次閱讀

評論