1 引言

隨著半導體和芯片技術的飛速發展,現在的FPGA集成了越來越多的可配置邏輯資源、各種各樣的外部總線接口以及豐富的內部RAM資源,使其在國防、醫療、消費電子等領域得到了越來越廣泛的應用。當采用FPGA進行設計電路時,大多數FPGA對上電的電源排序和上電時間是有要求的,所以電源排序是需要考慮的一個重要的方面。通常情況下,FPGA供應商都規定了電源排序、上電時間的要求。因為一個FPGA所需要的電源軌數量會從3個到10個以上不等。通過遵循推薦的電源序列,可以避免在啟動期間吸取過大的電流,同時又可以防止器件受損壞。對一個FPGA的最小電路中的電源進行排序有多種方法。本文中主要以MP5650為例,來敘述把PGOOD引腳級聯至使能引腳來實現排序。

2. 研發案例

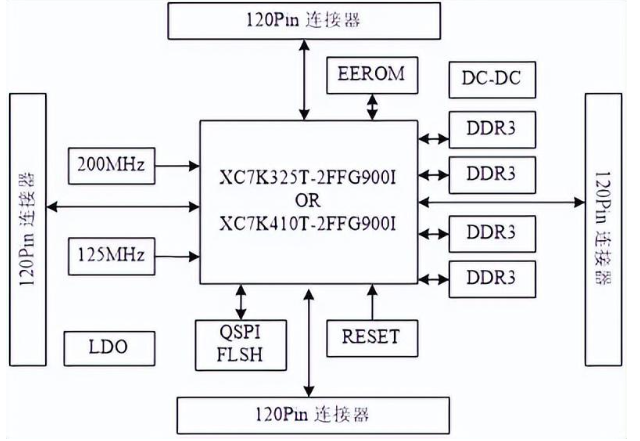

今天分享的案例是以明德揚公司研發的K7核心板,命名為MP5650為例。MP5650采用XILINX Kintex-7系列的XC7K325T-2FFG900I/XC7K410T-2FFG900I作為主控制器,在FPGA 芯片的HP 端口上掛載了4片DDR3存儲芯片,每片DDR3 容量高達512M 字節,每片16bit組成64bit 位的數據位寬。1片128Mb 的QSPI FLASH 芯片用來靜態存儲FPGA 芯片的配置文件或者其它用戶數據。核心板采用4個0.5mm間距120Pin 鍍金連接器與底板連接,核心板四個腳放置了4個3.5mm固定孔,此孔可以與底板通過螺絲緊固,確保了在強烈震動的環境下穩定運行。核心板結構尺寸為65(mm)× 85(mm)。整個開發系統的結構如圖1所示,實物圖如圖2所示。該板很適合高速數據通信;視頻采集、視頻輸出、消費電子;機器視覺、工業控制;項目研發前期驗證;電子信息工程、自動化、通信工程等電子類相關專業開發人員學習等領域及人群。

圖1 核心板結構圖

圖2 核心板實物圖

MP5650的K7FPGA所需要的電源軌如下:

(1)VCCINT

FPGA內部核心電壓。其不損壞FPGA器件的范圍為-0.5V~1.1V,正常工作電壓為0.97V~1.03V,推薦工作電壓為1.0V。

(2)VCCAUX

輔助供電電壓。其不損壞FPGA器件的范圍為-0.5V~2.0V。正常工作電壓為1.71V~1.89V。推薦工作電壓為1.8V。

(3)VCCBRAM

內部Block RAM的供電電壓。其不損壞FPGA器件的范圍為-0.5V~1.1V。正常工作電壓為0.97V~1.03V,推薦工作電壓為1.00V。

(4)VCCIO

對于HR BANK的接口電壓來說,需要與外部器件的信號電平保持一致,其不損壞FPGA器件的范圍為-0.5V~3.6V。正常工作電壓為1.14V~3.465V。推薦工作電壓與外部信號電平一致即可。對于HP BANK的接口電壓來說,需要與外部器件的信號電平保持一致,其不損壞FPGA器件的范圍為-0.5V~2.0V。正常工作電壓為1.14V~1.89V。推薦工作電壓與外部信號電平一致即可。

(5)VCCAUX_IO

IO輔助電壓。其不損壞FPGA器件的范圍為-0.5V~2.06V。正常工作電壓為1.14V~1.89V/2.06V。推薦工作電壓為1.8V/2V。

(6)VCCADC

XADC的供電電壓。其不損壞FPGA器件的范圍為-0.5V~2.0V。正常工作電壓為1.71V~1.89V。推薦工作電壓為1.80V。

(7)MGTAVCC

GTX收發器核心電壓。其不損壞FPGA器件的范圍為-0.5V~1.1V。正常工作電壓為0.97V~1.08V,推薦工作電壓為1.00V。

(8)MGTAVTT

GTX收發器終端匹配電壓。其不損壞FPGA器件的范圍為-0.5V~1.32V。正常工作電壓為1.17V~1.23V。推薦工作電壓為1.20V。

(9)MGTVCCAUX

GTX收發器輔助電壓。其不損壞FPGA器件的范圍為-0.5V~1.935V。正常工作電壓為1.75V~1.85V。推薦工作電壓為1.80V。

(10)MGTAVTTRCAL

GTX收發器校正電壓。其不損壞FPGA器件的范圍為-0.5V~1.32V。正常工作電壓為1.17V~1.23V。推薦工作電壓為1.20V。

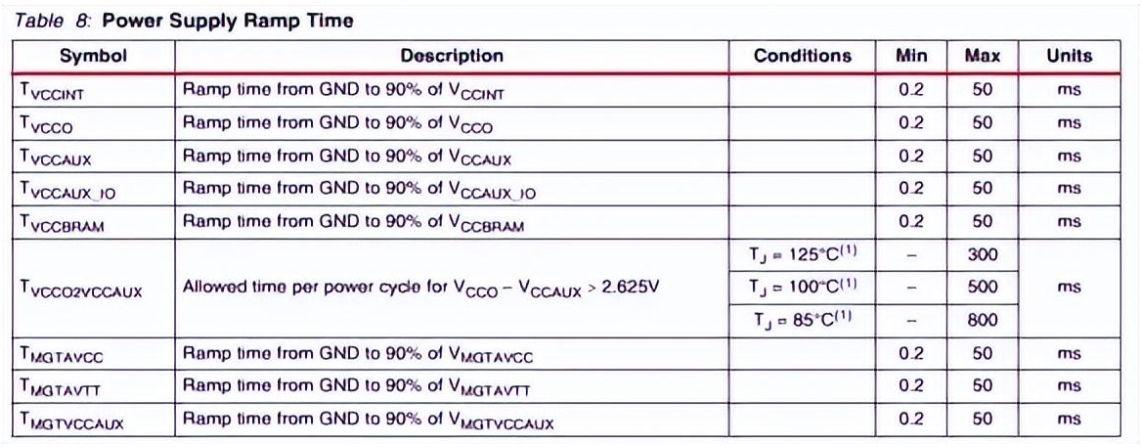

官方推薦的上電順序依次為VCCINT、VCCBRAM、VCCAUX、VCCAUX_IO、VCCO,斷電順序和上電順序正好相反。另外如果VCCINT和VCCBRAM電源軌一致,則可同時上電/斷電。VCCAUX_IO、VCCAUX與VCCO電源軌一致也可同時上電/斷電。其它電源軌則無上電順序。GTX收發器的上電順序為VCCINT、MGTAVCC、MGTAVTT或者MGTAVCC、VCCINT、MGTAVTT。斷電順序正好相反。MGTVCCAUX無順序。

3. MP5650電源排序方法

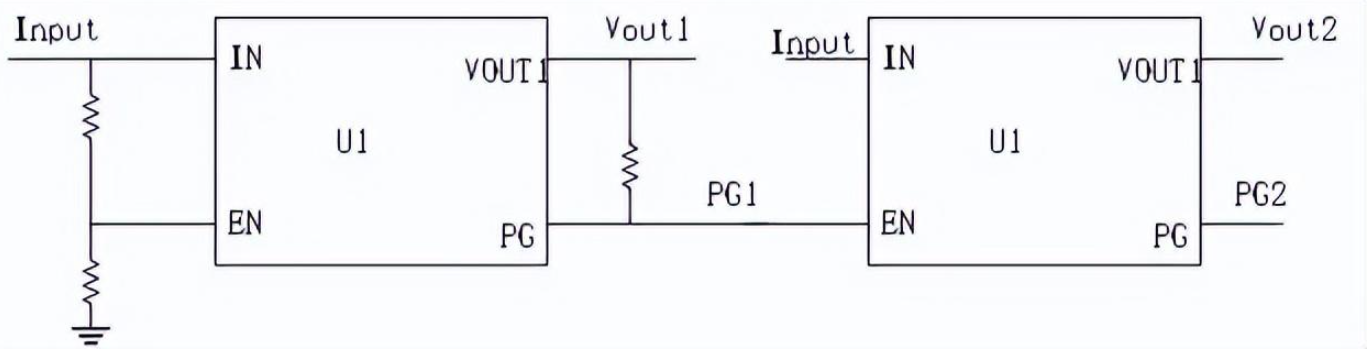

實現排序的一種方法是把一個電源的電源良好(PGOOD)管腳級聯至相繼的下一個電源的使能(EN)管腳,如圖3所示。在電源芯片在PG門限得到滿足時開始接通。該方法的優勢是成本低,但是無法輕松的控制定時。在EN管腳上增加電容在上電的級聯上引入定時延時。

圖3 把PGOOD引腳級聯至使能引腳示意圖

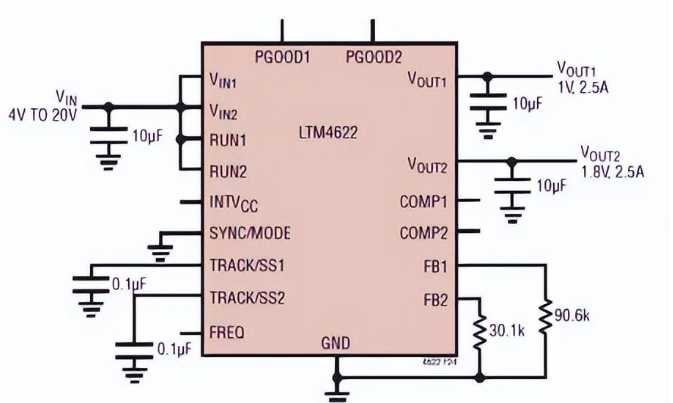

MP5650上選用的DC-DC電源芯片為LTM4628和LTNM4622,芯片的使用典型電路如圖4所示。芯片通過控制TRACK/SS管腳,通過給該管腳外加電容來改變上電時間。電容越小,上電時間越短。若FPGA電源級數較多較多,若每級上電時間較長,會導致電源總的上電時間過慢,超過官方給的最大值,導致無法啟動配置工作,FPGA工作不正常。官方提供的上電時間要求如圖5所示,最大不超過50ms。

圖4 LTM4628和LTNM4622芯片使用典型電路

圖5 官方提供的上電時間要求

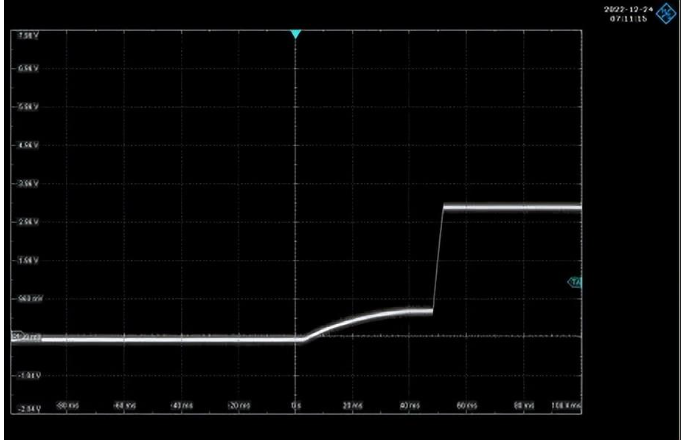

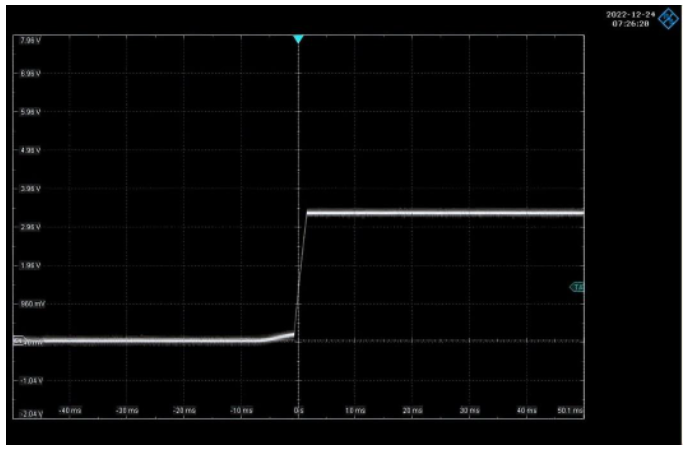

在我們最初的設計中TRACK/SS管腳電容選為0.1uF,我們發現經過四級級聯后,上電有時Flash配置芯片配置不成功,經示波器測試發現上電時間過長,超過了Xilinx要求的50ms,如圖6所示。經修改TRACK/SS管腳電容選為4.7nF后,上電時間大大縮短,如圖7所示,約為3ms。滿足了Xilinx上電時間要求,FPGA可以正常工作。設計中也可以將TRACK/SS管腳懸空,在默認情況下,上電時間有默認延時時間約為幾百微秒。

圖6 TRACK/SS管腳電容為0.1uF時,最后一級電源上電時間

4. 總結

總得來說,kintex7 FPGA電源結構比較復雜。目前用戶設計的7系列FPGA帶上電順序的電源方案常用各個電源芯片的輸入EN和輸出PGOOD來控制順序,上電時間需滿足Xilinx官方要求。通過開始描述,我們能夠清晰看到這個MP5650核心板所含有的接口和功能。對于需要大量IO的用戶,此核心板將是不錯的選擇。而且IO連接部分,同一個BANK管腳到連接器接口之間走線做了等長和差分處理,對于二次開發來說,非常適合。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21783瀏覽量

605023 -

電源設計

+關注

關注

31文章

1540瀏覽量

66494 -

Xilinx

+關注

關注

71文章

2170瀏覽量

121869

發布評論請先 登錄

相關推薦

Xilinx FPGA電源設計與注意事項

Xilinx FPGA電源設計與注意事項

評論