引言

碳化硅(SiC)作為第三代半導體材料,具有更寬的禁帶寬度、更高的擊穿電場、更高的熱導率等性能優勢,在高溫、高壓、高頻領域表現優異,已成為半導體材料技術領域的主要發展方向之一。SiC襯底主要包括導電型和半絕緣型兩類,二者在外延層及下游應用場景不同。導電型SiC襯底經過同質外延生長、器件制造可制成SiC二極管、金屬-氧化物半導體場效應晶體管(MOSFET)等功率器件,被應用于新能源汽車、光伏發電、軌道交通、智能電網、航空航天等領域[1];半絕緣型SiC襯底經過氮化鎵外延、器件制造可制成高電子遷移率晶體管(HEMT)等微波射頻器件,主要應用于5G通信、衛星、雷達等領域[2]。在半導體產業鏈中,襯底是晶圓制造的基礎,是所有半導體芯片的底層材料,主要起到物理支撐、導熱及導電作用,特別是在SiC功率半導體器件中,由于使用了同質外延,SiC襯底質量直接影響外延材料的質量,進而對SiC功率半導體器件的性能發揮具有決定性的作用。

高質量SiC襯底的獲得存在單晶制備和加工兩方面的難度:一方面SiC通常需要在高溫(》2000 ℃)的環境中生長[3],而且SiC存在250多種晶型,因此制備高質量單一晶型的成本和難度非常大;另一方面,SiC硬度與金剛石接近,單晶的加工難度和成本都很高。據測算,在SiC器件制造各環節中,襯底成本占總成本近50%。襯底尺寸越大,單位襯底可集成芯片數量越多,單位芯片成本越低。采用8英寸(1英寸=2.54 cm)襯底比6英寸可多切近90%的芯片,邊緣浪費降低7%,有利于進一步降低芯片的成本,因此大尺寸化是SiC產業鏈降本增效的主要路徑之一。

目前,6英寸襯底是SiC襯底市場上的主流產品,而8英寸襯底是SiC半導體產業發展的主要方向之一。在國際上,行業龍頭美國Wolfspeed Inc.(原 Cree)最早在2015年展示了8英寸SiC樣品,其他多家企業也陸續宣布研發出了8英寸SiC襯底,例如Coherent Corp.(原Ⅱ-Ⅵ Inc.)、Rohm semiconductor Co. Ltd.、STMicroelectronics等。Wolfspeed Inc.是目前唯一一家實現8英寸SiC襯底量產的企業,其位于紐約莫霍克谷的8英寸SiC襯底工廠已于2022年4月正式投產[4]。國內產業界和科研機構雖然起步稍晚,但也取得不錯的進展。2022年,多家單位公布了8英寸產品開發成功[5],這些單位有北京天科合達半導體股份有限公司、中國科學院物理研究所、山西爍科晶體有限公司、山東天岳先進材料科技有限公司、山東大學[6]等。

北京天科合達半導體股份有限公司(簡稱“天科合達”)成立于2006年,技術來源于中國科學院物理研究所科研項目及研究成果,是國內首家專業從事SiC單晶襯底研發和產業化的高新技術企業,十幾年來一直堅守SiC襯底細分領域,6英寸SiC襯底產品已實現批量銷售,得到了國內外知名半導體器件企業的廣泛認可。天科合達從2020年開始開展8英寸導電型SiC單晶襯底的研發工作,經過2年多艱苦卓絕的技術攻關,突破了8英寸晶體擴徑生長和晶片加工等關鍵技術難題,成功制備出高品質8英寸導電型SiC單晶襯底,并計劃在2023年實現小規模量產。

2.實 驗

2.1

晶體生長和襯底制備

本實驗通過以自主研發的由c軸偏向《11-20》方向4°的6英寸4H-SiC襯底作為籽晶和擴徑生長的起始點,采用物理氣相傳輸(physical vapor transport, PVT)法進行擴徑生長獲得直徑放大的SiC單晶。將放大的晶體進行切、磨、拋得到放大的新籽晶,通過多次迭代實現直徑放大到200 mm以上,從而獲得8英寸SiC晶體。生長過程中選擇籽晶的碳面作為生長表面,原料端溫度維持在2300 ℃左右,籽晶端的溫度控制在2100 ℃左右,壓力控制在4000 Pa以下,保持一定比例的氬氣和氮氣流動氣氛調控n型摻雜,從而實現導電型4H-SiC單晶的穩定生長。生長完成后的晶體進行滾圓、磨平面得到標準直徑的8英寸晶柱,以多線切割的方式進行切片,而后將切片進行研磨、拋光、清洗等一系列流程,制備出標準尺寸的8英寸導電型4H-SiC襯底。

2.2

性能表征

使用LabRamHR800型拉曼測試儀對8英寸4H-N-SiC襯底進行拉曼光譜檢測,激發光源為532 nm,光斑大小為直徑721 nm,共檢測357點位,對襯底的晶型進行表征;

使用Panalytical-X’Pert3 MRD XL型高分辨X射線衍射儀進行結晶質量檢測,采用單色源Cu Kα射線(λ=0.15406 nm),測試范圍為±0.02°,步長0.0001°, 積分時間0.1 s,檢測襯底上、下、左、中、右半徑中點處共5點位(004)衍射面的搖擺曲線,用以表征襯底的結晶質量;

使用光學顯微鏡檢測襯底的微管數量和分布位置,并計算出微管密度;

使用非接觸式電阻儀,參照SEMI-MF673中的方法Ⅱ[7],即非接觸渦流法測量襯底55點位的電阻率;

使用應力檢測儀對8英寸襯底的應力進行表征,該設備利用光在不同應力條件下傳播會產生相位差這一特性,通過觀察疊加偏振的光明暗來定性辨別應力大小和分布;

使用Tropel FlatMaster 200對8英寸襯底的面型進行測量,該設備利用分析樣品與設備參考平面反射光形成的干涉條紋來識別樣品的面型和厚度變化;

使用540 ℃熔融KOH對襯底進行20 min刻蝕,并采用全自動位錯掃描儀對其位錯分布及密度進行掃描和統計。

3.結果與討論

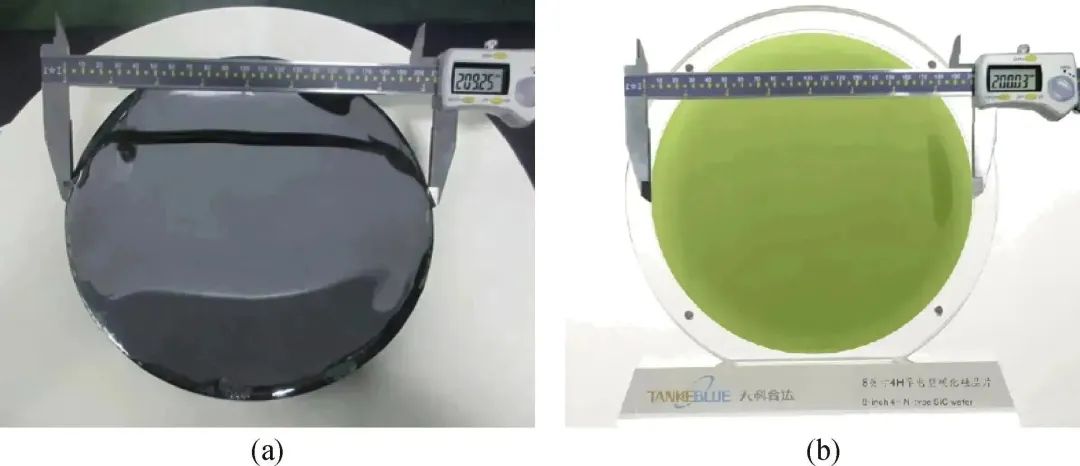

對于SiC晶體擴徑生長,溫場和流場決定了擴展邊緣結晶完整度和晶型單一性,在晶體邊緣處存在的SiC、石墨、氣態分子多種物質交織發生化學反應的驅動力與表面沉積、原子遷移、吸附-解吸附等過程之間的動力學關系,決定能否實現晶體擴徑生長。隨著SiC晶體尺寸的增大,溫場和流場的不均勻性更加明顯,擴徑生長難度也顯著增加。采用熱場模擬與工藝試驗相結合方法,開展設備關鍵結構設計、高匹配籽晶黏接、局部熱場設計優化改進,解決大尺寸晶體擴徑生長邊緣缺陷增殖和熱應力問題,實現低應力8英寸SiC單晶擴徑生長。PVT法生長的8英寸導電型SiC晶體如圖1所示,晶體直徑達到 209.25 mm。生長界面微凸,表面光亮平滑且無任何裂紋,表明生長過程結晶比較穩定。按標準加工流程制成直徑為200.03 mm的標準8英寸襯底,自然光下呈棕綠色,表面無明顯多晶、劃痕、崩邊等肉眼可見缺陷。

圖1天科合達8英寸SiC晶錠和晶片。(a)直徑達到209 mm的SiC晶錠;(b)標準8英寸SiC晶片

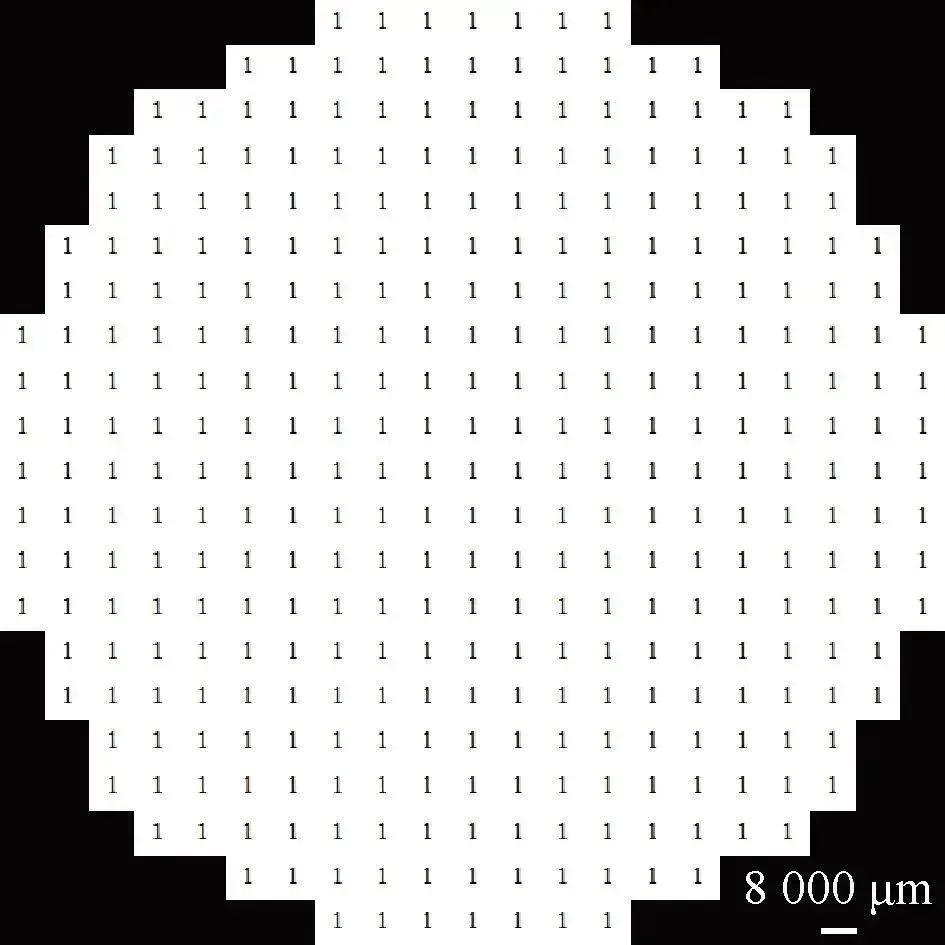

拉曼光譜對晶片357點位的測試結果如圖2所示。各測試點位均出現形貌相似的拉曼峰,且與聲子模以及簡約波矢和對稱性為204 cm-1(FTA,x=0.5,E2)的拉曼峰偏差不大于0.65 cm-1。與此同時,結果中未測得6H晶型對應的FTA模(150 cm-1),以及15R晶型對應的FTA模(174 cm-1)等高強度簡約波矢模[8]。由此可得8英寸SiC晶片的4H晶型占比為100%。

圖28英寸4H-SiC晶片拉曼光譜掃描圖(1為4H-SiC,2為6H-SiC,3為15R-SiC)

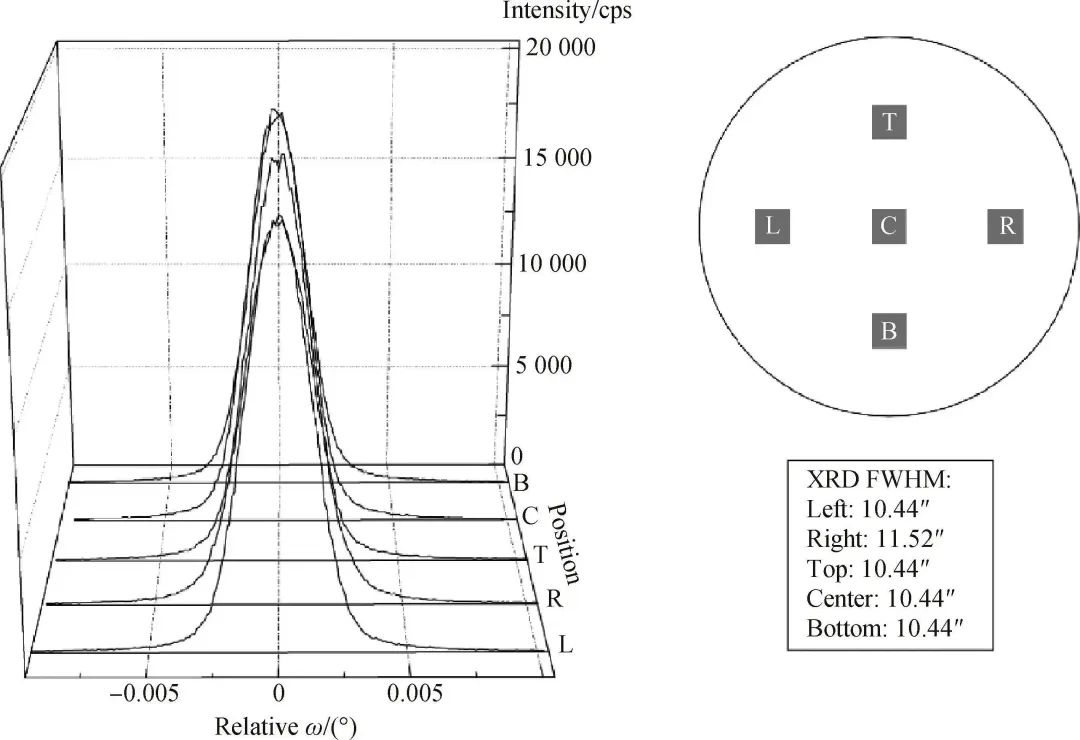

高分辨率X射線搖擺曲線測試結果如圖3所示,測試點位為襯底中心和上、下、左、右半徑的中心位置共5點。從圖中可以看出,各測試點位的(004)衍射峰均為單一峰,其對應的半峰全寬分布在10.44″至11.52″之間,表明8英寸4H-SiC襯底結晶質量良好,不存在多晶、小角晶界等影響結晶質量的缺陷。

圖38英寸SiC晶片(004)晶面高分辨X射線衍射圖譜

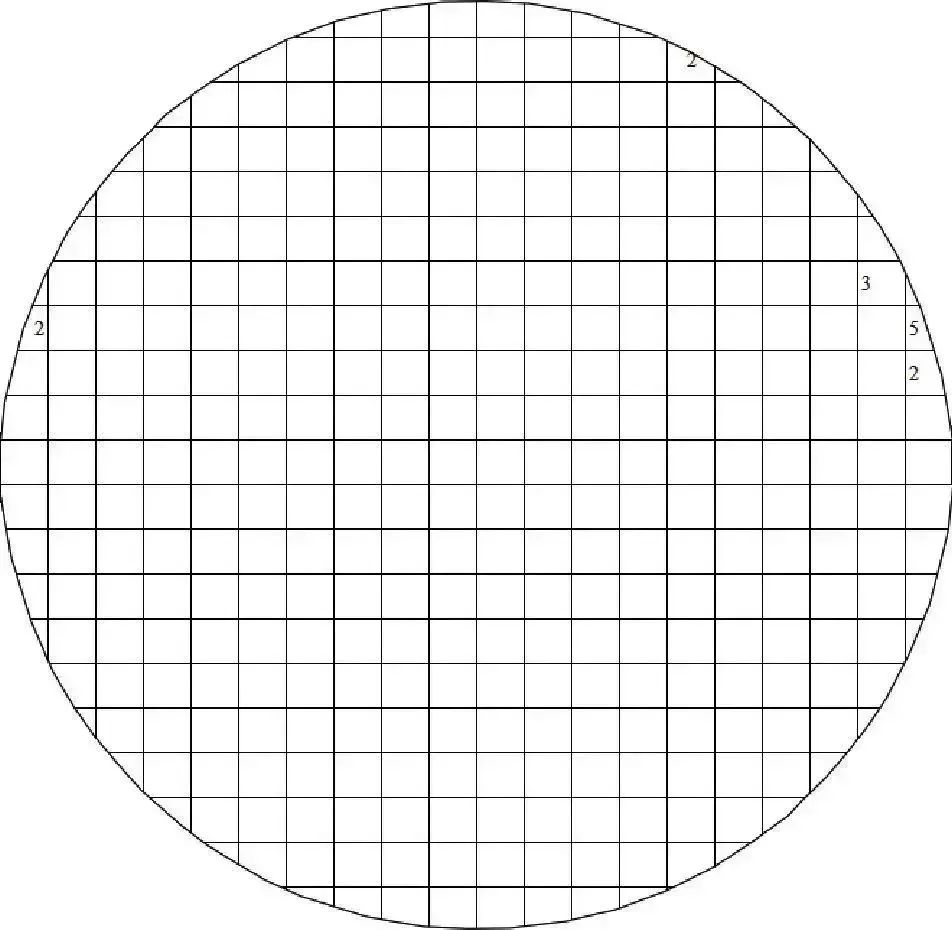

使用光學顯微鏡對8英寸襯底的微管密度進行全自動掃描,去除邊緣3 mm區域的微管進行統計后得出,該8英寸襯底的微管密度為0.04 cm-2。整片中共發現微管14個,且均分布于邊緣,如圖4所示。

圖48英寸SiC晶片微管分布

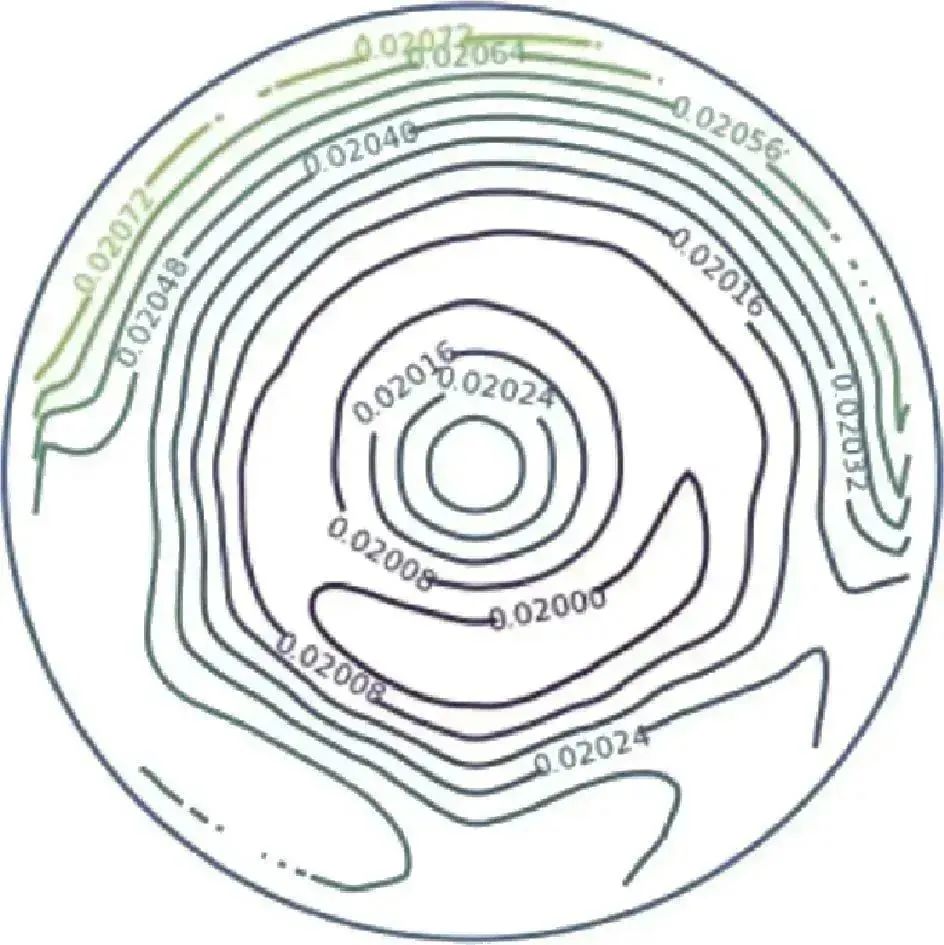

采用非接觸式渦流法測試8英寸SiC襯底電阻率,結果如圖5所示。結果顯示,8英寸襯底的平均電阻率為0.0203 Ω·cm,最大值為0.0208 Ω·cm,最小值為0.0199 Ω·cm,相對標準偏差為1.11%。

圖58英寸SiC晶片電阻率測試結果

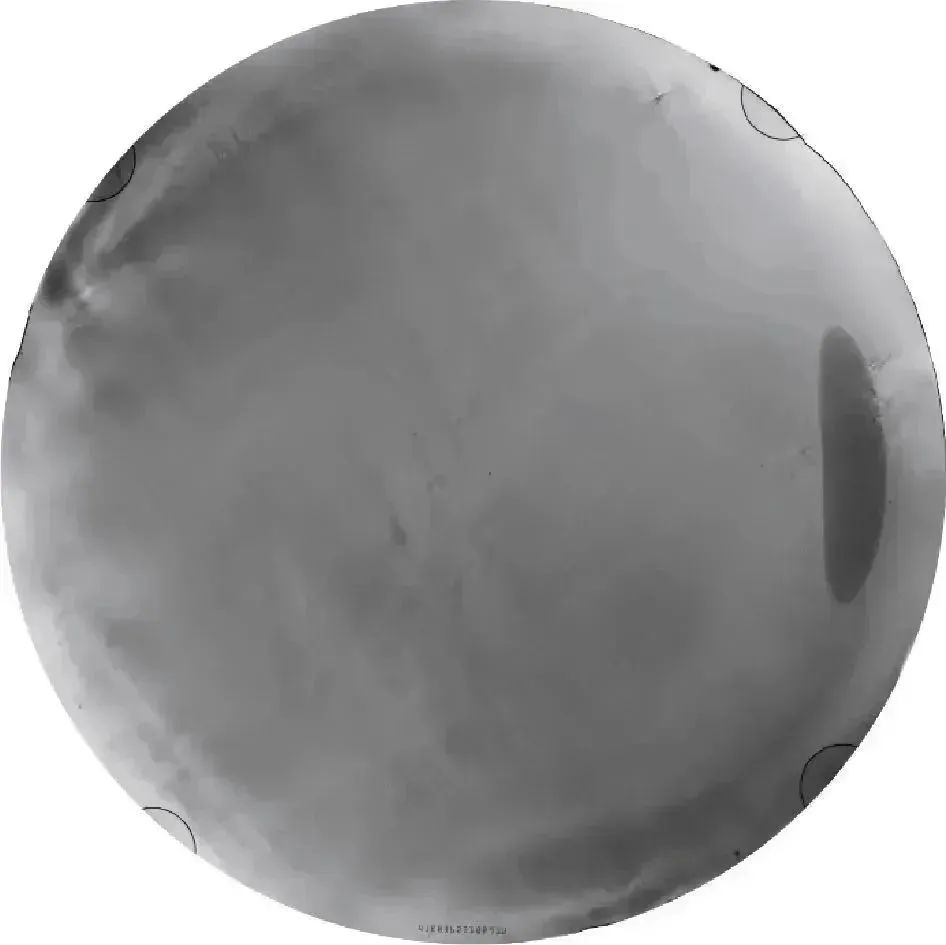

采用偏振光應力儀檢測的8英寸襯底應力分布,如圖6所示。一般地,測試結果中明暗波動較大的區域應力較大[9]。該8英寸SiC襯底整體應力分布均勻,除在小面位置外側以及襯底邊緣位置存在低強度應力區域外,大部分區域未見明顯的應力集中區域,表明晶體的結晶質量良好。

圖68英寸SiC晶片偏振光應力測試結果

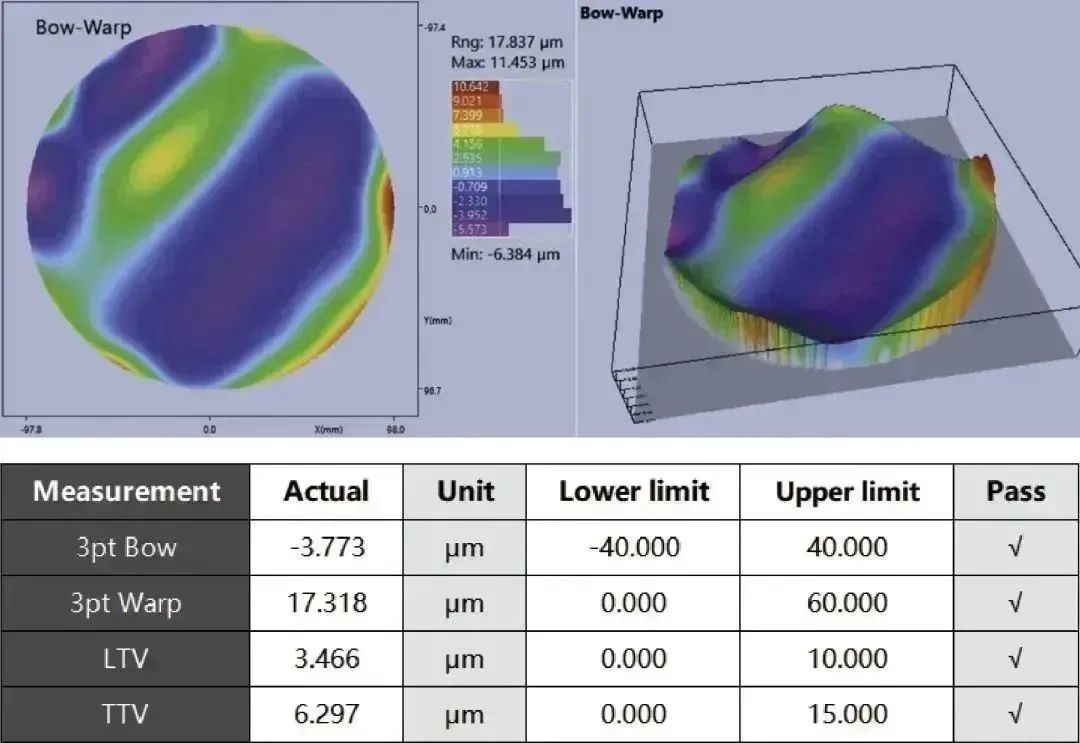

使用FM200測試的晶片面型結果如圖7所示。通過測量得出該8英寸晶片的3點彎曲度(Bow)為-3.773 μm,3點翹曲度(Warp)為17.318 μm。

圖78英寸SiC晶片平整度測試結果

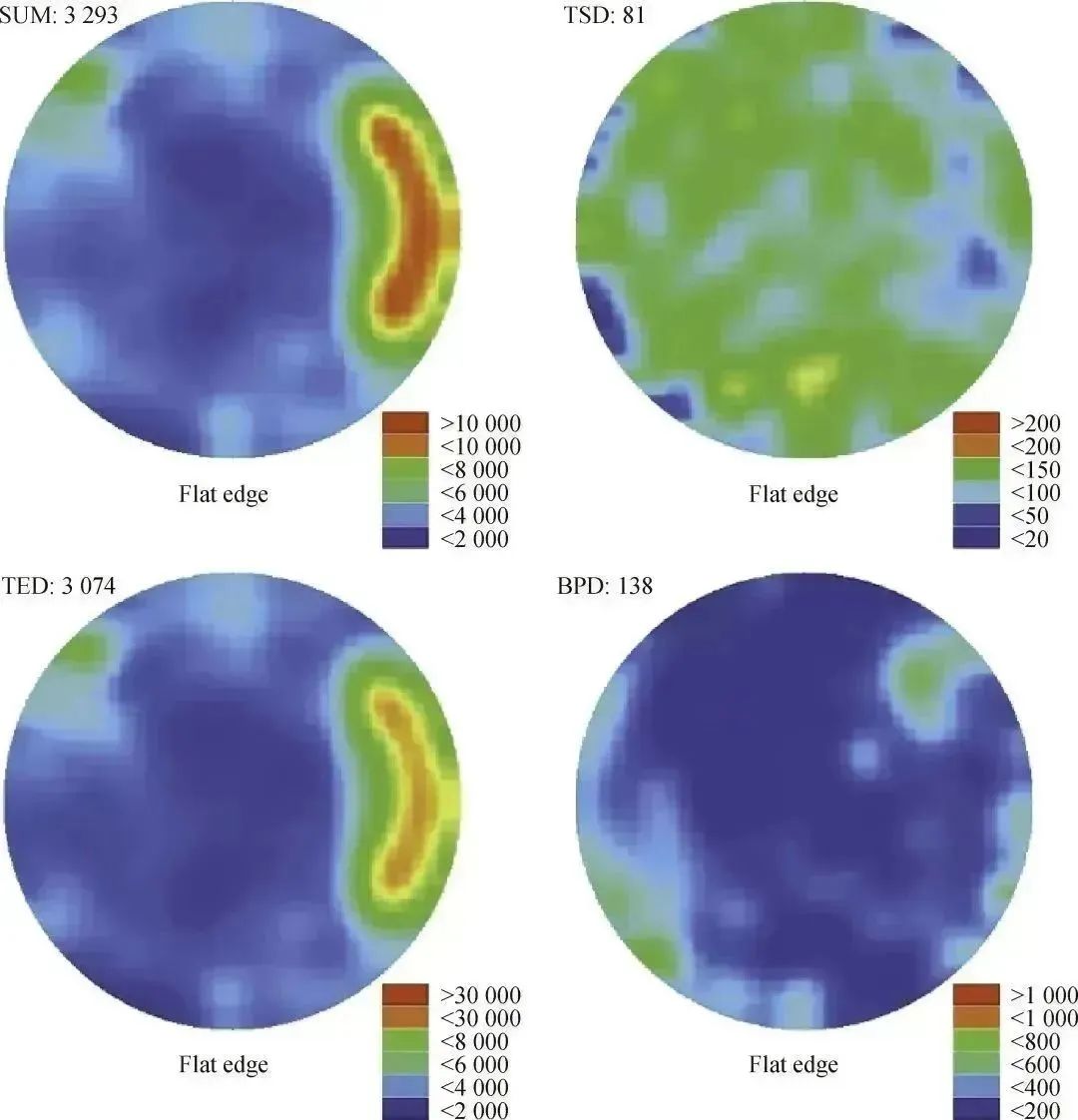

通過熔融KOH刻蝕,SiC襯底硅面表面的位錯位置被擇優腐蝕放大,即位錯腐蝕坑。使用自動位錯檢測儀對腐蝕坑的形貌進行識別和分類,并統計出位錯在襯底上的分布和位錯密度。結果顯示,該8英寸襯底的位錯腐蝕坑密度(etch pit density, EPD)為3293 cm-2,其中螺型位錯(threading screw dislocation, TSD)密度為81 cm-2,刃型位錯(threading edge dislocation, TED)密度為3074 cm-2,基平面位錯(basal plane dislocation, BPD)密度僅為138 cm-2。各類型位錯的分布如圖8所示。由于小面區域的生長習性與其他區域不同,導致位錯密度在此位置明顯高于其他區域,符合理論預期。

圖88英寸SiC晶片位錯分布圖

綜合上述結果,該SiC襯底的各項指標與當前6英寸SiC襯底的行業標準[10-11]相當,可滿足后續8英寸外延、器件等加工要求。

4.結 論

使用PVT法通過多次擴徑生長將SiC晶體直徑從150 mm擴大到209 mm,并通過多線切割、研磨、拋光等一系列加工工藝,制備出標準的8英寸襯底產品。8英寸4H-SiC襯底4H晶型比例為100%,5點X射線搖擺曲線半峰全寬分布在10.44″~11.52″,平均微管密度為0.04 cm-2,平均電阻率為0.0203 Ω·cm。襯底不存在明顯應力區,Warp值為17.318 μm,Bow值為-3.773 μm,總位錯密度為3293 cm-2,其中TSD密度為81 cm-2,BPD密度為138 cm-2,各項檢測指標均達到了行業先進水平。為滿足國內外客戶對于8英寸SiC襯底的迫切需求,天科合達公司預計2023實現小規模量產。

審核編輯 :李倩

-

SiC

+關注

關注

29文章

2804瀏覽量

62608 -

氮化鎵

+關注

關注

59文章

1628瀏覽量

116306

原文標題:天科合達談八英寸SiC

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

8英寸SiC投產進展加速,2025年上量

天域半導體8英寸SiC晶圓制備與外延應用

碳化硅襯底,進化到12英寸!

又一企業官宣已成功制備8英寸SiC晶圓

合盛新材料8英寸導電型4H-SiC襯底項目全線貫通

全球掀起8英寸SiC投資熱潮,半導體產業迎來新一輪技術升級

國內8英寸SiC工程片下線!降本節奏加速

韓國首座8英寸SiC晶圓廠開建

杭州士蘭與廈門半導體等聯手投資8英寸SiC功率器件項目

江蘇天科合達碳化硅晶片二期擴產項目預計6月投產

新質生產力賦能高質量發展,青禾晶元突破8英寸SiC鍵合襯底制備!

科友半導體與俄羅斯N公司開展“八英寸碳化硅完美籽晶”的項目合作

北京順義泰科天潤項目一期投資4億元,預計2028年達產

8英寸SiC襯底陣容加速發展 全球8英寸SiC晶圓廠將達11座

天科合達談八英寸SiC

天科合達談八英寸SiC

評論