作者:Austin Harney and Grzegorz Wawrzola

鎖相環(PLL)是現代通信系統的基本組成部分。PLL通常用于在無線電接收器或發射器中提供本振(LO)功能;它們還用于時鐘信號分配和降噪,并越來越多地用作高采樣率模數或數模轉換的時鐘源。

隨著PLL的噪聲性能逐代提高,電源噪聲的影響也越來越明顯,在某些情況下甚至會限制噪聲性能。

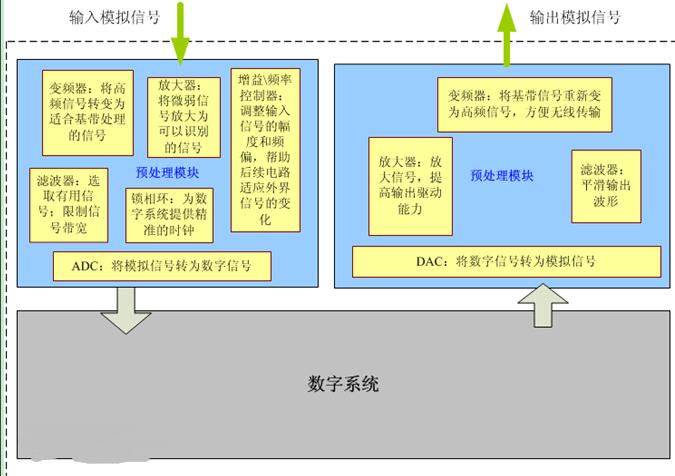

本文考慮圖1所示的基本PLL方案,并研究每個構建模塊的電源管理要求。

圖1.顯示各種電源管理要求的基本鎖相環。

在PLL中,反饋控制環路驅動壓控振蕩器(VCO),使振蕩器頻率(或相位)精確跟蹤施加參考頻率的倍數。許多很好的參考文獻,例如,貝斯特的鎖相環,1解釋PLL的數學分析;以及仿真工具,如ADI公司的ADIsimPLL?,有助于理解循環傳遞函數和計算。現在讓我們依次看一下PLL構建模塊。

VCO和VCO推動

壓控振蕩器將來自鑒相器的誤差電壓轉換為輸出頻率。它的“增益”定義為KVCO,通常以 MHz/V 為單位指定。壓控可變電容二極管(變容二極管)通常用于調節VCO中的頻率。VCO的增益通常大到足以提供足夠的頻率覆蓋,但又不會大到降低相位噪聲,因為任何變容二極管噪聲都會被放大KVCO并導致輸出相位噪聲。

多頻段集成VCO的出現,例如集成VCO的ADF4350頻率合成器中使用的VCO,消除了兩者之間的權衡KVCO和頻率覆蓋范圍,允許PLL設計人員使用包含多個中等增益VCO的IC,并通過智能頻段切換例程根據編程輸出頻率選擇合適的頻段。這種頻段劃分提供了寬闊的整體范圍和更低的噪聲。

除了從輸入電壓變化到輸出頻率變化(KVCO),電源變化會產生不需要的輸出頻率變化分量。VCO對電源變化的敏感性定義為VCO推動 (K推動),通常是通緝犯的一小部分KVCO.例如K推動通常為 5% 至 20%KVCO.因此,對于高增益VCO,推動效應變得更大,VCO電源的噪聲貢獻變得更加關鍵。

VCO 推動是通過向 VTUNE 引腳施加直流調諧電壓、改變電源電壓并測量頻率變化來測量的。推力圖是使用ADF4350 PLL的頻率變化與電壓變化之比,如表1所示。

表 1.ADF4350 VCO 推送測量

|

VCO 頻段 (兆赫) |

V調整 (五) |

f1(兆赫) 在 V 時VCO= 3 V |

f2(兆赫) 在 V 時VCO= 3.3 V |

K推動= Δf/δV (兆赫/伏) |

| 2200 | 2.5 | 2233.446 | 2233.061 | 1.28 |

| 3300 | 2.5 | 3331.112 | 3331.799 | 2.3 |

| 4400 | 2.5 | 4462.577 | 4464.242 | 5.55 |

參考文獻 2 中提到的另一種方法是將低頻方波直流耦合到電源中,同時觀察 VCO 頻譜兩側的頻移鍵控 (FSK) 調制峰值(圖 2)。峰值之間的頻率偏差除以方波幅度得出VCO推頻數。這可能是比靜態直流測試更準確的測量方法,因為它消除了與直流輸入電壓變化相關的任何熱效應。圖2顯示了ADF4350 VCO輸出在3.3 GHz時的頻譜分析儀圖,標稱3.3 V電源施加10 kHz、0.6 V p-p方波。對于 1.62 MHz/0.6 V 或 2.7 MHz/V 的推動數,由此產生的偏差為 3326.51 MHz – 3324.89 MHz = 1.62 MHz。相比之下,表1給出了2.3 MHz/V的靜態測量值。

圖2.ADF4350 VCO對10 kHz、0.6 V p-p方波電源調制的響應的頻譜分析儀圖。

在PLL系統中,更高的VCO推力意味著VCO電源噪聲的倍增更大。需要低噪聲電源,以盡量減少對VCO相位噪聲的影響。

基準電壓源3和基準4提供了不同低壓差穩壓器(LDO)如何影響PLL相位噪聲的良好示例。例如,比較了ADP3334和ADP150 LDO為ADF4350供電的情況。ADP3334穩壓器的集成均方根噪聲為27 μV(超過四十年頻程,從10 Hz到100 kHz)。相比之下,ADF4350評估板上使用的LDOADP150為9 μV。測量的PLL相位噪聲頻譜密度的差異如圖3所示。測量是在4.4 GHz VCO頻率下進行的,其中VCO推力最大(表1),因此這是最壞情況的結果。ADP150穩壓器噪聲足夠低,因此其貢獻不會顯著增加VCO噪聲,使用兩節(可能為“無噪聲”)AA電池重復測量證實了這一點。

圖3.ADF4350在4.4 GHz時的相位噪聲比較,當使用ADP3334和ADP150 LDO和AA電池供電時。

圖3強調了低噪聲電源對ADF4350的重要性,但如何指定電源或LDO的噪聲要求?

以類似于VCO噪聲的方式,LDO的相位噪聲貢獻可以建模為加性元件Φ線性分布器(t),如圖4所示。重復使用VCO過量相位表達式可產生:

或者,在頻域中

哪里vLDO(f)是LDO的電壓噪聲頻譜密度。

1 Hz帶寬內的單邊帶功率譜密度SΦ(f)由下式給出

以dB表示,計算電源噪聲引起的相位噪聲貢獻的公式為:

|

(1) |

其中 L(線性分布器)是失調f處穩壓器對VCO相位噪聲(dBc/Hz)的噪聲貢獻;K推動是以 Hz/V 為單位的 VCO 推動數字;和 v線性分布器(f) 是給定頻率偏移下的噪聲頻譜密度,單位為 V/√Hz。

圖4.小信號加性VCO電源噪聲模型

在自由運行的VCO中,總噪聲是和方根(rss)L線性分布器和VCO噪音。因此,以dB表示:

例如,考慮一個推頻數為10 MHz/V、在100 kHz偏移時測量相位噪聲為–116 dBc/Hz的VCO:為了不降低100 kHz時的VCO噪聲性能,電源所需的噪聲頻譜密度是多少?電源噪聲和VCO噪聲相加為和方根,因此電源噪聲應至少比VCO噪聲小6 dB,以盡量減少其貢獻。因此L線性分布器應小于 –122 dBc/Hz。使用公式 1,

求解vLDO(f),

vLDO(f),= 11.2 nV/√Hz,100kHz 偏移

給定失調下的LDO噪聲頻譜密度通常可以從LDO數據手冊的典型性能曲線中讀取。

當VCO連接到負反饋PLL時,LDO噪聲,L線性分布器,由PLL環路濾波器進行高通濾波,其方式與VCO噪聲類似。因此,上述公式僅適用于大于PLL環路帶寬的頻率偏移。在PLL的環路帶寬內,PLL可以成功跟蹤和濾除LDO噪聲,從而降低其貢獻。

LDO濾波

為了改善LDO噪聲,通常有兩種選擇:使用噪聲較小的LDO或對LDO輸出進行后置濾波。當無濾波器的噪聲要求超出經濟實惠的LDO的能力時,濾波選項可能是一個不錯的選擇。一個簡單的LC π濾波器通常足以將帶外LDO噪聲降低20 dB(圖5)。

圖5.LC π濾波器可衰減LDO噪聲。

在選擇組件時需要小心。典型的電感器在微亨利范圍內(帶有鐵氧體磁芯),因此有必要考慮其飽和電流 (我坐),在電感數據手冊中指定為電感下降10%時的直流電流水平。VCO消耗的電流應小于我坐.有效串聯電阻(ESR)也是一個問題,因為這會導致濾光片上的IR壓降。對于消耗300 mA DC的微波VCO,需要ESR小于0.33 Ω的電感才能產生小于100 mV的IR壓降。還需要低但非零的ESR,以抑制濾波器響應并提高LDO穩定性。選擇寄生ESR非常低的電容器并為此添加專用串聯電阻器是可行的。這 都 可以 使用 NI Multisim 等 可 下載 的 組 件 評估 器 在 SPICE 中 輕松 仿真?.

電荷泵和濾波器

電荷泵將鑒相器誤差電壓轉換為電流脈沖,電流脈沖由PLL環路濾波器進行積分和平滑處理。電荷泵通常可以在比其電源電壓(VP)低0.5 V的電壓下工作。例如,如果最大電荷泵電源為5.5 V,則電荷泵只能在高達5 V的輸出電壓下工作。如果VCO需要更高的調諧電壓,通常需要有源濾波器。實用信息和實際PLL的參考設計可在電路筆記CN0174中找到。5以及處理高壓的方法在“使用高壓VCO設計高性能鎖相環”中討論。6出現在《模擬對話》第 43 卷第 4 期(2009 年)中。有源濾波器的替代方案是使用帶電荷泵的PLL,例如ADF4150HV。ADF4150HV可以在高達30 V的電荷泵電壓下工作,因此在許多情況下無需使用有源濾波器。

電荷泵吸收的低電流使得使用升壓轉換器從較低的電源電壓產生高電荷泵電壓看起來很有吸引力,但與這種類型的DC-DC轉換器相關的開關頻率紋波可能會在VCO的輸出端產生不需要的雜散音。高PLL雜散可能導致發射器發射模板測試失敗,或降低接收器系統中的靈敏度和帶外阻塞。為了幫助指導轉換器紋波的規格,使用圖6所示的測量設置,對各種PLL環路帶寬進行了全面的電源抑制與頻率的關系圖。

圖6.用于測量電荷泵電源抑制的設置。

17.4 mV (–22 dBm)的紋波信號交流耦合到電源電壓,并在整個頻率范圍內掃描。在每個頻率下測量雜散電平,并將PSR計算為–22 dBm輸入和雜散輸出電平之間的dB差。保留在原位的0.1 μF和1 nF電荷泵電源去耦電容對耦合信號進行了一定程度的衰減,因此發電機上的信號電平增加,直到在每個頻率點的引腳上直接測量17.4 mV。結果如圖 7 所示。

隨著PLL環路帶寬內頻率的增加,電源抑制最初會變得更糟。當頻率接近PLL環路帶寬時,紋波頻率以與參考噪聲類似的方式衰減,PSR得到改善。該圖顯示,需要具有更高開關頻率(理想情況下大于1 MHz)的升壓轉換器,以最大程度地減少開關雜散。此外,應盡可能將PLL環路帶寬降至最低。

ADP1613的開關速度為1.3 MHz,是合適的升壓轉換器的一個很好的例子。將PLL環路帶寬設置為10 kHz時,PSR可能約為90 dB;環路帶寬為80 kHz時,PSR為50 dB。從PLL雜散電平要求開始,可以反向確定升壓轉換器輸出所需的紋波電平。例如,如果PLL要求雜散小于–80 dBm,而PSR為50 dB,則電荷泵電源輸入端的紋波功率需要小于–30 dBm或20 mV p-p。如果將足夠的去耦電容放置在電荷泵電源引腳附近,則紋波濾波器可以輕松實現這些紋波電壓水平。例如,100 nF去耦電容在1.3 MHz時提供超過20 dB的紋波衰減。 應注意使用具有適當額定電壓的電容器;例如,如果升壓轉換器產生 18V 電源,請使用額定電壓為 20V 或更高的電容器。

圖7.ADF4150HV電荷泵電源抑制曲線圖

使用基于Excel的ADP161x 設計工具簡化了升壓轉換器和紋波濾波器的設計。圖8顯示了示出5 V輸入至20 V輸出設計的用戶輸入。為了最小化轉換器級輸出端的電壓紋波,選擇了噪聲濾波器選項,并將V降至最低外波紋場設置為最小值。高壓電荷泵消耗的電流最大值為2 mA,因此I外輸入 10 mA 以提供裕量。該設計使用ADF4150HV評估板進行了測試,使用20 kHz的PLL環路帶寬。從圖7可以看出,PSR可能約為70 dB。由于具有出色的PSR,即使省略了噪聲濾波器,這種設置在VCO輸出端也沒有明顯的開關雜散(< –110 dBm)。

圖8.ADP1613升壓轉換器Excel設計工具。

作為最后的實驗,將高壓電荷泵的PSR與有源濾波器的PSR進行了比較,有源濾波器是目前最常用于產生高VCO調諧電壓的拓撲結構。為了進行測量,將幅度為1 V p-p的交流信號注入電荷泵電源(VP),使用無源環路濾波器,如圖6中的測量設置所示。用有源濾波器代替等帶寬的無源濾波器重復相同的測量。使用的有源濾波器為CPA_PPFFBP1型,如ADIsimPLL(圖9)所述。

圖9.ADIsimPLL中CPA_PPFFBP1濾波器設計的屏幕視圖。

電荷泵和運算放大器電源引腳上的去耦相同,以提供公平的比較——10 μF、10 nF和10 pF電容并聯。測量結果如圖10所示:與有源濾波器相比,高壓電荷泵的開關雜散電平降低了40 dB至45 dB。高壓電荷泵的雜散電平有所改善,部分原因是有源濾波器的環路濾波器衰減較小,注入的紋波在第一極點之后,而無源濾波器則注入的紋波位于輸入端。

圖 10.有源環路濾波器的電源紋波電平與高壓無源濾波器的比較。

最后要注意的是:圖1所示的第三個電源軌——分壓器電源,AVDD/DVDD—與VCO和電荷泵電源相比,電源要求不那么嚴格,因為PLL的RF部分(AVDD)通常是雙極性ECL邏輯級,具有穩定的帶隙參考偏置電壓,因此相對不受電源影響。此外,就其性質而言,數字CMOS塊(DVDD) 更不受電源噪聲的影響。因此,建議選擇同時滿足該電源軌電壓和電流要求的中等性能LDO,并在所有電源引腳附近應用足夠的去耦;100 nF 并聯 10 pF 通常就足夠了。

結論

討論了主PLL模塊的電源管理要求,并推導出了VCO和電荷泵電源的規格。ADI公司為電源管理和PLL提供多種設計支持工具,包括基準電壓源電路和解決方案,以及ADIsimPLL和ADIsimPower等仿真工具。了解電源噪聲和紋波對PLL性能的影響后,設計人員可以回頭推導出電源管理模塊的規格,并以最佳性能實現PLL設計。

審核編輯:郭婷

-

鎖相環

+關注

關注

35文章

590瀏覽量

88050 -

振蕩器

+關注

關注

28文章

3873瀏覽量

139629 -

電源管理

+關注

關注

115文章

6218瀏覽量

145191 -

pll

+關注

關注

6文章

785瀏覽量

135467 -

無線電

+關注

關注

60文章

2154瀏覽量

117073

發布評論請先 登錄

相關推薦

什么是模擬集成電路?

視頻與影像解決方案指南

鎖相環原理

數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

什么是模擬集成電路_集成電路

鎖相環的電源管理設計

模擬集成電路的應用

鎖相環的電源管理設計

鎖相環的電源管理設計

評論