作者:Mike Curtin and Paul O'Brien

本系列的第一部分介紹了鎖相環(PLL),描述了基本架構和工作原理。它還包括一個在通信系統中使用PLL的示例。在本系列的第二部分中,詳細研究了相位噪聲、基準雜散和輸出泄漏等關鍵性能規格,并考慮了它們對系統性能的影響。在本系列的最后一部分中,我們將處理構成PLL頻率合成器的一些主要構建塊。我們還將比較整數 N 和小數 N 分數架構。該系列文章最后將總結目前市場上可用的VCO,并列出ADI公司頻率合成器系列。

鎖相環頻率合成器基本構建模塊

PLL頻率合成器可以從幾個基本構建模塊的角度來考慮。已經涉及,現在將更詳細地處理它們:

鑒頻鑒相器 參考

計數器 (R) 反饋計數器 (N)

鑒頻鑒相器

頻率合成器的核心是鑒相器或鑒頻鑒相器。在這里,將參考頻率信號與VCO輸出反饋的信號進行比較,產生的誤差信號用于驅動環路濾波器和VCO。在數字PLL(DPLL)中,鑒相器或鑒頻檢波器是一個邏輯元件。三種最常見的實現是:

專用或(EXOR)柵極

J-K觸發器數字

鑒頻鑒波器

這里,我們僅考慮PFD,即ADF4110和ADF4210頻率合成器系列中使用的元件,因為與EXOR門和J-K觸發器不同,當其處于解鎖狀態時,其輸出與兩個輸入之間的頻率差成正比。

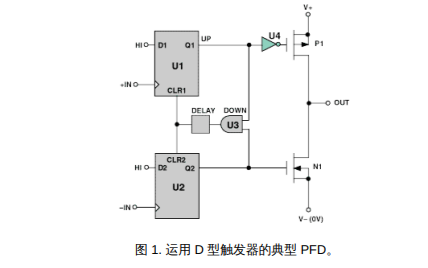

圖1顯示了PFD的一種實現,基本上由兩個D型觸發器組成。一個 Q 輸出使能一個正電流源;另一個Q輸出使能負電流源。假設在此設計中,D型觸發器是正邊沿觸發的,則狀態如下:

11 – 兩個輸出均為高電平,由 AND 門 (U3) 禁用,返回觸發器上的 CLR 引腳。

00 – P1和N1均關斷,輸出OUT基本上處于高阻抗狀態。

10–P1 打開,N1 關閉,輸出為 V+。

01–P1 關閉,N1 打開,輸出為 V–。

圖1.典型的PFD,使用D型觸發器。

現在考慮一下如果系統失鎖且+IN處的頻率遠高于-IN處的頻率,電路的行為,如圖2所示。

圖2.PFD 波形,頻率和相位鎖定。

由于+IN處的頻率遠高于–IN處的頻率,因此輸出大部分時間都處于高電平狀態。+IN上的第一個上升沿將輸出發送為高電平,并一直保持到–IN上出現第一個上升沿。在實際系統中,這意味著輸出以及VCO的輸入被驅動得更高,導致–IN的頻率增加。這正是所期望的。

如果 +IN 上的頻率遠低于 –IN,則會發生相反的效果。OUT 的輸出大部分時間都處于低狀態。這將具有在負方向上驅動VCO的效果,并再次使–IN處的頻率更接近+IN處的頻率,以接近鎖定條件。圖3顯示了輸入鎖定頻率并接近鎖相時的波形。

圖3.PFD波形,處于頻率鎖定狀態,但處于缺相鎖定狀態。

由于+IN是前導–IN,輸出是一系列正電流脈沖。這些脈沖將傾向于驅動VCO,使–IN信號與+IN上的信號相位對齊。

發生這種情況時,如果U3與U1和U2的CLR輸入之間沒有延遲元件,則輸出可能處于高阻抗模式,既不產生正電流脈沖,也不產生負電流脈沖。這不是一個好情況。VCO將漂移,直到產生明顯的相位誤差,并再次開始產生正或負電流脈沖。在相對較長的一段時間內,這種循環的影響是電荷泵的輸出被PFD輸入參考頻率的次諧波信號調制。由于這可能是低頻信號,因此環路濾波器不會衰減它,并且會在VCO輸出頻譜中產生非常明顯的雜散,這種現象稱為反沖效應。U3 輸出與 U1 和 U2 的 CLR 輸入之間的延遲元素可確保不會發生這種情況。使用延遲元件時,即使+IN和–IN完全相位對齊,電荷泵輸出端仍會產生電流脈沖。該延遲的持續時間等于在U3輸出端插入的延遲,稱為反沖脈沖寬度。

參考計數器

在經典的整數N分頻頻率合成器中,輸出頻率的分辨率由施加到鑒相器的參考頻率決定。因此,例如,如果需要 200 kHz 間隔(如 GSM 電話),則參考頻率必須為 200 kHz。然而,獲得穩定的 200kHz 頻率源并不容易。一個明智的方法是采用一個好的基于晶體的高頻源并將其劃分。例如,所需的頻率間隔可以通過從10 MHz頻率參考開始,然后將其除以50來實現。此方法如圖 4 中的圖表所示。

圖4.在PLL頻率合成器中使用基準計數器。

反饋計數器,N

N 計數器,也稱為 N 分頻器,是設置PLL中輸入和輸出頻率之間關系的可編程元件。多年來,N 計數器的復雜性一直在增長。除了一個簡單的N計數器外,它還發展到包括一個預分頻器,它可以具有雙模數。

當需要非常高的頻率輸出時,這種結構已經發展成為使用基本N分頻結構反饋到鑒相器所固有問題的解決方案。例如,假設 10 kHz 間隔需要 900 MHz 輸出。可以使用 10MHz 參考頻率,R 分頻器設置為 1000。然后,反饋中的 N 值需要為 90,000 量級。這意味著至少有一個17位計數器能夠處理900 MHz的輸入頻率。

為了處理此范圍,在可編程計數器之前加上一個固定的計數器元件是有意義的,以便將非常高的輸入頻率降低到標準CMOS的工作范圍。該計數器稱為預分頻器,如圖 5 所示。

圖5.基本預分頻器。

但是,使用標準預分頻器會帶來其他并發癥。系統分辨率現在已降低(F1×頁)。這個問題可以通過使用雙模預分頻器來解決(圖 6)。它具有標準預分頻器的優點,但不會損失任何系統分辨率。雙模預分頻器是一種計數器,其分頻比可以通過外部控制信號從一個值切換到另一個值。通過使用帶有A和B計數器的雙模預分頻器,仍然可以保持F的輸出分辨率1.但是,必須滿足以下條件:

圖6.雙模預分頻器

如果計數器未超時,則兩個計數器的輸出信號均為高電平。

當 B 計數器超時時,其輸出變為低電平,并立即將兩個計數器加載到其預設值。

加載到 B 計數器的值必須始終大于加載到 A 計數器的值。

假設 B 計數器剛剛超時,并且兩個計數器都已重新加載值 A 和 B。讓我們找到再次達到相同狀態所需的VCO周期數。

只要 A 計數器沒有超時,預分頻器就會除以 P+1。因此,每次預分頻器計數(P+1)VCO周期時,A和B計數器都將倒計時1。這意味著 A 計數器將在 ((P+1) × A) VCO 周期后超時。此時,預分頻器切換到 P 分頻。也可以說此時 B 計數器在超時之前仍有 (B-A) 周期要經過。這樣做需要多長時間:((B-A)×P)。系統現在回到了我們開始時的初始狀態。

實現此目的所需的 VCO 周期總數為:

使用雙模預分頻器時,重要的是要考慮N的最低值和最高值。我們真正想要的是可以以離散整數步長更改 N 的范圍。考慮表達式 N = A + BP。若要確保 N 的連續整數間距,A 必須在 0 到 (P–1) 范圍內。然后,每次 B 遞增時,都有足夠的分辨率來填充 BP 和 (B+1)P 之間的所有整數值。正如雙模預分頻器已經指出的那樣,B 必須大于或等于 A,雙模預分頻器才能工作。由此我們可以說,在能夠以離散整數步長遞增的同時,可能的最小除法比是:

N 的最大值由下式給出

在這種情況下一個.max和B.max僅由 A 和 B 計數器的大小決定。

現在來看ADF4111的實際示例。

假設預分頻器被編程為 32/33。

計數器:6位意味著A可以是26- 1 = 63 B 計數器:13 位表示

B 可以是 213- 1 = 8191

ADF4110系列

前幾節中討論的構建模塊均用于ADI公司新的N整數頻率合成器系列。ADF4110系列頻率合成器由單器件組成,ADF4210系列由雙通道版本組成。ADF4110的框圖如下所示。它包含上述參考計數器、雙模預分頻器、N 計數器和 PFD 模塊。

圖7.ADF4110系列框圖

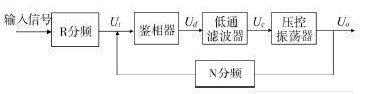

小數N分頻合成器

許多新興的無線通信系統需要本振(LO)中更快的開關和更低的相位噪聲。小數N分頻合成是實現這兩個目標的一種手段。

該技術最初是在 1970 年代初開發的。這項早期工作主要由惠普和拉卡爾完成。該技術最初被稱為“digiphase”,但后來被普遍命名為分數N。

在標準頻率合成器中,RF信號只能被整數除以。這就需要使用相對較低的參考頻率(由系統通道間距決定),并導致反饋中的N值很高。這兩個事實對系統建立時間和系統相位噪聲都有重大影響。低參考頻率意味著較長的建立時間,而高N值意味著較大的相位噪聲。

如果反饋中可以發生分數除法,則可以使用更高的參考頻率并仍然實現通道間距。這個較低的分數也意味著較低的相位噪聲。

如果事實如此,可以通過交替除以兩個整數來實現在很長一段時間內除以分數(除以 2.5 可以通過連續除以 2 和 3 來實現)。

那么,如何除以 X 或 (X + 1)(假設小數在這兩個值之間)?好吧,可以允許數字的小數部分以參考頻率速率累積。

圖8.小數N分頻合成器。

圖9的示意圖顯示了圖8中描述的小數N分頻系統的時序。出于此示例的目的,我們假設分頻比為 4.6。

信號 F外顯示 FREF 執行 10 個周期期間的 46 個周期。在 FREF 生成其第一個周期期間,N 計數器需要除以 4.6。當然,這是不可能的。它除以 4。因此,在第一個周期中,計數器輸出中“缺少”0.6個脈沖。這是使用累加器在系統中記憶的。累加器使用與F寄存器相同的代碼。在每個參考周期開始時,累加器將F寄存器內容添加到其先前的累積值中。因此,從時間 0 開始,累加器將跟蹤“缺失”的脈沖分數。

在第二個參考周期中,N 計數器將再次除以 4。累加器現在將在第一個參考周期累積的 0.6 的基礎上增加 0.6。這在累加器中給出了 1.2 的值,但由于它只能存儲小于 1 的值,因此將生成溢出并將 0.2 保留為累加器內容。

溢流用于激活脈沖消除電路。因此,VCO產生的下一個脈沖從輸入端移開至N計數器。這種脈沖去除與除以 5 而不是 4 具有相同的效果。如圖所示,累加器在第 4、5、7、9 和 10 個周期再次溢出。因此,在一系列 10 個參考周期中,有 6 個溢出,產生總數為 (4 × 4) + (6 × 5) = 46。這正是我們想要的。

圖9.小數 N 分頻時序。

VCO制造商摘要

隨著無線通信的爆炸式增長,對合成器和VCO等產品的需求在過去五年中急劇增加。有趣的是,到目前為止,市場一直由兩組不同的制造商提供服務。下面列出了VCO領域的一些參與者。這個列表并不是包羅萬象的,而是讓讀者對一些主要參與者有所了解。

審核編輯:郭婷

-

鎖相環

+關注

關注

35文章

588瀏覽量

87809 -

頻率合成器

+關注

關注

5文章

220瀏覽量

32370 -

pll

+關注

關注

6文章

777瀏覽量

135203 -

計數器

+關注

關注

32文章

2256瀏覽量

94700 -

觸發器

+關注

關注

14文章

2000瀏覽量

61215

發布評論請先 登錄

相關推薦

如何利用FPGA設計PLL頻率合成器?

DDS PLL短波頻率合成器設計

基于DDS芯片和集成鎖相芯片構成的寬頻合成器設計

基于DDS驅動PLL結構的寬帶頻率合成器的設計與實現

基于FPGA與PLL頻率合成技術設計的整數/半整數頻率合成器

構成PLL頻率合成器的構建模塊研究

構成PLL頻率合成器的構建模塊研究

評論